а сх с о

Изобретение относится к вычислительной технике и может быть использовано в процессорах быстродействующих ЭВМ.

Цель изобретения - упрощение устройства.

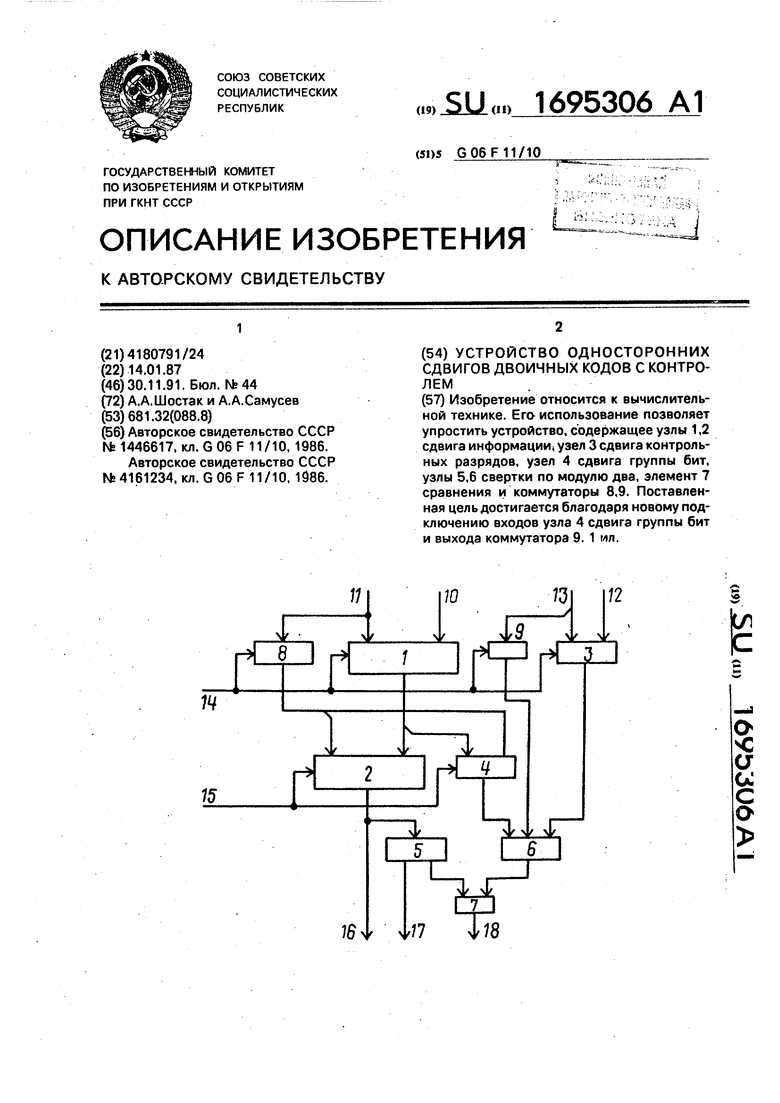

На чертеже приведена блок-схема устройства.

Устройство содержит первый 1 и второй

2узлы сдвига информации, узел 3 сдвига контрольных разрядов, узел 4 сдвига группы бит, первый 5 и второй б узлы свертки по модулю два, элемент 7 сравнения, первый 8 и второй 9 коммутаторы, первые 10 и вторые

11информационные входы, первые 12 и вторые 13 входы контрольных разрядов, первые 14 и вторые 15 управляющие входы, информационные выходы 16, выходы 17 контрольных разрядов и выход 18 ошибки.

В узле 1 обеспечивается сдвиг двоичного кода, установленного на входе 10, в одну сторону (например, вправо) на количество бит, кратное величине К 2J, j 1,2,3,..., а через вход 11 осуществляется вдвигание в освобождаемые разряды (слева) соответствующего количества групп битов (по К битое в каждой группе) кода, установленного на ()-разрядном входе 11, где N - разрядность входа 10 (N 21. i 2,3N К).

Количество групп по К битов задается путем установки на входе 14 соответствующего кода, значение которого может быть

Л |

равным М 0,1,2 ЬгЗ. где XJ - ближайшее целое число меньше X. При этом а узле 1 осуществляется сдвиг кодов вправо (с описанным вдвиганием) на количество соответственно 0,К,2К К битов.

В узле 2 осуществляется сдвиг (вправо) кода с выходов узла 1 с вдвиганием в освобождаемые разряды (слева) битов кода с первых (К-1) выходов коммутатора 8 на количество битов, равное т 0,1,2,...,К-1. При этом сдвинутый и вдвинутый коды формируются на выходе 16. Код величины сдвига находится в пределах 0 S т Ј К-1, т.е. не используется последний относительно направления сдвига разряд выхода коммутатора 8, количество разрядов которого равно К.

Узел 3 функционирует так же, как и узел 2, но с тем отличием, что разрядность входа

N

12и выхода узла 3 равна -гг + 1- Разрядность второго информационного входа узла

3равна -у (без последнего со стороны на1ч

правления сдвига разряда входа 13, разрядность которого равна JVH-1).

В описанных случаях использования значений кодов и количества разрядов, равных (VJ, означает, что при равенстве у целому числу (т.е. при делении N на К без остатка) hr -гг - 1 в то время, как количество групп разрядов входов 10 и 11 равно

N

тг- Количество разрядов в каждой группе к

равно К.

В случае, если -гг- дробное число, количество групп разрядов входов 10 и 11 равно

h( + Ри этом в ФУппе разрядов входа 10, которая является последней со стороны направления сдвига, количесто разрядов

равно N - hr К. В соответствующей групК

пе разрядов входа 11 количество разрядов равно N -1 -ф К.

Узел 4 функционирует так же, как и узел 2, но с тем отличием, что разрядность его первого и второго входов равна соответственно К и К-1.

Коммутатор 8 предназначен для передачи на выход сигналов битов первой отно- сительно направления сдвига не вдвинутой группы битов кода с входа 11.

Коммутатор 9 предназначен для передачи на выход сигнала четности (с входа 13) группы битов (кода, установленного на пер- вом входе узла 4), сигналы которой передаются на выход коммутатора 8.

Так, например, если пронумеровать

группы битов кодов на входах 10 и 11 (и,

следовательно, группы разрядов входов 10,

11) в соответствии с направлением сдвига

(например, вправо) цифрами 0,1,2Ьт, то

при задании на входе 14 кода со значением, равным 3, группы битов кода на входе 11с

номерами 0,1,2 вдвинуты1 в сдвинутый код на выходе узла 1, а сигналы группы битов с номером 3 с помощью коммутатора 8 переданы на его выход. При этом при группе, например, из четырех битов а, б, в, г

на вторые входы узла 2 переданы сигналы битов, кроме последнего а (относительно направления сдвига) бита, т.е. переданы сигналы битов б, в, г. При этом сигналы

(-;г$-й группы битов передаются в первые к

относительно направления сдвига разряды выхода коммутатора 8. Например, если количество битов fly )й группы битов равно трем, т.е. имеются разряды б, в, г, а

количество разрядов выхода коммутатора 8 равно четырем, то на его выход передаются сигналы битов по схеме 0, б, в, г (т.е. в последних разрядах выхода коммутатора 8, которые являются избыточными, формиру- ются логические нули).

Устройство работает следующим образом.

В исходном состоянии на входах 10 и 11 устройства устанавливаются соответствен- но сдвигаемый и вдвигаемый коды. На входах 12 и 13 устанавливаются значения контрольных битов, равные значениям сигналов сверток по модулю два групп по 1C битов кодов, установленных на входах соот- ветственно 10 и 11 устройства. Например, при установке на входе 10 N 16-разрядного кода 1011000100001110, а на входе 11 - (М-1}-15-разрядного кода 111001100000001 на входе 12 устанавливаются значения сиг- налов сверток по модулю два групп, например, по битов 1011, 0001, 0000, 1110 кода, установленного на входе 10, соответственно 1,1,0,1, а на входе 13 - значения сигналов свертки по модулю два групп би- тов 111, 0011, 0000, 0001 кода, установленного на выходе 11 равна соответственно 1,0,0,1.

Для выполнения сдвига на входе 14 устанавливается двоичный код (М) величины сдвига, кратной значению , например (10)2, а на входе 15 - двоичный код m величины сдвига в пределах 0 m К-1, равной, например .

В результате на выходе узла 1 формиру- ется сдвинутый на битов (например, вправо) код равный 0000000110110001 и сформированный в результате сдвига (вправо) на М«К 2-4 8 битов с вдвиганием в N-M К 16-8 8 освобождаемых разрядов соот- ветсвтующей (правой) части кода с входа 11.

На выходе коммутатора 8 формируется код 0011 в результате передачи сигналов М+1 2+1 3-ей группы (при отсчете со стороны направления сдвига, начиная с первой крайней группы) битов кода с входа 11. На втором входе узла 2 устанавливается код 011. На втором входе узла 4 устанавливается (К-1)-разрядный код К-1 первых битов (М+1)-й группы (при отсчете со стороны направления сдвига начиная с первой крайней группы) битов кода с входа 10, переданных на К-1 первых разрядов выхода узла 1, равный 001.

На выходе узла 3 формируется код 0111, образованный в результате сдвига кода 1101 на входе 12 и сдвигания соответствующей части кода 001 с входа 13.

На выходе 16 формируется к од 1100000001101100 в результате сдвига в узле 2 кода, установленного на первом входе узла 2, и вдвигания соответствующей части кода с второго входа узла 2. На выходе узла 4 формируется код 0100 в результате сдвига на разряда (вправо) кода, установленного на первом входе узла 4, и вдвигания соответствующей части кода со второго входа узла 4. Код на выходе узла 4 представляется совокупностью невдвинутых битов последней (М+1)-й вдвигаемой группы битов кода, устанозленного на входе 11, и выдвинутых битов последней (М+1)-й выдвигаемой группы битов кода, установленного на входе 10.

На выход коммутатора 9 и на первый (со стороны направления сдвига) разряд выхода узла 3 передаются сигналы четности указанных групп бит, свертка по модулю два которых и сигналов кода на выходе узла 4 характеризует значение четности совокупности вдвинутых и оставшихся бит указанных групп бит на выходе 16. Свертка же всех сигналов на входах узла 6 характеризует сигнал четности всего кода на выходе 16.

В результате свертки по модулю два в узле 6 всех сигналов, значения которых равны соответственно 0100,0,0111, на его выходе формируется код О, который сравнивается с кодом сигнала четности сдвинутого кода на выходе 16, формируемом на втором выходе узла 5 и равного О. На выходе 18 устройства формируется сигнал отсутствия ошибки, например, со значением О. При наличии ошибки (неисправности) в устройстве сигналы на входах элемента 7 имеют разные значения и на выходе 18 формируется сигнал ошибки со значением 1.

На выходе 17 формируются значения сигналов четности для групп битов кода, сформированного на выходе 16, равные (при количестве битов в группе, равном восьми) 00.

Таким образом, обеспечивается полный контроль по модулю два при минимальных аппаратных затратах на контроль,

Формула изобретения Устройство односторонних сдвигов двоичных кодов с контролем, содержащее первый узел сдвига информации, первые информационные входы которого являются одноименными входами устройства, вторые информационные входы первого узла сдвига информации объединены с соответствующими информационными входами первого коммутатора и являются вторыми информационными входами устройства, узел сдвига контрольных разрядов, первые информационные входы которого являются первыми входами контрольных разрядов устройства,

вторые информационные входы узла сдвига контрольных разрядов объединены с соответствующими информационными входами второго коммутатора и являются вторыми входами контрольных разрядов устройства, управляющие входы коммутаторов, первого узла сдвига информации и узла сдвига контрольных разрядов соответственно объединены и являются первыми управляющими входами устройства, выходы первого узла сдвига информации и выходы первого - (К- 1)-го разрядов первого коммутатора (К - общее число разрядов выходов первого коммутатора) соединены соответственно с первыми и вторыми информационными вхо- дами второго узла сдвига информации, управляющие входы которого объединены с соответствующими управляющими входами узла сдвига группы бит и являются вторыми управляющими входами устройства, выхо- ды второго узла сдвига информации подключены к входам первого узла свертки по модулю два и являются информационными выходами устройства, первые выходы первого узла свертки по модулю два являются выходами контрольных разрядов устройства, выходы узла сдвига контрольных разрядов и узла сдвига группы бит соединены с первыми и вторыми входами второго узла свертки по модулю два, выходы узлов свертки по модулю два подключены к первому и второму входам элемента сравнения, отличающееся тем, что, с целью упрощения устройства, первые и вторые информационные входы узла сдвига группы бит подключены соответственно к выходам первого коммутатора и первому - (К-1)-му разрядам выходов первого узла сдвига информации, выходы второго коммутатора соединены с третьими входами второго узла свертки по модулю два, выход элемента сравнения является выходом ошибки устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для односторонних сдвигов двоичных кодов с контролем | 1986 |

|

SU1446617A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для контроля сдвигателя | 1989 |

|

SU1672456A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

Изобретение относится к вычислительной технике. Его использование позволяет упростить устройство, содержащее узлы 1,2 сдвига информации, узел 3 сдвига контрольных разрядов, узел 4 сдвига группы бит, узлы 5,6 свертки по модулю два, элемент 7 сравнения и коммутаторы 8,9. Поставленная цель достигается благодаря новому подключению входов узла 4 сдвига группы бит и выхода коммутатора 9. 1 ил.

| Устройство для односторонних сдвигов двоичных кодов с контролем | 1986 |

|

SU1446617A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР N24161234 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1987-01-14—Подача