ЈЬ sj

00 СЛ

со

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах передачи данных по информационным каналам для преобразователя параллельного кода в последовательный.

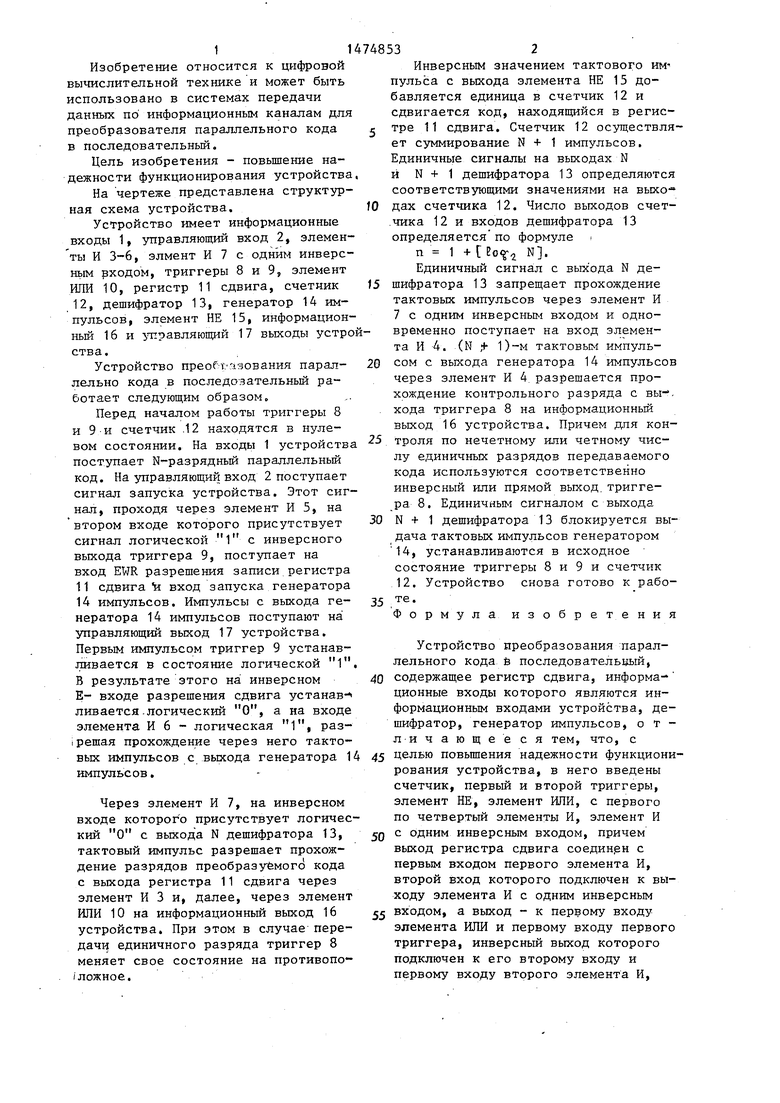

Цель изобретения - повышение надежности функционирования устройства. На чертеже представлена структурная схема устройства.

Устройство имеет информационные входы 1, управляющий вход 2, элемен- ты И 3-6, элмент И 7 с одним инверсным входом, триггеры 8 и 9, элемент ИЛИ 10, регистр 11 сдвига, счетник 12, дешифратор 13, генератор 14 импульсов, элемент НЕ 15, информационный 16 и управляющий 17 выходы устройства.

Устройство npeofгчэования парал- лельно кода в последовательный работает следующим образом.

Перед началом работы триггеры 8 и 9 и счетчик 12 находятся в нулевом состоянии. На входы 1 устройства поступает N-разрядный параллельный код. На управляющий вход 2 поступает сигнал запуска устройства. Этот сигнал, проходя через элемент И 5, на

втором входе которого присутствует

сигнал логической 1 с инверсного выхода триггера 9, поступает на вход EWR разрешения записи регистра 11 сдвигай вход запуска генератора 14 импульсов. Импульсы с выхода ге- нератора 14 импульсов поступают на управляющий выход 17 устройства. Первым импульсом триггер 9 устанавливается в состояние логической 1 В результате этого на инверсном Е- входе разрешения сдвига устанав- ливается логический О, а на входе элемента И 6 - логическая 1, раз- iрешая прохождение через него тактовых импульсов с выхода генератора 1 импульсов.

Через элемент И 7, на инверсном входе которого присутствует логический О с выхода N дешифратора 13, тактовый импульс разрешает прохождение разрядов преобразуемого кода с выхода регистра 11 сдвига через элемент И 3 и, далее, через элемент ИЛИ 10 на информационный выход 16 устройства. При этом в случае передачи единичного разряда триггер 8 меняет свое состояние на противоположное.

0

5 0 5

0 5

Инверсным значением тактового импульса с выхода элемента НЕ 15 добавляется единица в счетчик 12 и сдвигается код, находящийся в регистре 11 сдвига. Счетчик 12 осуществляет суммирование N + 1 импульсов. Единичные сигналы на выходах N и N + 1 дешифратора 13 определяются соответствующими значениями на выходах счетчика 12. Число выходов счетчика 12 и входов дешифратора 13 определяется по формуле

п 1 + Bo«g-2 N.

Единичный сигнал с выхода N дешифратора 13 запрещает прохождение тактовых импульсов через элемент И 7 с одним инверсным входом и одновременно поступает на вход элемента И 4. (N ,+ 1)-м тактовым импульсом с выхода генератора 14 импульсов через элемент И 4 разрешается прохождение контрольного разряда с вы-1 хода триггера 8 на информационный выход 16 устройства. Причем для контроля по нечетному или четному числу единичных разрядов передаваемого кода используются соответственно инверсный или прямой выход триггера 8. Единичным сигналом с выхода N + 1 дешифратора 13 блокируется выдача тактовых импульсов генератором 14, устанавливаются в исходное состояние триггеры 8 и 9 и счетчик 12. Устройство снова готово к работе. Формула изобретения

Устройство преобразования параллельного кода 6 последовательный, содержащее регистр сдвига, информационные входы которого являются информационным входами устройства, дешифратор, генератор импульсов, отличающееся тем, что, с целью повышения надежности функционирования устройства, в него введены счетчик, первый и второй триггеры, элемент НЕ, элемент ИЛИ, с первого по четвертый элементы И, элемент И с одним инверсным входом, причем выход регистра сдвига соединен с первым входом первого элемента И, второй вход которого подключен к выходу элемента И с одним инверсным входом, а выход - к первому входу элемента ИЛИ и первому входу первого триггера, инверсный выход которого подключен к его второму входу и первому входу второго элемента И,

выход.которого.соединен с вторым входом элемента ИЛИ, выход которого является информационным выходом устройства, управляющий вход которого соединен с первым входом третьего элемента И, выход которого соединен с первым и вторым управляющими входами регистра сдвига и входом запуска генератора импульсов, выход которого соединен с первыми входами второго триггера и четвертого элемента И, с вторым входом второго элемента И и является управляющим выходом устройства, инверсный и прямой выхо- 1ды второго триггера соединены с вто- ;рыми входами соответственно третьего

4853 4

и четвертого элементов И, выход последнего из которых подключен к прямому входу элемента И с одним инверсным входом и через элемент НЕ - к третьему управляющему входу.регистра сдвига и счетному входу счетчика, выходы которого соединены с соответствующими входами дешифратора, пер- - вый выход которого соединен с треть - им входом второго элемента И и инверсным входом элемента И с одним инверсным входом, а второй выход соединен с входами уставновки счетчика, первого и второго триггеров и входом -блокировки генератора импуль сов.

10

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки /ЭЛТ/ | 1989 |

|

SU1633387A1 |

| "Генератор чисел в кодах "золотой" пропорции" | 1989 |

|

SU1711143A1 |

Изобретение относится к цифровой вычислительной технике. Цель изобретения-повышение надежности устройства. С этой целью в устройство, содержащее регистр 11 сдвига и генератор 14 импульсов, введены элементы И 3-6, элемент И 7 с одним инверсным входом, элемент НЕ 15, элемент ИЛИ 10, два триггера 8,9, счетчик 12 и дешифратор 13. Устройство преобразует П-разрядный параллельный код в последовательный и добавляет контрольный разряд. Первые П тактовых импульсов с выхода генератора импульсов разрешают последовательное прохождение разрядов входного кода на информационный выход устройства. Одновременно в одном из триггеров формируется контрольный разряд, выдача которого производится (П+1)-м тактовым импульсом. Управление работой устройства осуществляется дешифратором и счетчиком. 1 ил.

| Преобразователь параллельного кода в последовательный | 1983 |

|

SU1119002A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь параллельного кода в последовательный | 1985 |

|

SU1275781A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-23—Публикация

1987-05-18—Подача