Изобретение относится к вычислительной технике и может быть иснользовано в матричных устройствах сдвига информации.

Цель изобретения - ювышение быстродействия и обеспечение возможности работы в двухтактном (обычном) и потакт- ном (ускоренном) режимах сдвига.

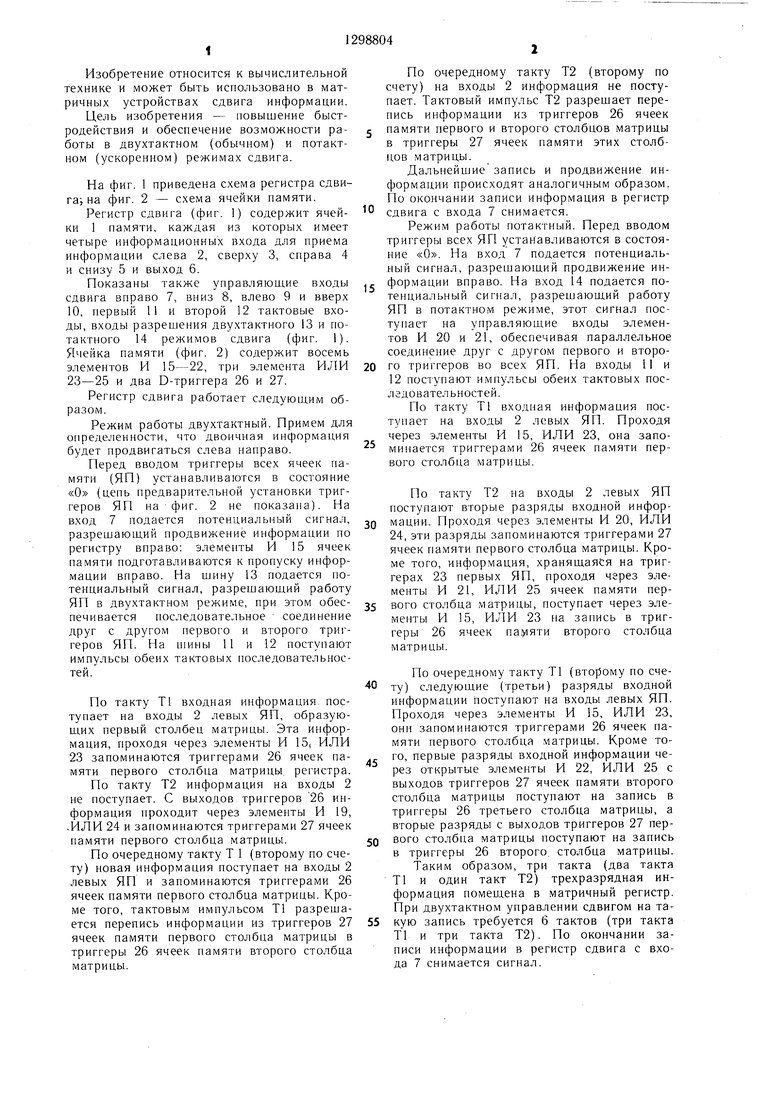

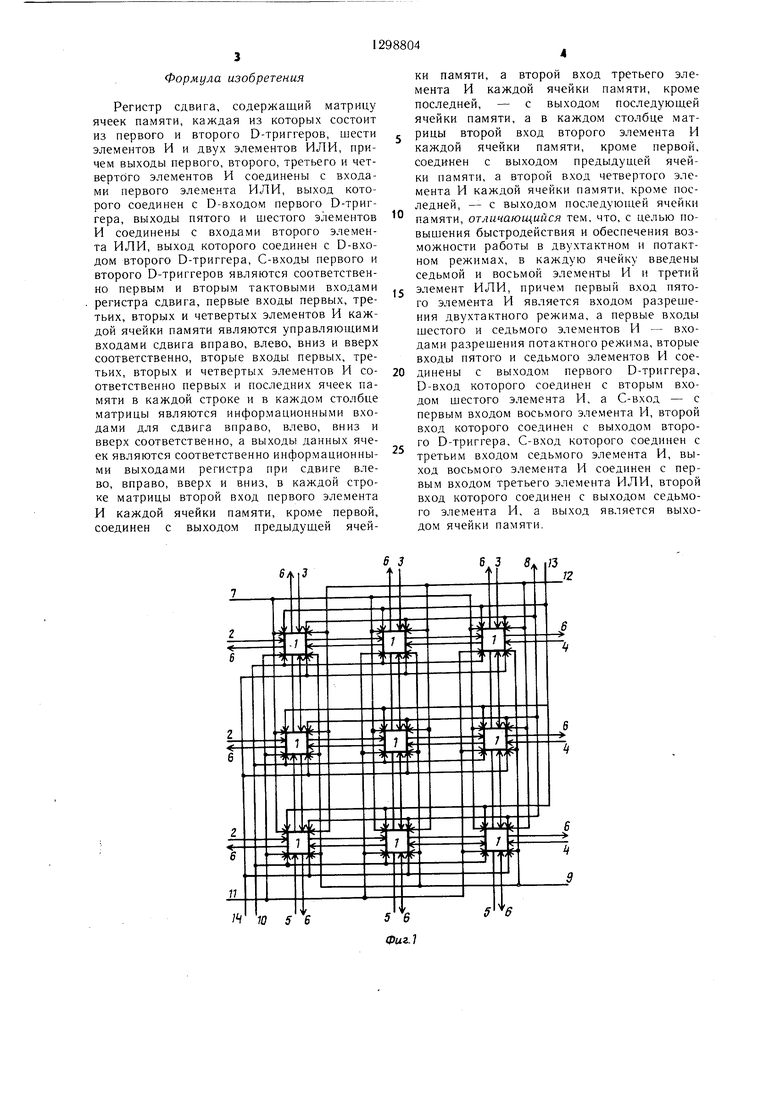

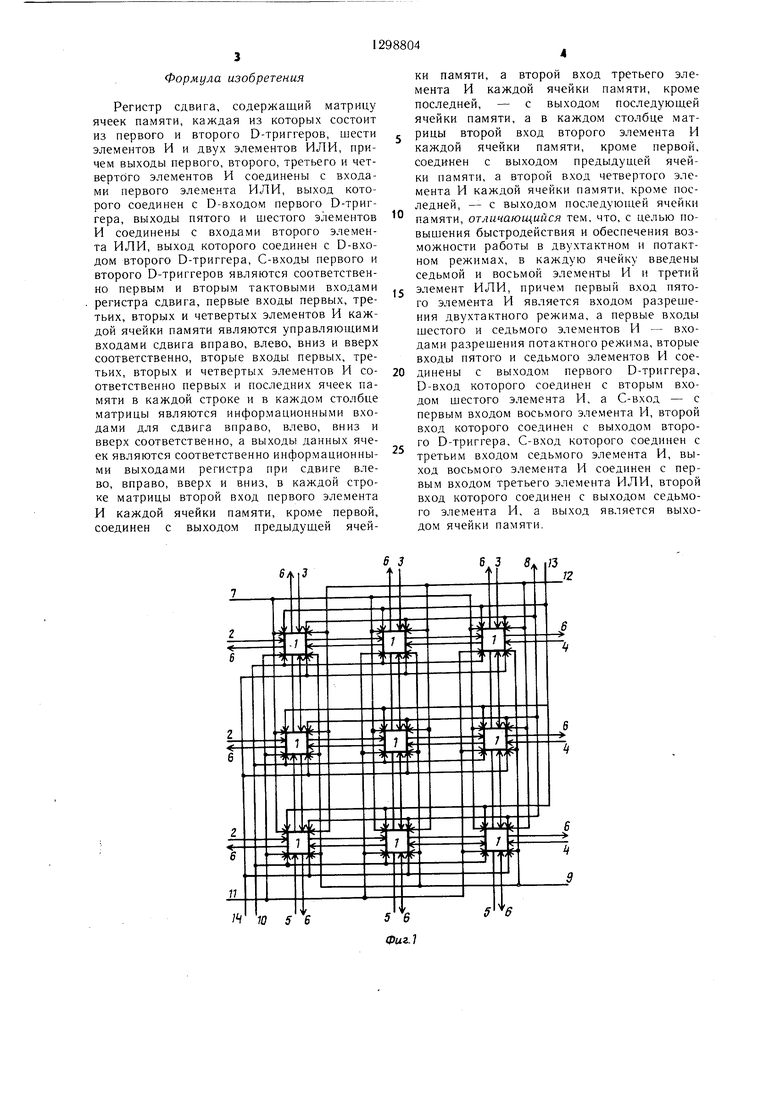

На фиг. 1 приведена схема регистра сдвига; на фиг. 2 - схема ячейки памяти.

Регистр сдвига (фиг. 1) содержит ячейки 1 памяти, каждая из которых имеет четыре информационных входа для приема информации слева 2, сверху 3, справа 4 и снизу 5 и выход 6.

Показаны также управляющие входы сдвига вправо 7, вниз 8, влево 9 и вверх 10, первый 11 и второй 12 тактовые входы, входы разрешения двухтактного 13 и по- тактного 14 режимов сдвига (фиг. 1). Ячейка памяти (фиг. 2) содержит восемь элементов И 15-22, три элемента ИЛИ 23-25 и два D-триггера 26 и 27.

Регистр сдвига работает следующим образом.

Режим работы двухтактный. Примем для определенности, что двоичная информация будет продвигаться слева направо.

Перед вводом триггеры всех ячеек памяти (ЯП) устанавливаются в состояние «О (цепь предварительной установки триггеров ЯП на фиг. 2 не показана). На вход 7 подается потенциальный сигнал, разрешающий продвижение информации по регистру вправо: элементы И 15 ячеек памяти подготавливаются к пропуску информации вправо. На шину 13 подается потенциальный сигнал, разрешающий работу ЯП в двухтактном режиме, при этом обеспечивается последовательное соединение друг с другом первого и второго триггеров ЯП. На П1ИНЫ 11 и 12 поступают импульсы обеих тактовых последовательностей.

По такту Т1 входная информация, поступает на входы 2 левых ЯП, образующих первый столбец матрицы. Эта информация, проходя через элементы И 15, ИЛИ 23 запоминаются триггерами 26 ячеек памяти первого столбца матрицы, регистра.

По такту Т2 информация на входы 2 не поступает. С выходов триггеров 26 информация проходит через элементы И 19, .ИЛИ 24 и запоминаются триггерами 27 ячеек памяти первого столбца матрицы.

По очередному такту Т 1 (второ.аду по счету) новая информация поступает на входы 2 левых ЯП и запоминаются триггерами 26 ячеек памяти первого столбца матрицы. Кроме того, тактовым импульсом Т1 разрешается перепись информации из триггеров 27 ячеек памяти первого столбца матрицы в триггеры 26 ячеек памяти второго столбца матрицы.

По очередному такту Т2 (второму по счету) на входы 2 информация не поступает. Тактовь й импульс Т2 разрещает перепись информации из триггеров 26 ячеек

памяти первого и второго столбцов .матрицы в триггеры 27 ячеек памяти этих столбцов матрицы.

Дальнейщие запись и продвижение информации происходят аналогичным образом. По окончании записи информация в регистр

сдвига с входа 7 снимается.

Режим работы потактный. Перед вводом триггеры всех ЯП устанавливаются в состояние «О. На вход 7 подается потенциальный сигнал, разрешающий продвижение информации вправо. На вход 14 подается потенциальный сигнал, разрешающий работу ЯП в потактном режиме, этот сигнал поступает на управляющие входы элементов И 20 и 21, обеспечивая параллельное соединение друг с другом первого и второго триггеров во всех ЯП. На входы 11 и 12 поступают импульсы обеих тактовых последовательностей.

По такту Т1 входная информация поступает на входы 2 левых ЯП. Проходя через элементы И 15, ИЛИ 23, она запоминается триггерами 26 ячеек па.мяти первого столбца матрицы.

По такту Т2 на входы 2 левых ЯП поступают вторые разряды входной информации. Проходя через элементы И 20, ИЛИ 24, эти разряды запоминаются триггерами 27 ячеек памяти первого столбца матрицы. Кроме того, информация, хранящаяся на триггерах 23 первых ЯП, проходя через элементы И 21, ИЛИ 25 ячеек памяти первого столбца матрицы, поступает через элементы И 15, ИЛИ 23 на запись в триггеры 26 ячеек па.1яти второго столбца матрицы.

По очередному такту Т1 (второму по сче- ту) следующие (третьи) разряды входной информации поступают на входы левых ЯП. Проходя через элементы И 15, ИЛИ 23, они запоминаются триггерами 26 ячеек памяти первого столбца матрицы. Кроме того, первые разряды входной информации через открытые элементы И 22, ИЛИ 25 с выходов триггеров 27 ячеек памяти второго столбца матрицы поступают на запись в триггеры 26 третьего столбца матрицы, а вторые разряды с выходов триггеров 27 пер- вого столбца матрицы поступают на запись в триггеры 26 второго, столбца матрицы. Таким образом, три такта (два такта Т1 и один такт Т2) трехразрядная информация помещена в матричный регистр. При двухтактном управлении сдвигом на та- кую запись требуется 6 тактов (три такта Т1 и три такта Т2). По окончании записи информации в регистр сдвига с входа 7 снимается сигнал.

Формула изобретения

Регистр сдвига, содержащий матрицу ячеек памяти, каждая из которых состоит из первого и второго D-триггеров, шести элементов И и двух элементов ИЛИ, причем выходы первого, второго, третьего и четвертого элементов И соединены с входами первого элемента ИЛИ, выход которого соединен с D-входом первого D-триг- гера, выходы пятого и шестого элементов И соединены с входами второго элемента ИЛИ, выход которого соединен с D-входом второго D-триггера, С-входы первого и второго D-триггеров являются соответственно первым и вторым тактовыми входами регистра сдвига, первые входы первых, третьих, вторых и четвертых элементов И каждой ячейки памяти являются управляющими входами сдвига вправо, влево, вниз и вверх соответственно, вторые входы первых, третьих, вторых и четвертых элементов И соответственно первых и последних ячеек памяти в каждой строке и в каждом столбце матрицы являются информационными входами для сдвига вправо, влево, вниз и вверх соответственно, а выходы данных ячеек являются соответственно информационными выходами регистра при сдвиге влево, вправо, вверх и вниз, в каждой строке матрицы второй вход первого элемента каждой ячейки памяти, кроме первой, оединен с выходом предыдущей ячей0

ки памяти, а второй вход третьего элемента И каждой ячейки памяти, кроме последней, - с выходом последующей ячейки памяти, а в каждом столбце матрицы второй вход второго элемента И каждой ячейки памяти, кроме первой, соединен с выходом предыдущей ячейки памяти, а второй вход четвертого элемента И каждой ячейки памяти, кроме последней, -- с выходом последующей ячейки памяти, отличающийся тем, что, с целью повышения быстродействия и обеспечения возможности работы в двухтактном и потакт- ном режимах, в каждую ячейку введены седьмой и восьмой элементы И и третий

5 элемент ИЛИ, причем первый вход пятого элемента И является входом разрешения двухтактного режима, а первые входы щестого и седьмого элементов И - входами разрешения потактного режима, вторые входы пятого и седьмого элементов И сое0 динены с выходом первого D-триггера, D-вход которого соединен с вторым входом щестого элемента И, а С-вход - с первым входом восьмого элемента И, второй вход которого соединен с выходом второго D-триггера, С-вход которого соединен с третьим входом седьмого элемента И, выход восьмого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И, а выход является выходом ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ЧИСЛОВЫХ МАТРИЦ | 1991 |

|

RU2022334C1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| Систолическая структура для вычисления логических функций | 1989 |

|

SU1654809A1 |

| Устройство для считывания изображений | 1986 |

|

SU1429142A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1464183A1 |

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

Изобретение относится к выч11слитсл1 - ной технике и может быть исполь.и)ва- но в матричных ycTpoiiCToax сдвига информации. Целью изобретения является ио- вышение быстродействия регистра и обеспечение возможности работы в двухтактном (обычном) и нотактном (ускоренном) режимах сдвига. Для достижения это цели в каждую ячейку намятн матрично1 о накопителя, состоящую из двух три1теров, шести элементов И и двух элементов ИДИ, введены еиле два элеме1гга И и один элемент ИДИ, позволяющие обеспечить нотакт- ный режим ввода и сдвига информации. 2 ил. ts5 ;о 00 00

Составитель А. Дерюгин

Редактор А. СабоТехред И. ВересКорректор О. Луговая

Заказ 751/54Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Авторское свидетельство СССР Nfo 754478, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Майоров С | |||

| А., Новиков Г | |||

| И | |||

| Принципы организации цифровых машин | |||

| Л.: Машиностроение, 1974, с | |||

| Ребристый каток | 1922 |

|

SU121A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-03-23—Публикация

1985-05-16—Подача