Изобретение относится к вычислительной технике и может быть исполь- зовано при йостроении управляющих систем, а также самостоятельных микропрограммных автоматов, операционные j указанные выходные состояния блоков

1 и 6 далее не проходят.

1 и 6 далее не проходят.

По исходному (нулевому) состоян регистра 2 микрокоманд на выходе 1 устройства на выходах регистра 2

части которых в два и более раз превосходят- адресные по разрядности.

Цель изобретения - повышение быстродействия .

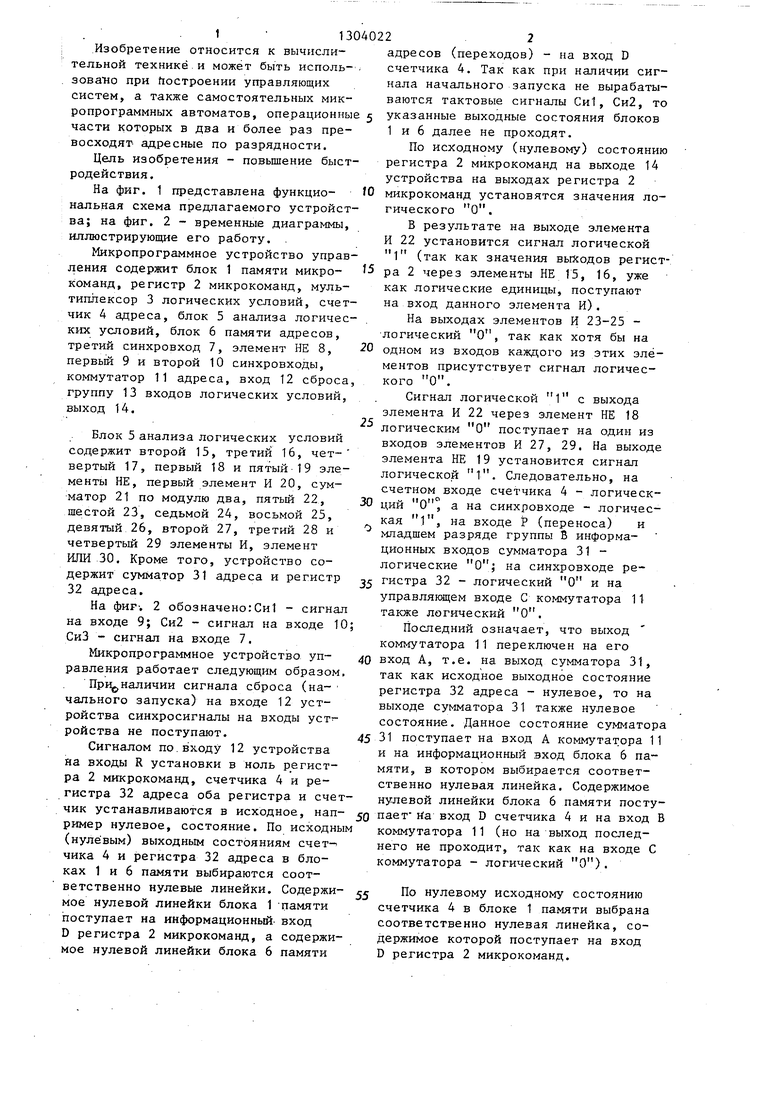

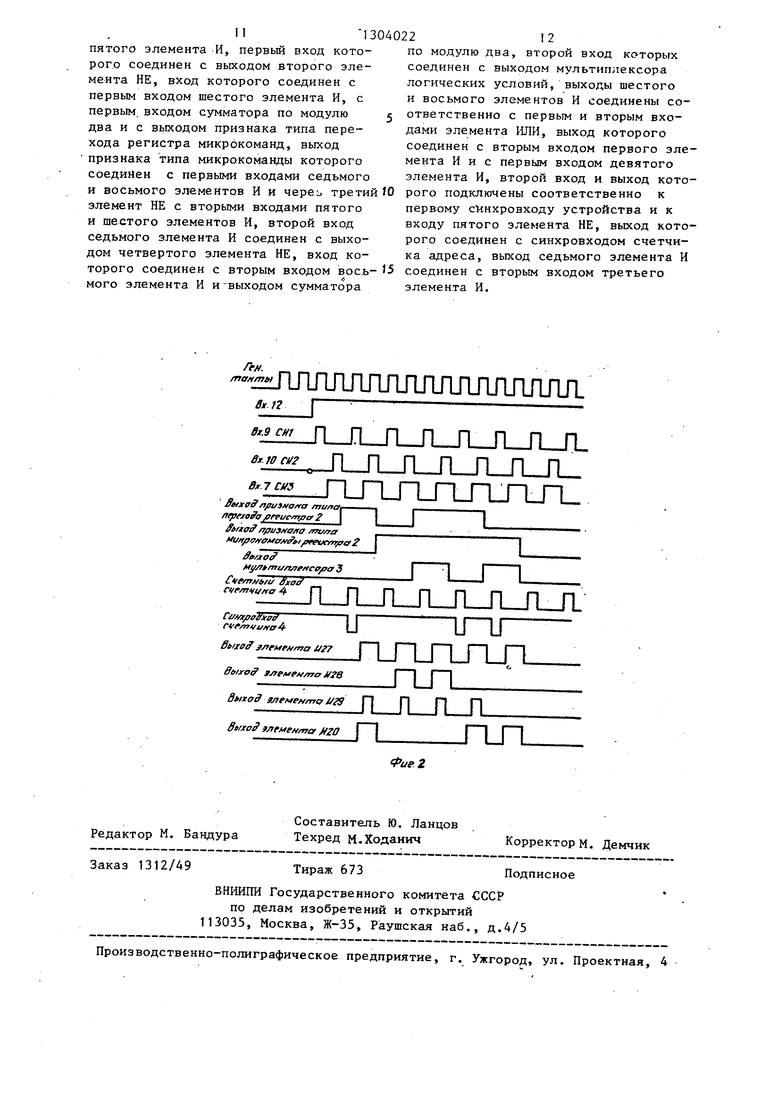

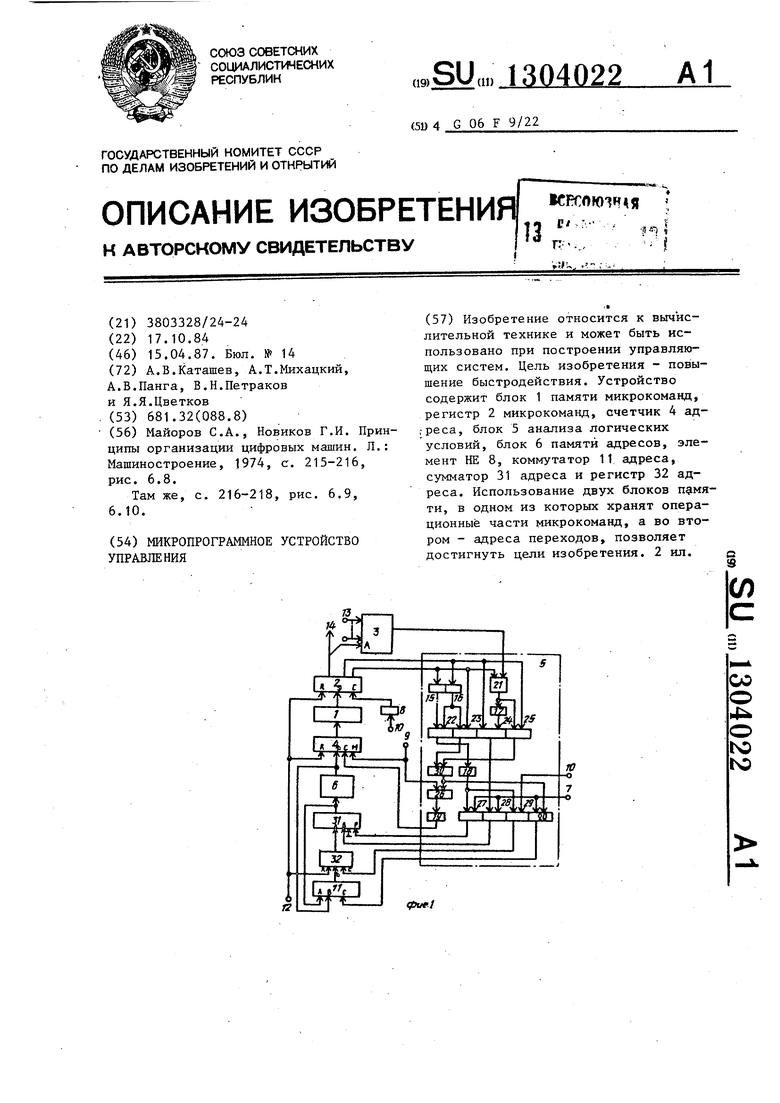

На фиг. 1 представлена функцио- О нальная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, иллюстрируюп1ие его работу. .

Микропрограммное устройство управления содержит блок 1 памяти микро- 5 ра 2 через элементы НЕ 15, 16, уже команд, регистр 2 микрокоманд, муль- как логические единицы, поступают типлексор 3 логических условий, счетчик 4 адреса, блок 5 анализа логических условий, блок 6 памяти адресов, третий синхровход 7, элемент НЕ 8, 20 первьй 9 и второй 10 синхровходы, коммутатор 11 адреса, вход 12 сброса, группу 13 входов логических условий, выход 14.

микрокоманд установятся значения л гического О.

В результате на выходе элемента И 22 установится сигнал логической 1 (так как значения выходов реги

на вход данного элемента И).

На выходах элементов И 23-25 так как хотя бы на

логический О,

одном из входов каждого из этих эл ментов присутствует сигнал логичес кого О.

Сигнал логической 1 с выхода элемента И 22 через элемент НЕ 18

Блок 5 анализа логических условий содержит второй 15, третий 16, чет- вертый 17, первый 18 и пятый 19 элементы НЕ, первый элемент И 20, сумматор 21 по модулю два, пятый 22, шестой 23, седьмой 24, восьмой 25, девятый 26, второй 27, третий 28 и четвертый 29 элементы И, элемент ИЛИ 30. Кроме того, устройство содержит сумматор 31 адреса и регистр гистра 32 - логический О и на

32 адреса.

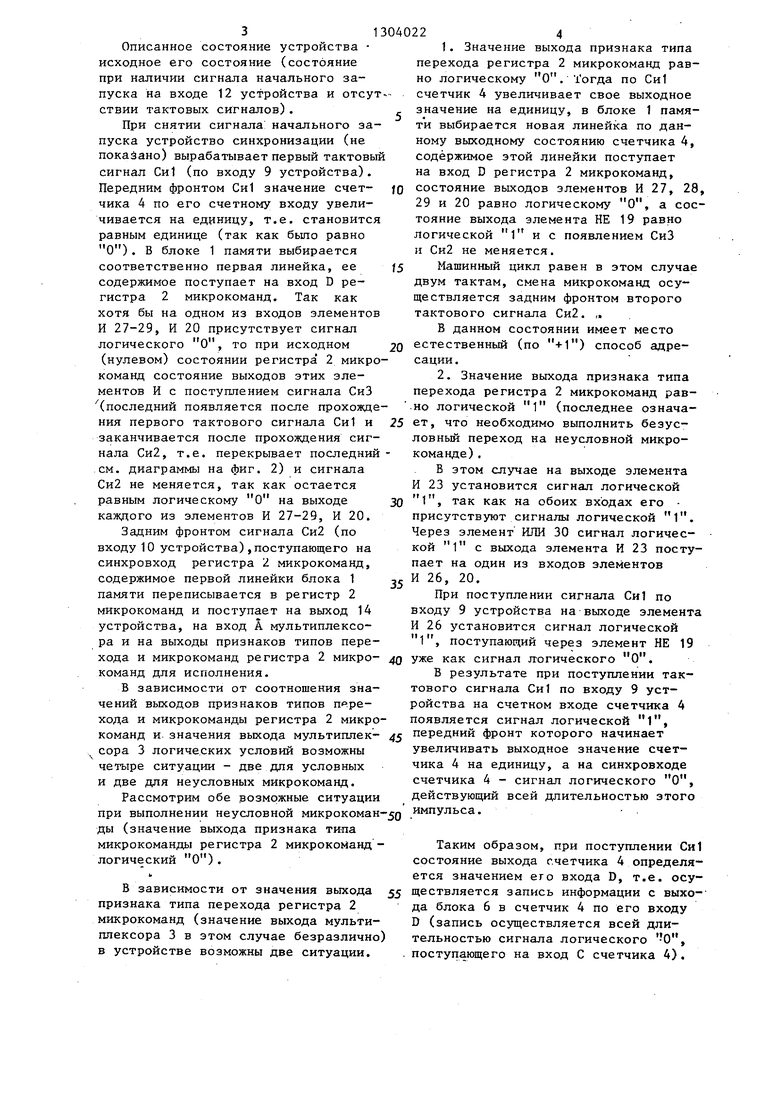

На фиг-. 2 обозначено:Си1 - сигнал на входе 9; Си2 - сигнал на входе 10; СиЗ - сигнал на входе 7.

Микропрограммное устройство управления работает следующим образом,

При наличии сигнала сброса (на- чального запуска) на входе 12 устройства синхросигналы на входы устройства не поступают.

Сигналом по.входу 12 устройства на входы R установки в ноль р егистра 2 микрокоманд, счетчика 4 и регистра 32 адреса оба регистра и счетуправляющем входе С коммутатора также логический О.

Последний означает, что выход коммутатора 11 переключен на его

40 вход А, т.е. на выход сумматора так как исходное выходное состоя регистра 32 адреса - нулевое, то выходе сумматора 31 также нулево состояние. Данное состояние сумм

45 31 поступает на вход А коммутато и на информационный вход блока 6 мяти, в котором выбирается соотв ственно нулевая линейка. Содержи нулевой линейки блока 6 памяти п

чик устанавливаются в исходное, нап- о пает ria вход D счетчика 4 и на вход В ример нулевое, состояние. По исходным коммутатора 11 (но на выход послед- (нулёвым) выходным состояниям счет- чика 4 и регистра 32 адреса в блоках 1 и 6 памяти выбираются соответственно нулевые линейки. Содержи- По нулевому исходному состоянию мое нулевой линейки блока 1 памяти счетчика 4 в блоке 1 памяти выбрана

него не проходит, так как на входе С коммутатора - логический О).

поступает на информационный- вход D регистра 2 микрокоманд, а содержимое нулевой линейки блока 6 памяти

адресов (переходов) - на вход D счетчика 4. Так как при наличии сигнала начального запуска не вырабатываются тактовые сигналы Си1, Си2, то

указанные выходные состояния блоков

1 и 6 далее не проходят.

По исходному (нулевому) состоянию регистра 2 микрокоманд на выходе 14 устройства на выходах регистра 2

ра 2 через элементы НЕ 15, 16, уже как логические единицы, поступают

микрокоманд установятся значения логического О.

В результате на выходе элемента И 22 установится сигнал логической 1 (так как значения выходов регистра 2 через элементы НЕ 15, 16, уже как логические единицы, поступают

на вход данного элемента И).

На выходах элементов И 23-25 ра 2 через элементы НЕ 15, 16, уже как логические единицы, поступают

так как хотя бы на

логический О,

одном из входов каждого из этих элементов присутствует сигнал логичес- кого О.

Сигнал логической 1 с выхода элемента И 22 через элемент НЕ 18

логическим О поступает на один из входов элементов И 27, 29. На выходе элемента НЕ 19 установится сигнал логической 1. Следовательно, на счетном входе счетчика 4 - логическций О а на синхровходе - логичес- кая 1, на входе Р (переноса) и младшем разряде группы В информационных входов сумматора 31 - логические на синхровходе ре гистра 32 - логический О и на

управляющем входе С коммутатора 1t также логический О.

Последний означает, что выход коммутатора 11 переключен на его

40 вход А, т.е. на выход сумматора 31, так как исходное выходное состояние регистра 32 адреса - нулевое, то на выходе сумматора 31 также нулевое состояние. Данное состояние сумматора

45 31 поступает на вход А коммутатора 11 и на информационный вход блока 6 памяти, в котором выбирается соответственно нулевая линейка. Содержимое нулевой линейки блока 6 памяти поступает ria вход D счетчика 4 и на вход В коммутатора 11 (но на выход послед- По нулевому исходному состоянию счетчика 4 в блоке 1 памяти выбрана

него не проходит, так как на входе С коммутатора - логический О).

соответственно нулевая линейка, содержимое которой поступает на вход D регистра 2 микрокоманд.

Описанное состояние устройства исходное его состояние (состояние при наличии сигнала начального запуска на входе 12 устройства и отсут ствии тактовых сигналов).При снятии сигнала начального запуска устройство синхронизации (не показано) вырабатывает первый тактовый сигнал Си1 (по входу 9 устройства). Передним фронтом Си1 значение счет- чика 4 по его счетному входу увеличивается на единицу, т.е. становится равным единице (так как бьшо равно О). В блоке 1 памяти выбирается соответственно первая линейка, ее содержимое поступает на вход D регистра 2 микрокоманд. Так как хотя бы на одном из входов элементов И 27-29, И 20 присутствует сигнал логического О, то при исходном (нулевом) состоянии регистра 2 микрокоманд состояние выходов этих элементов И с поступлением сигнала СиЗ (последний появляется после прохождения первого тактового сигнала Си1 и заканчивается после прохождения си1- нала Си2, т.е. перекрывает последний см. диаграммы на фиг. 2) и сигнала Си2 не меняется, так как остается равным логическому О на выходе каждого из элементов И 27-29, И 20.

Задним фронтом сигнала Си2 (по входу 10 устройства),поступающего на синхровход регистра 2 микрокоманд, содержимое первой линейки блока 1 памяти переписывается в регистр 2 микрокоманд и поступает на выход 14 устройства, на вход А мультиплексора и на выходы признаков типов перехода и микрокоманд регистра 2 микро- команд для исполнения.

В зависимости от соотношения значений выходов признаков типов хода и микрокоманды регистра 2 микрокоманд и значения выхода мультиплек- сора 3 логиче.ских условий возможны четыре ситуации - две для условных и две для неусловных микрокоманд.

Рассмотрим обе возможные ситуации при выполнении неусловной микрокоман ды (значение выхода признака типа микрокоманды регистра 2 микрокоманд - логический О).

t

В зависимости от значения выхода признака типа перехода регистра 2 микрокоманд (значение выхода мультиплексора 3 в этом случае безразлично в устройстве возможны две ситуации.

1. Значение выхода признака типа перехода регистра 2 микрокоманд равно логическому О. Тогда по Си1 счетчик 4 увеличивает свое выходное значение на единицу, в блоке 1 памяти выбирается новая линейка по данному выходному состоянию счетчика 4, содержимое этой линейки поступает на вход D регистра 2 микрокоманд, состояние выходов элементов И 27, 28 29 и 20 равно логическому О, а состояние выхода элемента НЕ 19 равно логической 1 и с появлением СиЗ и Си2 не меняется.

Машинный цикл равен в этом случае двум тактам, смена микрокоманд осуществляется задним фронтом второго тактового сигнала Си2. ,.

В данном состоянии имеет место естественный (по +1) способ адресации.

2. Значение выхода признака типа перехода регистра 2 микрокоманд равно логической 1 (последнее означает, что необходимо выполнить безусловный переход на неусловной микрокоманде) .

В этом случае на выходе элемента И 23 установится сигнал логической 1, так как на обоих входах его - присутствуют сигналы логической 1. Через элемент ИЛИ 30 сигнал логической 1 с выхода элемента И 23 поступает на один из входов элементов И 26, 20.

При поступлении сигнала Си1 по входу 9 устройства на выходе элемента И 26 установится сигнал логической 1, поступающий через элемент НЕ 19 уже как сигнал логического О.

В результате при поступлении тактового сигнала Си1 по входу 9 устройства на счетном входе счетчика 4 появляется сигнал логической 1, передний фронт которого начинает увеличивать выходное значение счетчика 4 на единицу, а на синхровходе счетчика 4 - сигнал логического О, действующий всей длительностью этого импульса.

Таким образом, при поступлении Си состояние выхода г.четчика 4 определяется значением его входа D, т.е. осуществляется запись информации с выхо да блока 6 в счетчик 4 по его входу D (запись осуществляется всей длительностью сигнала логического О, поступающего на вход С счетчика 4).

Так как к моменту появления тактового сигнала Си1 значения входа Р и Ь4падшегоразряда группы входов В сумматора 31 равны логическому О, на выходе блока 6 памяти присутствует содержимое линейки этого блока, выбранной в нем по адресу - выходному состоянию регистра 32 адреса.

Кроме того, сигнал логической 1 с выхода признака типа перехода регистра 2 микрокоманд через элементы НЕ 15, И 22 и НЕ 18 поступает на один из входов элементов И 27, 29. На одном из входов элемента И 28 присутствует сигнал логического О с выхода элемента И 24, а на одном из входов элемента И 20 - сигнал логической 1 с выхода элемента ИЛИ 30.

С поступлением сигнала СиЗ (на

входе 7 устройства) на выходе элемен-20 случае значение выхода признака типа

та И 27 устанавливается сигнал логической 1, который поступает на вход Р сумматора 31 и увеличивает его содержимое на единицу относительно

выходного состояния регистра 32 адре- 25 вий определяется (как обычно ) условиса. По полученному выходному состоя-. нию сумматора 31 в блоке 6- выбирается следующая линейка, содержимое которой поступает на вход Б коммутатора I1, на управляющий вход С которого посту- пает сигнал лонической 1 с выхода элемента И 20 (на первом его входе логическая 1 с входа 7, а на втором - логическая 1 с выхода элемента ИЛИ 30). Таким образом, на вы- ходе коммутатора 11 устанавливается значение выхода блока 6.

При поступлении переднего фронта сигнала Си2 по входу 10 устройства на .выходе элемента И 29 появляется сигнал логической 1, так как теперь на обеих его входах присутствуют сигналы логической 1.

Сигнал логической 1 с выхода элемента И 29 поступает на синхро- вход регистра 32 и передним фронтом записывает содержимое выхода блока 6 в регистр 32 адреса.

Данное выходное состояние регистра 32 является новым адресом для блока 6 после безусловного перехода по микро- программе в блоке 1. Таким образом, за счет изменения значения счетчика 4 по сигналу Си1 осуществляется безу

слоэный переход на неусловной микро- 55 28. С выхода элемента НЕ 18 сигнал команде: по Си1 в счетчик 4 записы- логической 1 поступает на первые ватеся содержимое линейки блока 6 входы элементов И 27, 29 (на выходах

|элементов И 22, 23,, 25 присутствуют сигналы логического О).

памяти адресов (переходов), выбранной по адресу - выходному состоянию регистра 32 адреса, проходящему через сумматор 31 без изменения и представляющему собой адрес безусловного перехода, по которому в блоке 1 памяти

выбирается соответствующая линейка, затем по СиЗ выходное значение сумматора 31 увеличивается на единицу и через коммутатор 11 (по входу В его) содержимое следующей линейки блока 6

(по переднему фронту Си2) перепищется в регистр 32 адреса, представляя собой адрес ДД1Я выбора следующей линейки в блоке 6 памяти адресов (переходов) .

Рассмотрим далее две возможные

ситуации в устройстве в случае выполнения условной микрокоманды (выход признака типа микрокоманды регистра 2 микрокоманд - логическая 1). В этом

перехода регистра 2 микрокоманд может иметь значение логического О или логической 1, а значение выхода мультиплексора 3 логических усло

ями, поступающими на его информационные входы по группе входов 13 устройства. . .

Выбор пути формирования адреса следующей микрокоманды микропрограммы определяется соотношением значений выхода признака типа перехода регист- ра 2 микрокоманд и выхода мультиплексора 3.

Пусть значение выхода признака типа перехода регистра 2 - логический О, значение выхода мультиплексора 3 условий - также логический ноль, т.е. совпадают (однозначны).

В этом случае на выходе сумматора присутствует сигнал так как сигналы на 21 однозначны. НЕ 17 этот сигнал.

21 по модулю два логического О, входах сумматора Через элемент

уже как сигнал логической еданицы, поступает на один из входов элемента И 24, на втором входе этого элемента присутствует сигнал логической 1 с выхода признака типа микрокоманды регистра 2 микрокоманд (так как сматриваем случай вьшолнения условий ; микрокоманды). На выходе элемента И 24 - сигнал логической 1, который поступает на первый вход элемента

713

При поступлении переднего фронта тактового сигнала Си1 по входу 9 устройства на счетный вход счетчика 4 значение выхода его увеличивается на единицу. В блоке 1 памяти по дан- ному адресу (полученное выходное состояние счетчика 4) выбирается следующая линейка, содержимое которой (сле

Пусть значения выходов мультиплексора 3 логических условий и выхода признака типа перехода регистра 2 микрокоманд неоднозначны, т.е. когда

II 1 М

второй - логический О

дующая микрокоманда микропрограммы)

поступает на вход D регистра 2 микро-Ю один имеет на выходе логическую команд -(но до поступления тактового сигнала Си2 не переписывается в регистр 2 микрокоманд).

При поступлении переднего фронта управляющего сигнала СиЗ на выходах элементов И 27, 28 появляются сигналы логической 1, поступающие соответственно на вход Р (переноса) и младший разряд группы В информацион Г

, и наооорот.

В этом случае на выходе сумматора 21 по модулю два установится сигнал логической 1 (так как сигналы на 15 входах сумматора 21 неравнозначны). Этот сигнал логической 1 поступает на один из входов элеме-нта И 25, на втором входе которого присутствует сигнал логической 1 с выхода приз- ных входов сумматора 31-. В р езультате О шака типа микрокоманды регистра 2 на выходе сумматора устанагливается микрокоманд. Следовательно, на выходе значение, увеличенное на два по сравнению с предыдущим, равным выходному значению регистра 32 .адреса.

При поступлении переднего фронта тактового сигнала Си2 на второй вхОд элемента И 29 (на первом входе которого - сигнал логической выхода элемента НЕ 18) на выходе последнего

25

элемента И 25 устанавливается сигнал логической l, который через элемент ИЛИ 30 поступает на один из входов элементов И 26 и 20.

При поступлении переднего фронта тактового сигнала Си1 по входу 9 устройства на счетный вход счетчика 4 состояние последнего начинает измепоявляется сигнал логической 1 дли- няться.

тельностью, равной длительности Си2. Этот сигнал поступает на синхровход регистра 32 адреса, записывая передним фронтом по его входу D информацию, поступающую с выхода сумматора 31 через коммутатор Т1 (по его входу А), так как на входе С последнего присутствует сигнал логического О.

В результате выходное состояние сумматора 31, отличающееся от предыдущего на два, по переднему фронту тактового сигнала Си2 переписано в регистр 32 адреса, а по заднему фронту Си2. следующая микрокоманда (выб-. ранная в блоке 1 памяти по адресу - выходному состоянию счетчика 4 при поступлении Си1) с входа D регистра 2 микрокоманд переписывается в последний. Так осуществляется естественный способ адресации при выполнении условной микрокоманды.

35

40

Одновременно (при поступлении Си1) на выходе элемента И 26 устанавливается сигнал логической 1, так как на обоих его входах присутствуют сигналы логической единицы (на одном входе Си1, на втором - сигнал логической 1 с выхода сумматора 21 через элементы И 25 и ИЛИ 30). В результате на выходе элемента НЕ 19

устанавливаетря сигнал логического О длительностью Си1. Этот сигнал, поступая на синхровход счетчика 4, осуществляет запись информации с выхода блока 6 памяти (по входу D счет- 45 чика 4), значение выходов элементов И 27-29, И 20 при наличии Си1 равно логическому О.

В результате на выходе счетчика 4 50 устанавливается содержимое линейки блока 6 памяти адресов, выбранной в последнем по адресу - выходному состоянию регистра 32 адреса (сумматор 31 изменений не вносит, так как на ческих условий и выхода признака типа 5 входах Р и В при наличии сигнала перехода регистра 2 микрокоманд рабо- Си1 присутствуют сигналы логического та устройства аналогична описанной, О), По полученному таким образом т.е. осуществляется естественный спо- адресу - выходному состоянию счет- соб адресации: в блоке 1 памяти по чика 4 в блоке 1 памяти выбирается

При единичном значении (логическая 1) выходов мультиплексора 3 логи +1

а в блоке 6-памяти адресов (переходов) - по +2.

Рассмотрим вторую ситуацию для случая выполнения условной микрокоманды.

Пусть значения выходов мультиплексора 3 логических условий и выхода признака типа перехода регистра 2 микрокоманд неоднозначны, т.е. когда

II 1 М

один имеет на выходе логическую

Г

второй - логический О

один имеет на выходе ло

В этом случае на выходе сумматора 21 по модулю два установится сигнал логической 1 (так как сигналы на входах сумматора 21 неравнозначны). Этот сигнал логической 1 поступает на один из входов элеме-нта И 25, на втором входе которого присутствует сигнал логической 1 с выхода приз- ака типа микрокоманды регистра 2 микрокоманд. Следовательно, на выходе

элемента И 25 устанавливается сигнал логической l, который через элемент ИЛИ 30 поступает на один из входов элементов И 26 и 20.

При поступлении переднего фронта тактового сигнала Си1 по входу 9 устройства на счетный вход счетчика 4 состояние последнего начинает изменяться.

Одновременно (при поступлении Си1) на выходе элемента И 26 устанавливается сигнал логической 1, так как на обоих его входах присутствуют сигналы логической единицы (на одном входе Си1, на втором - сигнал логической 1 с выхода сумматора 21 через элементы И 25 и ИЛИ 30). В результате на выходе элемента НЕ 19

40

устанавливаетря сигнал логического О длительностью Си1. Этот сигнал, поступая на синхровход счетчика 4, осуществляет запись информации с выхода блока 6 памяти (по входу D счет- 45 чика 4), значение выходов элементов И 27-29, И 20 при наличии Си1 равно логическому О.

линейка, содержимое которой поступает на вход D регистра 2 микрокоманд (но до поступления тактового сигнала Си2 не переписывается в регистр 2).

При поступлении сигнала СиЗ по входу 7 устройства на выходе элемента И 27 появится сигнал логической l, поступающий на вход Р переноса сумматора 31, Длительность этого сигнала равна длительности сигнала СиЗ. I В результате на выходе сумматора 31 установится значение, равное выходному значению регистра 32 адреса плюс единица и представляющее собой адрес, по которому в блоке 6 памяти выбирается следукяцая линейка. Содержимое этой линейки с выхода блока б памяти поступает на вход D счетчика 4 и на вход В (второй информационный ,вход) коммутатора 11.

Одновременно (с момента поступления сигнала СиЗ) на выходе элемента И 20 устанавливается сигнал логической }, поступающий на вход С (упгистра микрокоманд соединен с выходом блока памяти микрокоманд, адресный- вход которого соединен с информационным выходом счетчика адреса, счет5 ный вход которого подключен к первому синхровходу устройства, синхровход регистра микрокоманд подключен черей элемент НЕ к второму синхровходу устройства, выходы поля микроопераций

JO и поля проверки Логических условий регистра микрокоманд подключены соответственно к выходу устройства и к управляющему входу мультиплексора логических условий, группа информа1-5 ционных входов которого подключена к группе входов логических условий уатройства, отличающееся тем, что, с целью повышения быстродействия оно содержит блок памяти

20 адресов, регистр адреса, сумматор

адреса, коммутатор адреса и блок анализа логических условий, содержащий пять элементов HiS, сумматор по модулю два, девять элементов И и элеравляющий вход) коммутатора 11, пере-25 мент ИЛИ, причем вход сброса регистра ключающий его выход на собственньм вход В. С поступлением переднего фронта тактового сигнала Си2 по входу 10 устройство на выходе элемента И 29 установится сигнал логической 1, так как на обоих входах его присутствуют сигналы логической 1 (на одном входе - с выхода элемента НЕ 18, на втором - с входа 10 устройства).

адреса подключен к входу сброса устройства, информационньй вход счетчика адреса соединен с выходом блока памяти адресов и с первым информационным

30 входом коммутатора адреса, второй информационный вход которого соединен с адресным входом блока памяти адресов и с выходом сумматора адреса, первая группа информационных входов

элемента И 29 поступает на синхровход регистра 32 адреса. Передним фронтом этого сигнала осуществляется запись информации с входа В коммута-. тора 11, через последний - в регистр 32 адреса (по его входу D).

По данному адресу Опо выходному состоянию регистра 32) в блоке 6 памяти будет выбрана новая линейка, содержимое которой является адресом следующего безусловного перехода на условной .или неусловной микрокоманде данного устройства.

Формула изобретения

старших разрядов второй группы инфорМикропрограммное устройство управ- мационных входов.сумматора адреса ления, содержащее блок памяти микро- подключен к шине нулевого потенциала команд, регистр микрокоманд, счетчик устройства, первый вход четвертого адреса, мультиплексор логических ус- элемента И подключен к второму синх- ловий и элемент НЕ, причем входы ровходу устройства, вторые входы сброса регистра микрокоманд и счетчи- второго и четвертого элементов И сока адреса подключены к входу сброса , единены с выходом первого элемента устройства, информационный вход ре- НЕ, вход которого соединен с выходом

гистра микрокоманд соединен с выходом блока памяти микрокоманд, адресный- вход которого соединен с информационным выходом счетчика адреса, счетный вход которого подключен к первому синхровходу устройства, синхровход регистра микрокоманд подключен черей элемент НЕ к второму синхровходу устройства, выходы поля микроопераций

и поля проверки Логических условий регистра микрокоманд подключены соответственно к выходу устройства и к управляющему входу мультиплексора логических условий, группа информационных входов которого подключена к группе входов логических условий уатройства, отличающееся тем, что, с целью повышения быстродействия оно содержит блок памяти

адресов, регистр адреса, сумматор

адреса, коммутатор адреса и блок анализа логических условий, содержащий пять элементов HiS, сумматор по модулю два, девять элементов И и элемент ИЛИ, причем вход сброса регистра

мент ИЛИ, причем вход сброса регистра

адреса подключен к входу сброса устройства, информационньй вход счетчика адреса соединен с выходом блока памяти адресов и с первым информационным

входом коммутатора адреса, второй информационный вход которого соединен с адресным входом блока памяти адресов и с выходом сумматора адреса, первая группа информационных входов

которого соед,инена с группой выходов регистра адреса, информационный вход которого соединен с выходом коммутатора адреса, управляющий вход которого соединен с выходом первого элемента И, первый вход которого соединен с первыми входами второго и третьего элементов И и .подключен к третьему синхровходу устройства, выходы второго, третьего и четвертого элементов

И соединены Соответственно с входом переноса сумматора адреса, с информационным входом младшего разряда второй группы информационных входо в сумматора адреса и с синхровходом

регистра адреса, информационный вход

II

пятого элемента И, первый вход которого соединен с выходом второго элемента НЕ, вход которого соединен с первым входом шестого элемента И, с первым, входом сумматора по модулю два и с вькодом признака типа перехода регистра микрокоманд, выход признака типа микрокоманды которого соединен с первыми входами седьмого и восьмого элементов И и череь трети элемент НЕ с вторыми входами пятого и шестого элементов И, второй вход седьмого элемента И соединен с выходом четвертого элемента НЕ, вход которого соединен с вторым входом вось мого элемента И и-выходом сумматора

Гек.

:f fLnj irmjmjuirmjiJi

4022

12

5/О 5

по модулю два, второй вход которых соединен с выходом мультиплексора логических условий, выходы шестого и восьмого элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и с первьм входом девятого элемента И, второй вход и выход которого подключены соответственно к первому синхровходу устройства и к входу пятого элемента НЕ, выход которого соединен с синхровходом счетчика адреса, выход седьмого элемента И соединен с вторым входом третьего элемента И.

..LJl JLJIJl, П П П П П П П П П П

П П П П П

I j j I

U LJ

j I I I j 1 j I j j I

П П П

Si xoff элемента ZO I I

Редактор М. Бандура

Составитель Ю. Ланцов Техред М.Ходаиич

Заказ 1312/49

Тираж 673

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ЛЛКорректор М. Демчик

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1304021A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1293729A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1429114A1 |

| Микропрограммное устройство управления (его варианты) | 1984 |

|

SU1159020A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1275441A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих систем. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, счетчик 4 ад- ,-реса, блок 5 анализа логических условий, блок 6 памяти адресов, элемент НЕ 8, коммутатор 11 адреса, сумматор 31 адреса и регистр 32 адреса. Использование двух блоков ти, в одном из которых хранят операционные части микрокоманд, а во втором - адреса переходов, позволяет достигнуть цели изобретения. 2 ил. /4 со о 4 О N5 0«Ж/

| Майоров С.А., Новиков Г.И | |||

| Принципы организации цифровых машин | |||

| Л.: Машиностроение, 1974, с | |||

| Кузнечный горн | 1921 |

|

SU215A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Там же, с, 216-218, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-15—Публикация

1984-10-17—Подача