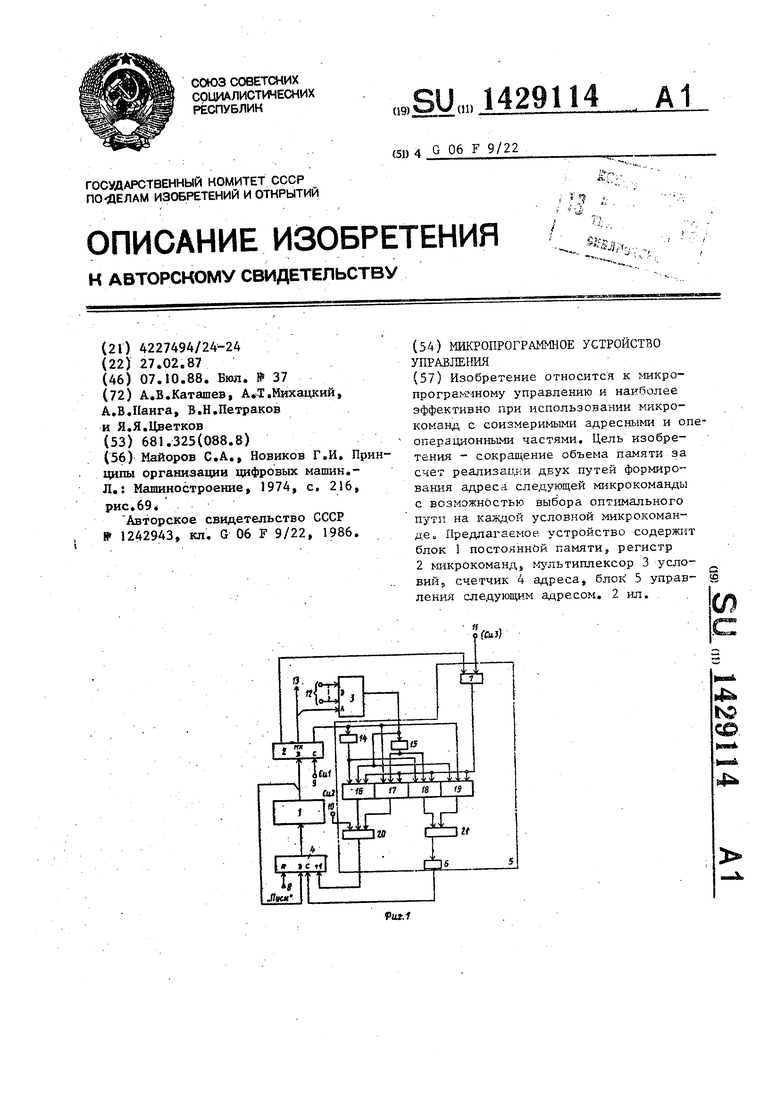

Изобретение относится к микропрограммному управлению и наиболее эффективно может быть использовано в вычислительной технике, например в ЭВМ, при построении управляющих систем, а также самостоятельных микро- трограммных автоматов с микрокомандами, адресные и операционные части которых соизмеримы по разрядности.

Цель изобретения - сокращение объе яа памяти за счет реализации двух путей формирования адреса следующей ушкрокоманды с возможностью выбора оптимального пути на каждой условной микрокоманде.

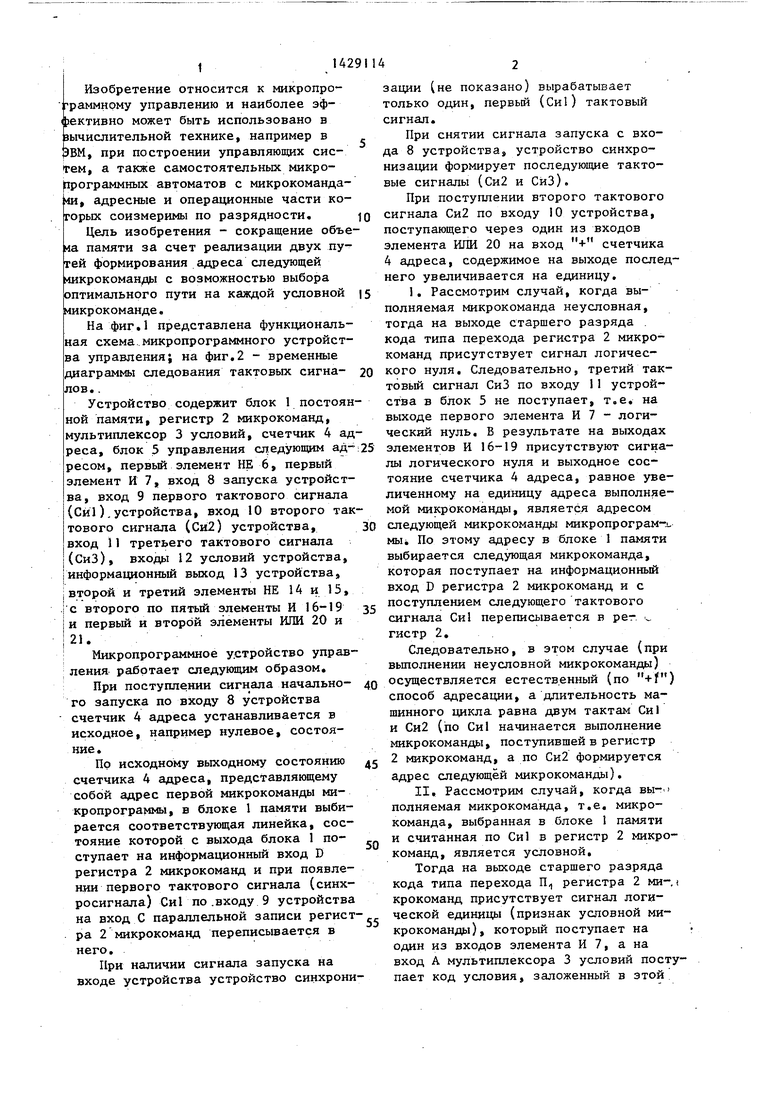

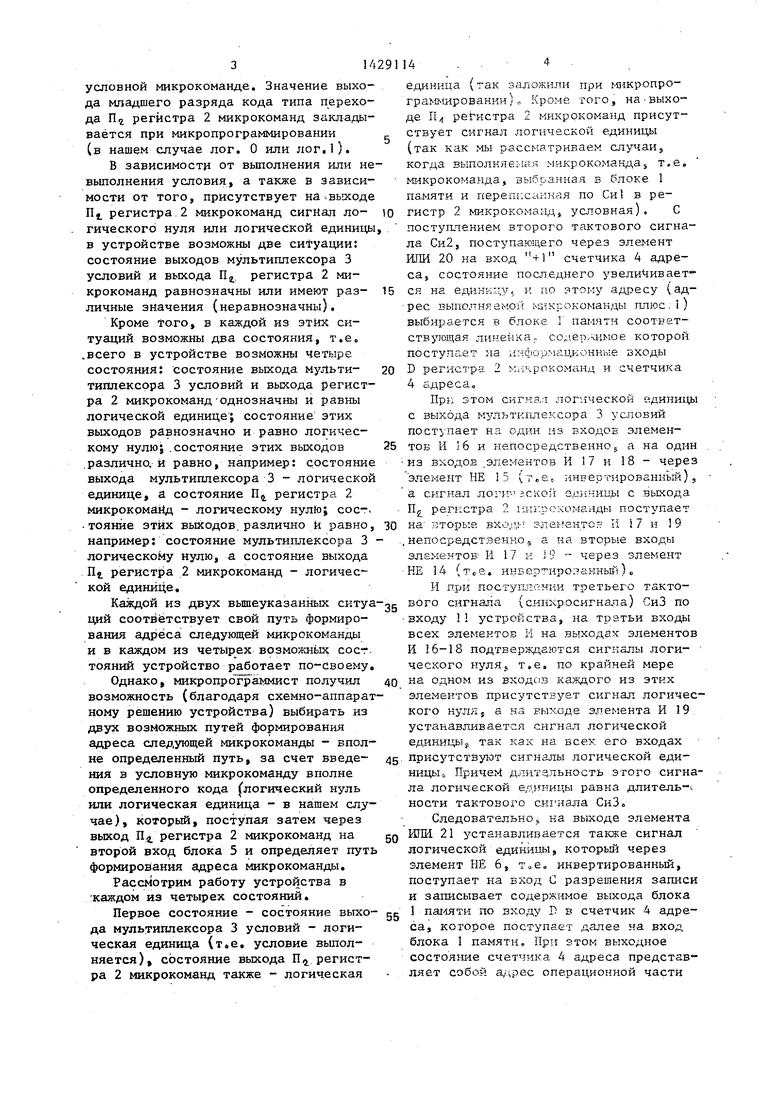

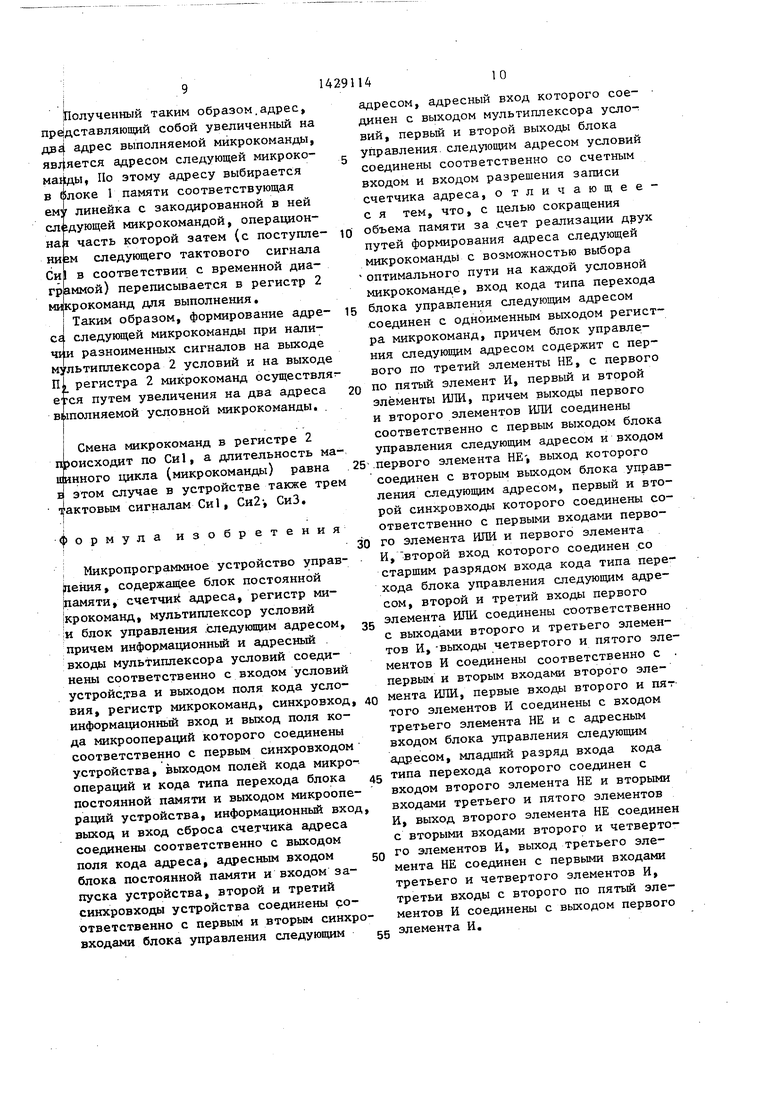

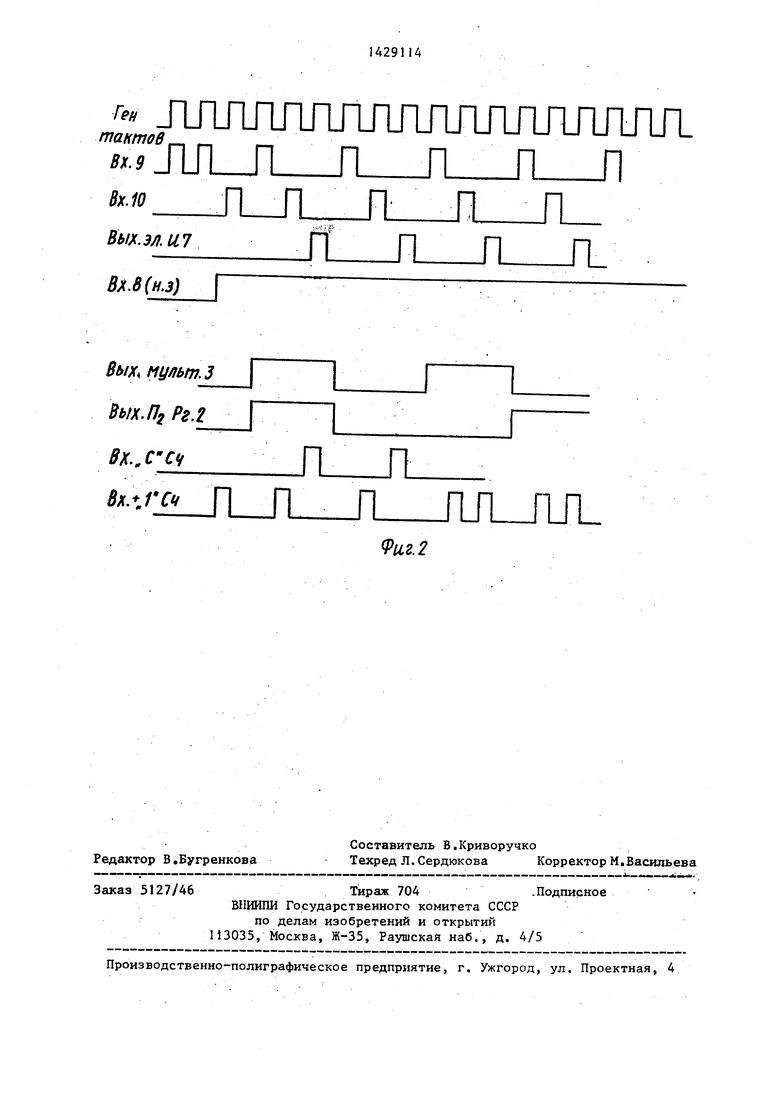

На фиг,1 представлена функциональная схема микропрограммного устройства управления; на фиг.2 - временные диаграммы следования тактовых сигна- лов..

Устройство содержит блок 1 постоянной памяти, регистр 2 микрокоманд, мультиплексор 3 условий, счетчик 4 адреса, блок 5 управления следующим адресом, первый элемент НЕ 6, первый элемент И 7, вход 8 запуска устройства, вход 9 первого тактового сигнала I(Сй1),устройства, вход 10 второго тактового сигнала (Си2) устройства, вход 11 третьего тактового сигнала (СиЗ), входы 12 условий устройства, информационный выход 13 устройства, второй и третий элементы НЕ 14 и 15, с второго по пятый элементы И 16-19 и первый и второй элементы ИЛИ 20 и 21.

Микропрограммное устройство управления работает следующим образом.

При поступлении сигнала начально- го запуска по входу 8 устройства счетчик 4 адреса устанавливается в исходное, например нулевое, состояние.

По исходному выходному состоянию

счетчика 4 адреса, представляющему собой адрес первой микрокоманды микропрограммы, в блоке 1 памяти выбирается соответствующая линейка, состояние которой с выхода блока 1 поступает на информационный вход D регистра 2 микрокоманд и при появлении первого тактового сигнала (синхросигнала) Си1 по .входу 9 устройства на вход С параллельной записи регистра 2 микрокоманд переписывается в него.

При наличии сигнала запуска на входе устройства устройство синхрони

5 0 5

О

5

0

5

зации не показано) вырабатывает только один, первый (Си1) тактовый сигнал.

При снятии сигнала запуска с входа 8 устройства, устройство синхронизации формирует последующие тактовые сигналы (Си2 и СйЗ).

При поступлении второго тактового сигнала Си2 по входу 10 устройства, поступающего через один из входов элемента ИЛИ 20 на вход + счетчика 4 адреса, содержимое на выходе последнего увеличивается на единицу.

I.Рассмотрим случай, когда выполняемая микрокоманда неусловная, тогда на выходе старшего разряда . кода типа перехода регистра 2 микрокоманд присутствует сигнал логического нуля. Следовательно5 третий так- товьй сигнал СиЗ по входу 11 устройства в блок 5 не поступает, т.е. на выходе первого элемента И 7 - логический нуль. В результате на выходах элементов И 16-19 присутствуют сигналы логического нуля и выходное состояние счетчика 4 адреса, равное увеличенному на единицу адреса выполняемой микрокоманды, является адресом следующей микрокоманды микропрограм-а, мьи По этому адресу в блоке 1 памяти выбирается следующая микрокоманда, которая поступает на информационный вход D регистра 2 микрокоманд и с поступлением следующего тактового сигнала Си1 переписывается в ре- гистр 2.

Следовательно, в этом случае (при выполнении неусловной микрокоманды) осуществляется естественный (по +f) способ адресации, а длительность машинного цикла равна двум тактам Си1 и Си2 (по Си1 начинается выполнение микрокоманды, поступившей в регистр 2 микрокоманд, а по Си2 формируется адрес следующей микрокоманды).

II.Рассмотрим случай, когда вы- полняемая микрокоманда, т.е. микрокоманда, выбранная в блоке I памяти

и считанная по Си1 в регистр 2 микрокоманд, является условной.

Тогда на выходе старшего разряда кода типа перехода П регистра 2 ми-, i крокоманд присутствует сигнал логической единицы (признак условной микрокоманды), который поступает на один из входов элемента И 7, а на вход А мультиплексора 3 условий поступает код условия, заложенный в этой

316

условной микрокоманде. Значение выхода младшего разряда кода типа перехода П, регистра 2 микрокоманд закладывается при микропрограммировании (в нашем случае лог. О или лог,1).

В зависимости от выполнения или невыполнения условия, а также в зависимости от того, присутствует на-выходе П регистра.2 микрокоманд сигнал ло- гического нуля или логической единицы в устройстве возможны две си уации: состояние выходов мультиплексора 3 условий и выхода П. регистра 2 микрокоманд равнозначны или имеют раз- личные значения (неравнозначны).

Кроме тото, в каждой из этих ситуаций возможны два состояния, т.е. .всего в устройстве возможны четыре состояния: состояние выхода мульти- типлексрра 3 условий и выхода регистра 2 микрокоманд Однозначны и равны логической единице; состояние этих выходов равнозначно и равно логическому нулю , .состояние этих выходов .различно, и равно, например: состояние выхода мультиплексора 3 - логической единице, а состояние П регистра 2 микрокоманд - логическому сое-. .тояние этих выходов, различно h равно, например: состояние мультиплексора 3 логическому нулю, а состояние выхода IIj регистра 2 микрокоманд - логической единице.

Каждой из двух вьшеуказанных ситуа ций соответствует свой путь формирования адреса следующей микрокоманды и в каждом из четырех возможньхх сосг. тояний устройство работает по-своему,

Однако, микропрбгфаммист получил возможность (благодаря схемно-аппарат ному решению устройства) выбирать из двух возможных путей формирования адреса следующей микрокоманды - вполне определенный путь, за счет введе- ния в условную микрокоманду вполне определенного кода | логический нуль или логическая единица - в нашем случае), который, поступая затем через выход П4 регистра 2 микрокоманд на второй вход блока 5 и определяет путь формирования адреса микрокоманды.

Рассмотрим работу устройства в :каждом из четырех состояний.

Первое состояние - состояние выхо- да мультиплексора 3 условий - логическая единица (т.е. условие выполняется) состояние выхода П регистра 2 микрокоманд также - логическая

4 . - 4 .

единица (так заложили при микропрограммировании) Кроме того, навыходе II регистра 2 микрокоманд присутствует сигнал логической единицы (так как мы рассматриваем случаи, когда выполняе:-1ая микрокомандаj , микрокоманда, выбранная в блоке 1 памяти и переписанная по Си в регистр 2 микрокомандJ условная), С поступлением второго тактового сигнала Си2, поступающего через элемент ИЛИ 20 на вход + счетчика 4 адреса j состояние последнего увели ивает- ся на единицу,, к по этоку адресу (ад- рее выполняемой ьшкрокоманды плюс.1) выбирается в блоке 3 памяти соответствующая линейка,. .iiMoe которой поступает на информационные входы D регистра 2 М11Крокоманд и счетчика

4адреса,

Ерк этом сигиа.л логической йдиницы с выхода мз льткплексора 3 условий поступает на один нз входов элементов И 16 и непосредственно; а на один из входов элег-feHTOB И 17 и 18 - через элемент НЕ 15 (, инвер оировапкый), а сигнал лоп-г- гской еди.чицы с выхода П регистра 2 микрскоманды поступает на- вторые вхо-д ; злвг ентсв И 17 и 19 непосредственно а на вторые входь: элементов И Г7 и J9 - через элемент НЕ 14 (т,е. и55Еертирозанный) с

И при постушшнии третьего тактового сигнала (синхросигнала) СиЗ по входу 1 устройства, на третьи входы всех элементов И на выходах элементов И 6-18 подтверждаются сигналы логи- ческого нуля, т.е. по KpaiiHeH- мере на одном из вход|; в .каждого из этих элементов присутствует сигнал логического нуля 5 а на выходе элемента И 19. устанавливается сигнал логической eдиниIJ 5 s так как на. всех его входах присутствуют сигналы логической единицы Причем длительность этого сигнала логической единицы равна длитель- ности тактового сигнала СиЗо

Следовательно, на выходе элемента ИЛИ. 21 устанавливается также сигнал логической единицы, которьй через элемент НЕ 6, т.,е, инвертированный, поступает на вход С разрешения записи и загшсывает содержимое выхода блока

5пш шти по входу D в счетчик 4 адреса, которое поступает далее на вход блока 1 памяти. При этом вьзходное состояние счетчика 4 адреса представляет собой a/ipec операционной части

i,

514

едующей микрокоманды, по которому в блоке памяти выбирается соответст- 1ующая этому адресу линейка с закодиро- I анной в ней операционной частью следую- П1ей микрокоманды. Содержимое этой линейки поступает на информационные I ходы D регистра 2 микрокоманд и счётчика 4 адреса,

С поступлением следующего тактового сигнала Си1 по входу 8 устройства на вход С параллельной записи регистра 2 микрокоманд содержимое выхода (шока памяти переписывается в ре- 1 истр 2 микрокоманд, т.е. на выход ре : истра 2 поступает для исполнения (следующая микрокоманда (ее операцион- ая часть),

Аналогично работает устройство и зо втором состоянии: на выходе муль- гиплексора 3 условий и выходе П, регистра 2 микрокоманды присутствуют сигналы логического нуля.

При этом, так как выполняемая ми-. крокоманда условная, состояние выхода П регистра 2 микрокоманд - логичес- ая единица, означающая необходимость формирования третьего тактового, сигг |нала СиЗ в устройство согласно времен |ной диаграмме (фиг.2).

; С поступлением второго тактового |сигнала Си2, поступающего через эле- iMeHT ИЛИ 20 на вход +1 счетчика 4 Iадреса, состояние последнего увеличи- вается на единицу, т.е. на выходе I счетчика 4 (следовательно, на входе блока) устанавливается выходное сос- ;тояние, представляющее собой увеличенный на ,1 адрес выполняемой условной микрокоманды. По этому адресу в блоке 1 памяти выбирается соответствующая ему линейка, содержимое которой поступает на информационные входы D регистра 2 микрокоманд и счетчика 4 адреса.

При этом сигнал логического нуля с выхода мультиплексора 3 условий поступает на один из входов элементов И 16 и 19 непосредственно, а на-один из входов элементов И 17 и 18 - через элемент НЕ 15 (т.е. инвертированный, равный лог. I). А сигнал логического нуля с выхода И регистра 2 микрокоманд поступает на вторые входа элементов И 17 и 19 непосредствен - но, а на вторые входы элементов И 16 и 18 - через элемент НЕ 14 (т.е. ин, вертированный, равный лог. 1). И при поступлении третьего тактового

9

5

0

5 0

g g

5

0

5

1146

сигнала СиЗ по входу 11 устройства на третьи входы всех элементов И - на входах элементов И 16, 17 и 19 подтверждается сигнал логического нуля, так как на одном из входов этих элементов присутствует сигнал логической единицы, так как на всех его входах присутствуют сигналы логической единицы.

Длительность этого сигнала равна длительности сигнала СиЗ, Сигнал логической единицы с выхода элемента И 18 поступает через элемент ИЛИ 21 и элемент НЕ 6 (т,е, инвертированный) на вход С параллельной записи счетчика 4 адреса, записьшая информацию с выхода блока 1 памяти в счетчик 4 адреса и на вход блока 1.

При этом выходное состояние счетчика 4 адреса представляет собой адрес операционной части следующей микрокоманды, по которому в блоке 1 памяти выбирается соответствующая этому адресу линейка с закодированной в ней операционной частью следующей микрокоманды. Содержимое этой линейки поступает на информационные входы D регистра 2 микрокоманд и счетчика 4 адреса,

С поступлением следующего тактового сигнала Си1 (согласно временной диаграмме на фиг.2) по входу 9 устройства на вход С параллельной записи регистра 2 микрокоманд содержимое выхода блока 1 памяти переписывается в регистр 2 микрокоманд, т,е. на выход регистра 2 поступает для исполнения следующая микрокоман-. да (ее операционная часть).

Таким образом, формирование адреса следующей микрокоманды при наличии однозначных сигналов на выход мультиплексора 3 условий и на выходе П, регистра 2 микрокоманд осуществляется следующим образом: адрес выпол- . няемой условной микрокоманды увеличивается на единицу, и полученный таким образом новый адрес является адресом адресной части следующей микрокоманды, которая по СиЗ записывается в счетчик 4- адреса и по которой в блоке 1 памяти выбирается операционная часть этой следующей микрокоманды.

Смена микрокоманд в регистре 2 происходит по Си1, а длительность машинного цикла (микрокоманды) равна в этом случае в устройстве трем тактовым сигналам: Си1, Си2 и СиЗ,

Рассмотрим работу устройства в третьем состоянии: на выходе мультиплексора 3 условий - логическая единица (условие условий - логичес- кая единица(условие выполняется), ,а на выходе Пг регистра 2 микрокоманд - логический нуль,

Так как выполняемая команда, т.е. микрокоманда, выбранная в блоке 1 па- мяти и переписанная по Си I в регистр 2 микрокоманд условная, то состояние выхода n,f регистра 2 микрокоманд - логическая единица, означающая необходимость формирования третьего такто- вого сигнала СиЗ в соответствии с приведенной на фиг.2 временной диаграммой.

С поступлением второго тактового сигнала Си2 по входу 10 устройства на один из входов элемента PfflH 20 сигнал логической единища с выхода этого элемента поступает на вход I счетчика 4 адреса и увеличивает его содержимое (адрес выполняемой микро- комадды).на единицу.

Сигнал логической единицы с выхода мультиплексора 3 условий поступает на первые входы элементов И 16 и 19 непосредственно, а на первые входы элементов И 17 и 18 - через элемент НЕ 15, т.е. инвертированный, равный лог. О.

Сигнал логического нуля с вьпсода П регистра 2 микрокоманд поступает н вторые входы элементов И 17. и 19 не-, посредственно, а на вторые входы элементов И 16, 18 - через элемент НЕ 14 т.е. инвертированный, равный лог. I

И при поступлении третьего такто-. вого сигнала СиЗ по входу II устройства на третьи выходы элементов И 16- 19 на выходах элементов И 17-19 подтверждаются сигналы логического нуля, так как не на всех их входах присут- ствуют сигналы логической единицы, а на выходе элемента И 16 устанавливается сигнал логической единицы, так как на всех его входах присутствуют сигналы логической единицы,

Сигнал .логической единицы с выхода элемента И 16 через элемент ИЛИ 20 поступает на вход +1 счетчика 4 адреса и увеличивает его содержимое (увеличенный на 1 адрес выполняемой микрокоманды) еще на единицу.

Полученный таким образом адрес, представляющий собой увеличенный на два адреса выполняемой микрокоманды.

является адресом следующей микрокоманды, 11с этому адресу в блоке 1 па- мяти вытирается соответствун щая ему линейка с закодированной в ней следущей микрокомандой (операционной ее частью), которая затем (с поступлением следующего тактового сигнала Си1 в соответствии с временной диаграммо (фиг.2) переписывается в регистр 2 микрокоманд для выполнения.

Аналогично работает устройство в четвертом состоянии: на выходе мультиплексора условий - сигнал логического. нуля (т,е, условие не выполняется) и на выходе П регистра 2 адреса сигнал логической единицы.

Так как.выполняемая микрокоманда условная, состояние выхода регистра 2 микрокоманд - логическая единица, и в устройстве (на входе 11) в соответствии с временной диаграммой (фиг.2) появляется третий тактовый сигнал СиЗ - на выходе элемента И 7 появляется сигнал логической единицы

С поступлением второго тактового сигнала Си2 по входу Ю. устройства, на один из входов элемента ИЛИ 20 синал логической единицы с выхода этого .элемента поступает на вход +1 счетчика 4 адреса и увеличивает его содержимое X адрес выполняемой микрокоманды) на единицу.

Сигнал логического нуля с выхода мультиплексора 3 условий поступает на первые входы элементов .И i6 и 19 непосредственно, а на первые входы элементов И 17 и i 8 - через элемент НЕ 15 (т,е, инвертированный)

Сигнал логической единицы с выхода IIj регистра 2 микрокоманд поступает на вторые входы элементов И 17 и 19 непосредственно., а на И 16 и 18 - через элемент НЕ 14, т.е. инвертиро- ванньй,

И при поступлении третьего такто- вого сигнала СиЗ по входу 1I устройства на третьи входы элементов И 16- 19 на выходах элементов И 16, 18 и

19подтверждаются сигналы логического нуля, а на выходе элемента И 17 - сигнал логической единицы.

Сигнал логической единицы с выхо- да элемента И 17 через элемент ИЛИ

20поступает на вход +1 счетчика

4 адреса, увеличивая его содержимое (увеличенный на единицу адрес выполняемой микрокоманды) еще на единицу.

i9

1олученный таким образом.адрес, пре|дставляющнй собой увеличенный на дв4 адрес выполняемой микрокоманды, является адресом следующей микроко- , По этому адресу выбирается в локе 1 памяти соответствующая ему линейка с закодированной в ней сл1;дующей микрокомандой, операцион- на 1 часть которой затем (с поступле- ниам следующего тактового сигнала Си1 в соответствии с временной диаграммой) переписывается в регистр 2 микрокоманд для выполнения.

i Таким образом, формирование адре- са следующей микрокоманды при наличии разноименных сигналов на выходе мультиплексора 2 условий и на выходе п регистра 2 микрокоманд осуществля ется путем увеличения на два адреса вдоолняемой условной микрокоманды.

i Смена микрокоманд в регистре 2 происходит по Си1, а длительность ма цщнного цикла (микрокоманды) равна Э этом случае в устройстве также тре тгактовым сигналам Си 1, Си2-, СиЗ.

формула изобретения

I Микропрограммное устройство управ- пения, содержащее блок постоянной 1амяти, cчeтчиk адреса, регистр ми- крокоманд, мультиплексор условий и блок управления .следующим адресом, 35 причем информационный и адресный . входы мультиплексора условий соединены соответственно с входом условий устройс.тва и выходом поля кода условия, регистр микрокоманд, синхровход, 40 информационный вход и выход поля кода микроопераций которого соединены соответственно с первым синхровходом устройства, выходом полей кода микроопераций и кода типа перехода блока 45 постоянной памяти и выходом микроопераций устройства, информационный вход, выход и вход сброса счетчика адреса соединены соответственно с выходом поля кода адреса, адресным входом gg блока постоянной памяти и входом запуска устройства, второй и третий синхровходы устройства соединены соответственно с первым и вторым синхро- входами блока управления следующим 55

14

10

5 0

5

0

5 0 5 g 55

адресом, адресный вход которого сое- динен с выходом мультиплексора условий, первьш и второй выходы блока управления, следующим адресом условий соединены соответственно со счетным входом и входом разрешения записи счетчика адреса, отличающее- с я тем, что, с целью сокращения объема памяти за .счет реализации друх путей формирования адреса следующей микрокоманды с возможностью выбора оптимального пути на каждой условной микрокоманде, вход кода типа перехода блока управления следующим адресом .соединен с одноименным выходом регистра микрокоманд, причем блок управления следующим адресом содержит с первого по третий элементы НЕ, с первого по пятый элемент И, первый и второй элементы ИЛИ, причем выходы первого и второго элементов ИЛИ соединены соответственно с первым выходом блока управления следующим адресом и входом .первого элемента НЕ-, выход которого соединен с вторым выходом блока управления следующим адресом, первый и второй синхровходы которого соединены соответственно с первыми входами первого элемента ИЛИ и первого элемента И, второй вход которого соединен со старшим разрядом входа кода типа перехода блока управления следующим адресом, второй и третий входы первого элемента ИЛИ соединены соответственно с выходами второго и третьего элементов И, -выходы четвертого и пятого элементов И соединены соответственно с . первьш и вторым входами второго элемента ИЛИ, первые входа: второго и пят того элементов И соединены с входом третьего элемента НЕ и с адресным входом блока управления следующим адресом, младший разряд входа кода типа перехода которого соединен с входом второго элемента НЕ и вторыми входами третьего и пятого элементов И, выход второго элемента НЕ соединен с вторыми входами второго и четвертого элементов И, выход третьего элемента НЕ соединен с первыми входами третьего и четвертого элементов И, третьи входы с второго по пятьй элементов И соединены с выходом первого элемента И.

jirnmrjiJTrmnjnjiTLJTJiJiJ п п п п п

jr.Jlf Вх.Ю

П п п- л п

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1304021A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1304022A1 |

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| Микропрограммное устройство управления (его варианты) | 1984 |

|

SU1159020A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1293729A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Микропрограммное устройство управления | 1984 |

|

SU1275441A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

Изобретение относится к микро- пpoгpa c нoмy управлению и наиболее эффективно при использовании микрокоманд с соизмеримыми адреснь ми и опе- операционными частями. Цель изобретения - сокращение объема памяти за счет реализащш двух путей формирования адреса следующей микрокоманды с возможностью выбора оптимального пути на каждой условной микрокоманде Предлагаемое, устройство содержит блок 1 постоянной памяти, регистр 2 шшрокоманд, г-гультиплексор 3 условий, счетчик 4 адреса, блок 5 управ- ления следующим адресом. 2 ил. , в fCij}

Вш.э/.и

п п п

Bj(.8(H.3)

fL

9иг.2

| Майоров С.А., Новиков Г.И | |||

| Принципы организации цифровых машин.- Л.: Машииостроение, 1974, с, 2J6, рис.69 Авторское свидетельство СССР 1242943, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-27—Подача