Изобретение относится к микропрограммному управлению и может быть использован в вычислительной технике, например в ЭВМ, при построении управляющих систем, а также самостоятельных микропрограммных автоматов с микрокомандами, адресные и операционные части которьгх соизмеримы по разрядности.

Цель изобретения - повышение быстродействия .

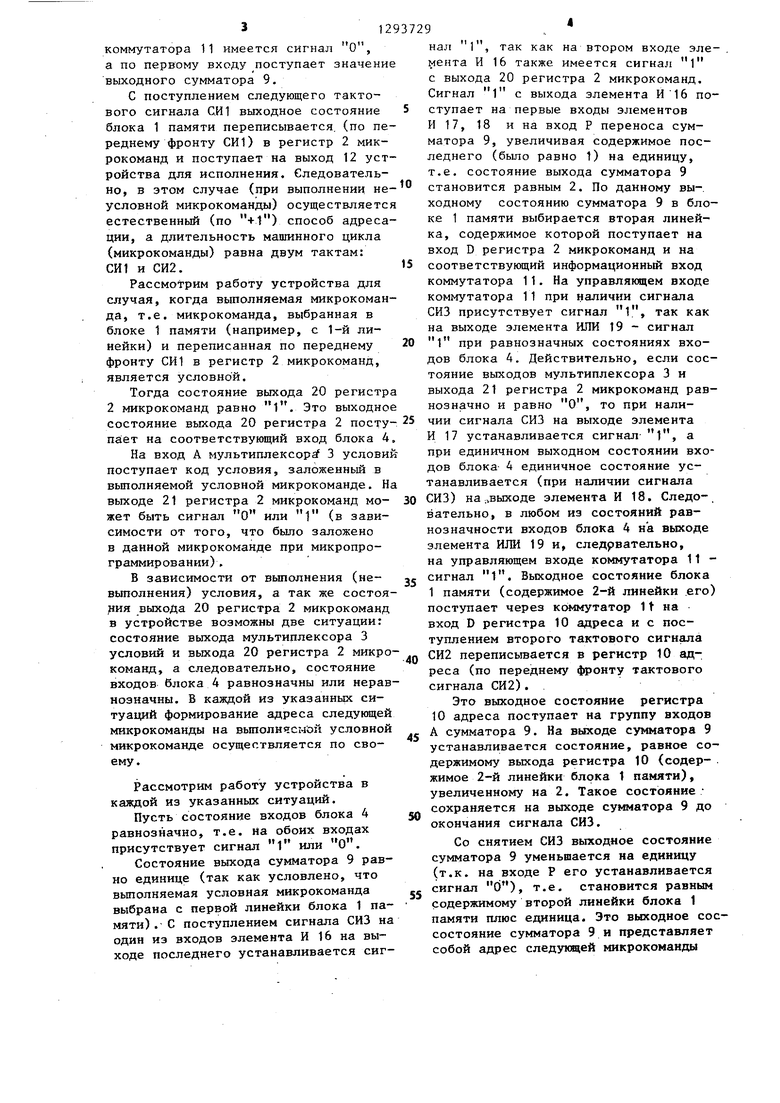

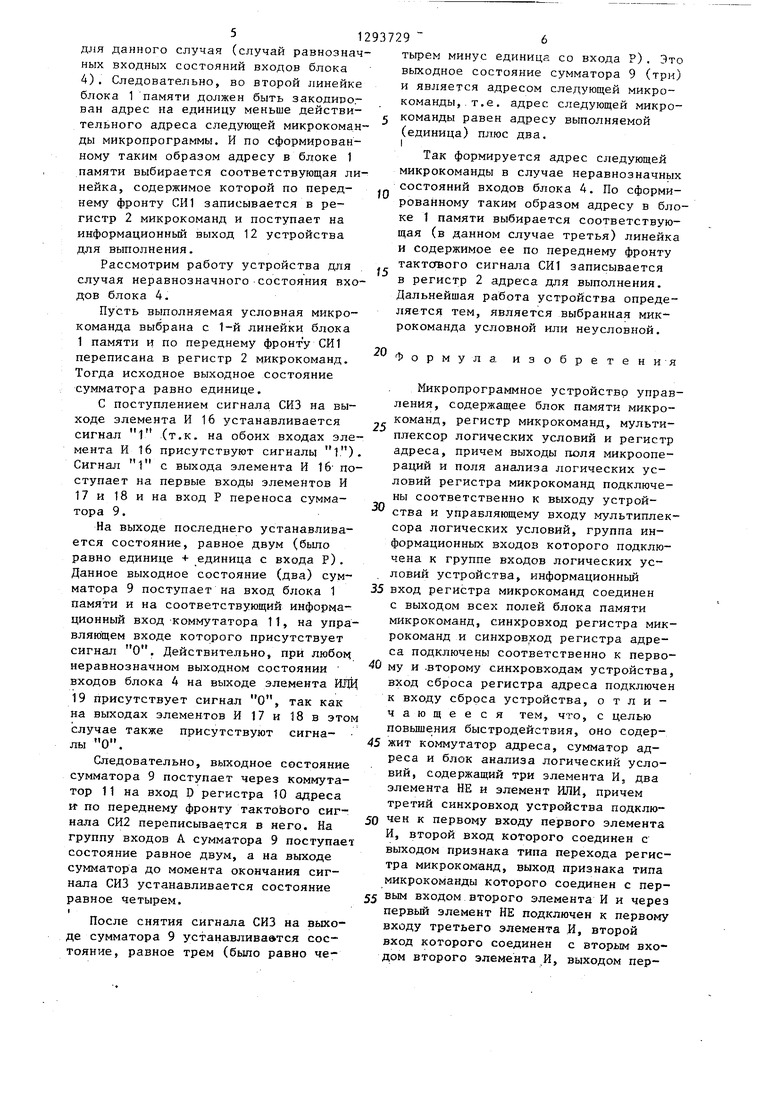

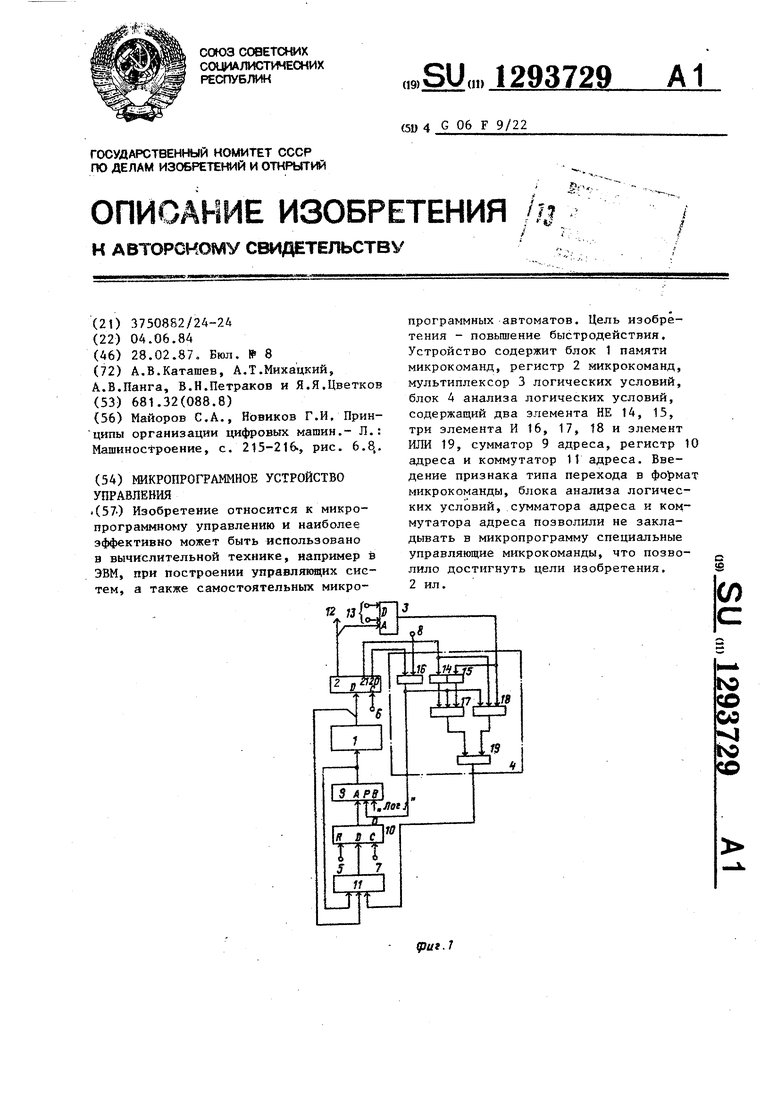

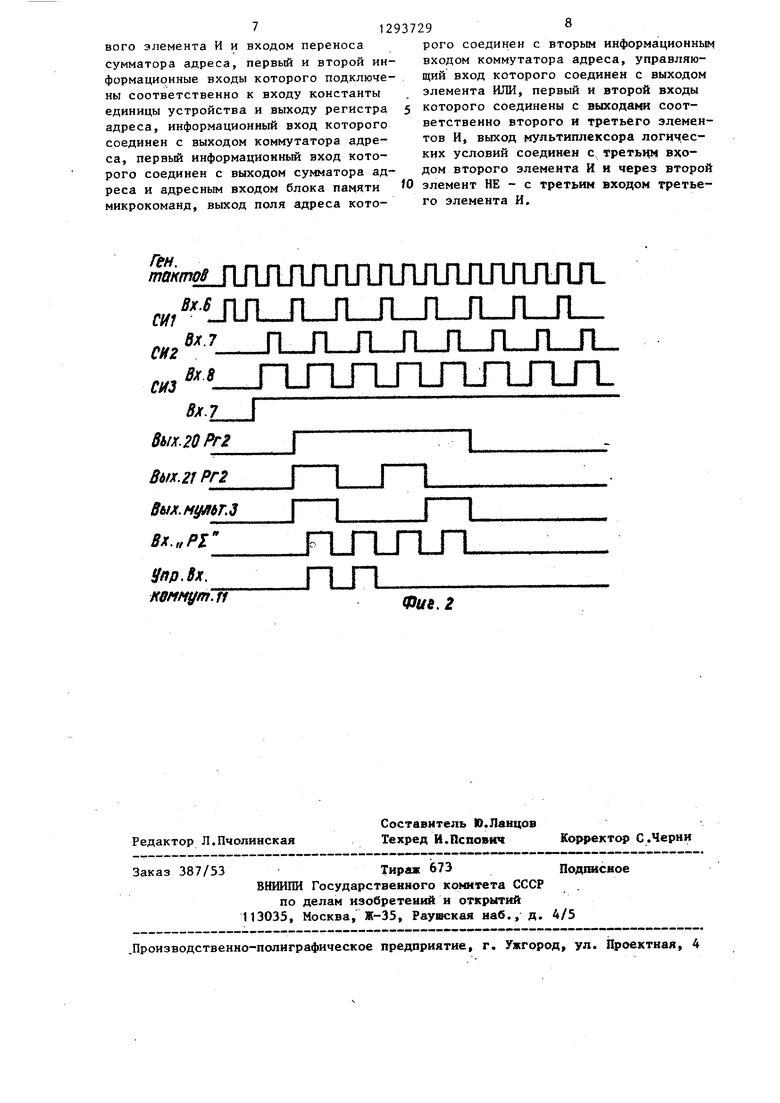

На фиг.1 представлена функциональная схема микропрограммного устройства управления; на фиг.2 - временные диаграммы его функционирования.

Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, мультиплексор 3 логических условий, блок 4 анализа логических условий, вход 5 сброса, первый 6, второй 7, и третий 8 синхровходы, сумматор 9 адреса, регистр 10 адреса, коммутатор t1 адреса, выход 12 и группу 13 входов логических условий,

Блок анализа логических условий содержит два элемента НЕ 14 и 15, - три элемента и 16-18 и элемент ИЛИ 19.

Кроме того, регистр 2 микрокоманд имеет выход 20 признака типа перехода и выход 21 признака типа микрокоманды .

Устройство работает следующим образом.

Пги поступлении сигнала начальног запуска по входу 5 устройства регист 10 адреса устанавливается в исходное нулевое состояние, поступаиидего на группу входов А сумматора 9, следовательно, на выходе сумматора 9 устанавливается выходное состояние равно единице поскольку на младшем разряде группы входов В - I, а на входе Р О), так как на выходе элемента И 1 присутствует сигнал О (на обоих входах этого момента - сигналы О в данный мом-ент) . На управляющем входе коммутатора II также присутствует сигнал О, и, следовательно, выход коммутатора 11 через свой первый информационный вход подключен к выходу сумматора 9, выходное состояние которого равно единице. Данное выходное состояние сумматора 9 поступает на вход блока 1 памяти, В результате на вьжоде блока 1 памяти устанавливается содерж1-шое первой его линейки поступающее с выхода блока I памяти на вход D регистра 2 микрокоманд и

на информационный вход коммутатора 115 но не проходит на выход последнего.

В момент запуска устройство синхронизации (не показано) вырабатывает только серию первых тактовых сигналов СИ1, поступающих на вход 6 устройства, соединенный с входом С регистра 2 микрокоманд. Передним фронтом тактового сигнала СИ1 содержимое блока 1 памяти переписывается в регистр 2 микрокоманд и поступает на выход 12 устройства для исполнения. Сигнал СИЗ 5 вырабатываемый устройством синхронизации, равен в данный момент о.

Пусть микрокоманда, выбранная с первой линейки блока 1 памяти и переписанная по переднему фронту СИ1 в

регистр микрокоманд, т.е. выполняемая микрокоманда, неусловная. Тогда состояние выхода 20 регистра 2 микрокоманд равно О, Независимо от состояния выхода мультиплексора 3 услоВИЙ и выхода 21 регистра 2 микрокоманд на входе Р переноса сумматора 9 и на управлякицем входе коммутатора 11 присутствуют сигналы, т.е. на первом и втором выходах блока

сигналы О,

4

При снятии сигнала начального запуска с входа 5 устройство синхронизации начинает вырабатывать (после прохождения сигнала СИ1) сигнал СИЗ, с поступлением которого в этот момент состояние выходов блока 4 не изменяется.

С поступлением сигнала СЙ2, состояние выхода сумматора 9 (единица) ., переписывается (передним фронтом СИ2) через коммутатор 11 в регистр ТО адреса, т.е. на выходе регистра 10 адреса устанавливается единичное выходное состояние, которое поступает на группу входов А сумматора 9. На выходе последнего устанавливается состояние равное двум (единица с группы входов А плюс единица с младшего разряда группы входов В),

В результате по выходному состоянию сумматора 9 а блоке 1 памяти выбирается вторая линейка, содержимое которой поступает с выхода блока 1 памяти .на вход D регистра 2 микроко- манд и на соответстшующий информационный вход коммутатора 11, Однако на выходе коммутатора 11 это состояние выхода блока 1 памяти пройти не может, так как на управляющем входе

коммутатора 11 имеется сигнал О,

а по первому входу поступает значение

выходного сумматора 9.

С поступлением следующего тактового сигнала СИ1 выходное состояние блока 1 памяти переписывается, (по переднему фронту СИ1) в регистр 2 микрокоманд и поступает на выход 12 устройства для исполнения. Следователь- но, в этом случае (при выполнении неусловной микрокоманды) осуществляется естественный (по +1) способ адресации, а длительность машинного цикла (микрокоманды) равна двум тактам: СИ1 и СИ2,

Рассмотрим работу устройства для случая, когда выполняемая микрокоманда, т.е. микрокоманда, выбранная в блоке 1 памяти (например, с 1-й линейки) и переписанная по переднему фронту СИ1 в регистр 2 микрокоманд, является условной.

Тогда состояние выхода 20 регистра 2 микрокоманд равно l. Это выходное состояние выхода 20 регистра 2 посту- пает на соответствующий вход блока 4.

На вход А мультиплексора 3 условий поступает код условия, заложенный в выполняемой условной микрокоманде. На выходе 21 регистра 2 микрокоманд может быть сигнал О или 1 (в зависимости от того, что было заложено в данной микрокоманде при микропрограммировании) .

В зависимости от выполнения (невыполнения) условия, а так же состоя- 1ия выхода 20 регистра 2 микрокоманд в устройстве возможны две ситуации: состояние выхода мультиплексора 3 условий и выхода 20 регистра 2 микрокоманд, а следовательно, состояние входов блока 4 равнозначны или неравнозначны. В каждой из указанных ситуаций формирование адреса следующей микрокоманды на вьшолнясы&й условной микрокоманде осуществляется по своему.

Рассмотрим работу устройства в каждой из указанных ситуаций.

Пусть состояние входов блока 4 равнозначно, т.е. на обоих входах присутствует сигнал 1 или О .

Состояние выхода сумматора 9 равно единице (так как условлено, что вьшолняемая условная микрокоманда выбрана с первой линейки блока 1 па- мяти). С поступлением сигнала СИЗ на один из входов элемента И 16 на выходе последнего устанавливается сиг

5

0

5

0

5

0

g

нал , так как на втором входе эле-. мента И 16 также имеется сигнал 1 с выхода 20 регистра 2 микрокоманд. Сигнал 1 с выхода элемента И 16 поступает на первые входы элементов И 17, 18 и на вход Р переноса сумматора 9, увеличивая содержимое последнего (было равно 1) на единицу, т.е. состояние выхода сумматора 9 становится равным 2. По данному выходному состоянию сумматора 9 в блоке 1 памяти выбирается вторая линейка, содержимое которой поступает на вход D регистра 2 микрокоманд и на соответствующий информационный вход коммутатора 11. На управляющем входе коммутатора 11 при наличии сигнала СИЗ присутствует сигнал 1., так как на выходе элемента ИЛИ 19 - сигнал l при равнозначных состояниях входов блока 4. Действительно, если состояние выходов мультиплексора 3 и выхода 21 регистра 2 микрокоманд равнозначно и равно О, то при наличии сигнала СИЗ на выходе элемента И 17 устанавливается сигнал l, а при единичном выходном состоянии входов блока 4 единичное состояние устанавливается (при наличии сигнала СИЗ) на .«выходе элемента И 18. Следо-. вательно, в любом из состояний равнозначности входов блока 4 на выходе элемента ИЛИ 19 и, следовательно, на управляющем входе коммутатора 11 - сигнал 1. Выходное состояние блока 1 памяти (содержимое 2-й линейки его) поступает через коммутатор 1t на вход D регистра 10 адреса и с поступлением второго тактового сигнала СИ2 переписьгеается в регистр 10 адреса (по переднему фронту тактового сигнала СИ2).

Это выходное состояние регистра 10 адреса поступает на группу входов А сумматора 9. На выходе сумматора 9 устанавливается состояние, равное содержимому выхода регистра 10 (содер- . жимое 2-й линейки блока 1 памяти), увеличенному на 2. Такое состояние; сохраняется на выходе сумматора 9 до окончания сигнала СИЗ.

Со снятием СИЗ выходное состояние сумматора 9 уменьшается на единицу (т.к. на входе Р его устанавливается сигнал О), т.е. становится равным содержимому второй линейки блока 1 памяти плюс единица. Это выходное сос- состояние сумматора 9 и представляет собой адрес следукяцей микрокоманды

для данного случая (случай равнозначных входных состояний входов блока 4). Следовательно, во второй линейке

блока 1 памяти должен быть закодиро.- ван адрес на единицу меньше действительного адреса следующей микрокоманды микропрограммы. И по сформированному таким образом адресу в блоке 1 памяти выбирается соответствующая линейка, содержимое которой по переднему фронту СИ1 записывается в регистр 2 микрокоманд и поступает на информационный выход 12 устройства для выполнения.

Рассмотрим работу устройства для случая неравнозначного состояния входов блока 4.

Пусть выполняемая условная микрокоманда выбрана с 1-й линейки блока 1 памяти и по переднему фронту СИ1 переписана в регистр 2 микрокоманд. Тогда исходное выходное состояние сумматора равно единице.

С поступлением сигнала СИЗ на выходе элемента И 16 устанавливается сигнал 1 (т.к. на обоих входах элемента И 16 присутствуют сигналы 1) Сигнал 1 с выхода элемента И 16- поступает на первые входы элементов И 17 и 18 и на вход Р переноса сумматора 9.

На выходе последнего устанавливается состояние, равное двум (было равно единице + единица с входа Р). Данное выходное состояние (два) сумматора 9 поступает на вход блока 1 памяти и на соответствующий информационный вход коммутатора 11, на управляющем входе которого присутствует сигнал О. Действительно, при любо1 неравнозначном выходном состоянии входов блока 4 на выходе элемента ИЩ

19 присутствует сигнал О, так как на выходах элементов И 17 и 18 в это случае также присутствуют сигналы О.

Следовательно, выходное состояние сумматора 9 поступает через коммутатор 11 на вход Р регистра 10 адреса И по переднему фронту тактового сиг нала СИ2 переписывается в него. На группу входов А сумматора 9 поступае состояние равное двум, а на выходе сумматора до момента окончания сигнала СИЗ устанавливается состояние

равное Четырем. I

После снятия сигнала СИЗ на выходе сумматора 9 устанавливаатся состояние, равное трем (было равно че0

5

0

тьфем минус единица со входа Р). Это выходное состояние сумматора 9 (три) и является адресом следующей микрокоманды, . т.е. адрес следующей микрокоманды равен адресу выполняемой

(единица) плюс два. I

Так формируется адрес следующей микрокоманды в случае неравнозначных состояний входов блока 4. По сформированному таким образом адресу в блоке 1 памяти выбирается соответствующая (в данном случае третья) линейка и содержимое ее по переднему фронту тактопвого сигнала СИ1 записывается в регистр 2 адреса для выполнения. Дальнейшая работа устройства определяется тем, является выбранная микрокоманда условной или неусловной.

Формула изобретения

5

0

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, мультиплексор логических условий и регистр адреса, причем выходы поля микроопераций и поля анализа логических условий регистра микрокоманд подключены соответственно к выходу устройства и управляющему входу мультиплексора логических условий, группа информационных входов которого подключена к группе входов логических условий устройства, информационный

5 вход регистра микрокоманд соединен с выходом всех полей блока памяти микрокоманд, синхровход регистра микрокоманд и синхровход регистра адреса подключены соответственно к перво0 му и -второму синхровходам устройства, вход сброса регистра адреса подключен к входу сброса устройства, отличающееся тем, что, с целью повыше.ния быстродействия, оно содер5 жит коммутатор адреса, сумматор адреса и блок анализа логический условий, содержащий три элемента И, два элемента НЕ и элемент ИЛИ, причем третий синхровход устройства подклю0 чен к первому входу первого элемента И, второй вход которого соединен с выходом признака типа перехода регистра микрокоманд, выход признака типа микрокоманды которого соединен с пер вым входом второго элемента и и через первый элемент НЕ подключен к первому входу третьего элемента И, второй вход которого соединен с вторым входом второго элемента И, выходом первого элемента И и входом переноса сумматора адреса, первый и второй информационные входы которого подключены соответственно к входу константы единицы устройства и выходу регистра адреса, информационный вход которого соединен с выходом коммутатора адреса, первый информационный вход которого соединен с выходом сумматора адреса и адресным входом блока памяти микрокоманд, выход поля адреса котоГен

ff i JlrlлллnллJmлJ JLГшлJL

ш UlJl JLJLJlJL fL n n

ор Л.Пчолинская 387/53

Составитель Ю.Лаыцов Техред И.Псповнч

Ко Под

Тираж 673 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113033, Москва , Раушская наб./ д. А/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3729

рого соединен с вторым информационнь|м входом коммутатора адреса, управляющий вход которого соединен с выходом элемента ИЛИ, первый и второй входы 5 которого соединены с выходами соответственно второго и третьего элементов И, выход мультиплексора логических условий соединен с третьим входом второго элемента И и через второй fO элемент НЕ - с третьим входом третьего элемента И.

Составитель Ю.Лаыцов Техред И.Псповнч

Тираж 673 венного комитета СССР

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1304022A1 |

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1304021A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1429114A1 |

| Микропрограммное устройство управления (его варианты) | 1984 |

|

SU1159020A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1275441A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для обработки данных | 1978 |

|

SU736106A1 |

Изобретение относится к микропрограммному управлению и наиболее эффективно может быть использовано в вычислительной технике, например в ЭВМ, при построении управляющих систем, а также самостоятельных микропрограммных автоматов. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, мультиплексор 3 логических условий, блок 4 анализа логических условий, содержащий два элемента НЕ 14, 15, три элемента И 16, 17, 18 и элемент ИЛИ 19, сумматор 9 адреса, регистр 10 адреса и коммутатор 11 адреса. Введение признака типа перехода в формат микрокоманды, блока анализа логических условий, сумматора адреса и коммутатора адреса позволили не закладывать в микропрограмму специальные управляющие микрокоманды, что позволило достигнуть цели изобретения, 2 ил. с (Л

| Майоров С.А., Новиков Г.И, Принципы организации цифровых машин.- Л.: Машиностроение, с | |||

| Кузнечный горн | 1921 |

|

SU215A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-28—Публикация

1984-06-04—Подача