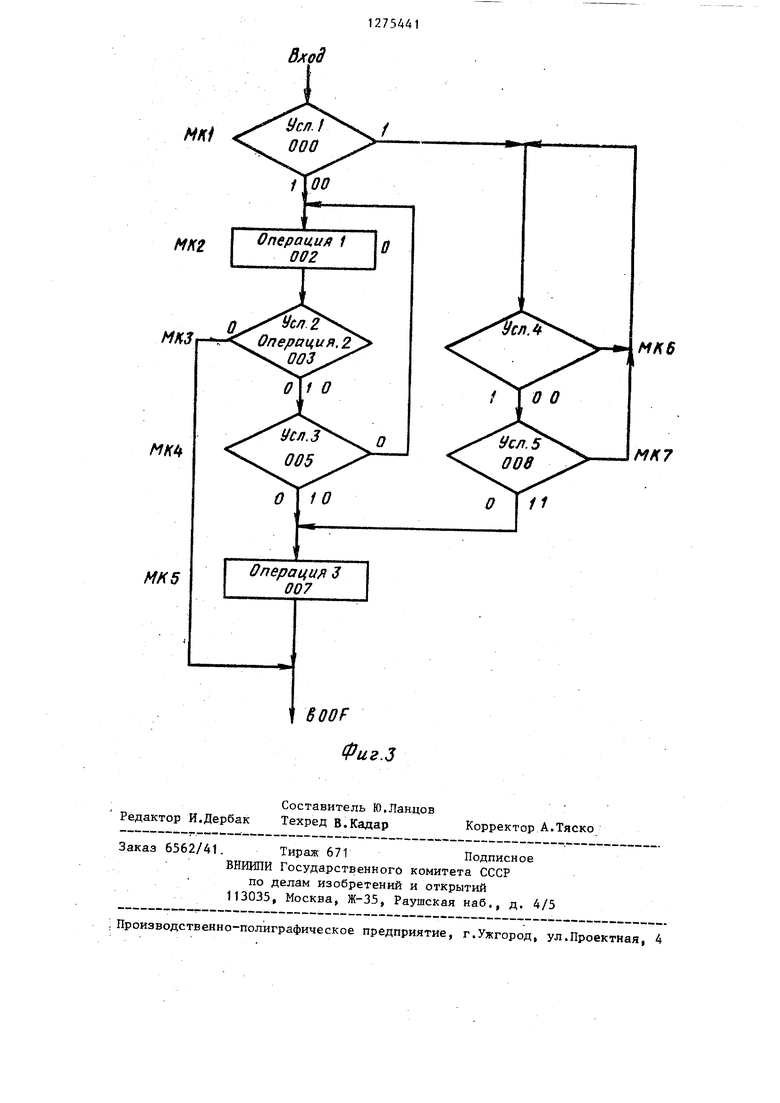

Изобретение относится к микропрог раммному управлению и наиболее эффективно может быть использовано в вычислительной технике, например в ЭВМ, при построении управляющих систем, а также самостоятельных микропрограммных автоматов. Цель изобретения повышение быстродействия. На фиг.1 представлена функциональ ная схема устройства; на фиг.2 - вре менные диаграммы, иллюстрирующие работу устройства; на фиг.З - пример заданной последовательности микрокоманд, реализуемой устройством. Устройство (фиг.1) содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, мультиплексор 3 логических условий, сумматор А, блок 5 анализа условий перехода, регистр 6 адреса, коммутатор 7 адреса, первый 8 и второй 9 входы синхронизации, вход 10 начального пуска, группу 11 входов логических условий, выход 12, третий вход 13 синхронизации. Блок 5 анализа условий перехода содержит элемент 14 равнозначности, элемент НЕ 15, третий 16, первый 17 и второй 18 элементы И и элемент ИЛИ 19. Кроме того, обозначены выход 20 признака типа микрокоманды регистра 2, второй выход 21 признака типа перехода регистра 2, первый выход 22 признака типа перехода регистра 2. Микропрограммное устройство управ ления работает следующим образом. При поступлении сигнала начального запуска по входу 10 устройства, соединенному с входом установки в ноль регистра 6 адреса, последний устанавливается в исходное нулевое состояние. Это же нулевое состояние устанавливается на выходе сумматора 4, так как на его входах В и Р присутствуют в данный момент сигналы логического нуля. По вьпсодному нулевому состоянию сумматора 4 в блоке 1 памяти выбирается соответственно нулевая линейка. При снятии сигнала начального запуска с входа. 10 устройства, устройство синхронизации (не показано) начинает вырабатываать тактовые импуль сы (при сигнале на входе 10 вырабаты ваются только тактовые сигналы). Передним фронтом первого тактового сигнала С1, йоступающего на вход параллельной записи регистра 2 микрокоманд по входу 8 устройства, первая микрокоманда микропрограммы (содержимое нулевой линейки блока 1 памяти) , поступившая с выхода блока 1 памяти на информационный вход регистра 2 микрокоманд, перепишется в последний и поступит на выход 12 устройства для выполнения (это происходит еще при наличии сигнала на входе устройства). Дальнейшая работа устройства определяется тем, что представляет собой поступившая в регистр 2 микрокоманд первая микрокоманда: является она условной или неусловной; выполняется или не вьтолняется условие; каково значение типа признака перехода, заложенного в данной микрокоманде и поступающего с соответствукщего выхода 21 регистра 2 микрокоманд на один из входов элемента 14, а также каково значение заложенного в данной микрокоманде и поступающего с выхода 22 регистра 2 микрокоманд на соответствующий вход элемента 18. Рассмотрим работу устройства для случая, когда микрокоманда (в нашем случае первая), записанная в регистр 2 микрокоманд, с нулевой линейки блока памяти неусловная. Тогда значение выходного регистра 2 микрокоманд равно логическому нулю, значение выхода 21 регистра микрокоманд и выхода мультиплексора 3 условий безразлично, а значение вЫхода 22 регистра 2 микрокоманд может иметь значение логического нуля или логической единицы. Значение выходов элементов И 16 и 17 блока 5 при поступлении синхросигнала по входу 13 устройства равно логическому нулю, так как сигнал логического нуля с выхода 20 регистра 2 микрокоманд (так как выполняемая микрокоманда неусловная) поступает на вторые входы элементов И 16 и 17. Поэтому с поступлением сигнала логической единицы по входу 13 на третьи входы элементов И 16 и 17 на выходах последних подтверждаются сигналы логического нуля. Следовательно, значение выхода элемента И 16 при выполнении неусловой микрокоманды всегда равно логическому нулю, а значение выхода эле3мента ИЛИ 19 определяется значением выхода только элемента И 18. Значение же выхода элемента И 18 определ ется конкретным значением выхода 22 регистра 2 микрокоманд, поступающим на один нз Еходов элемента И 1В, та как значение второго входа элемента И 18 при наличии синхросигнала, пос тупающего по входу 13 устройства, равно логической единице. В результате значение выхода эле мента ИЛИ 19 равно логической едини нице (при наличии синхросигнала на входе 13 устройства) при значении выхода 22 регистра 2 микрокоманд, равном логической единице, и соотве ственно, значение выхода элемента ИЛИ 19 равно логическому нулю при значении выхода 22 регистра 2 микро команд, равном логическому нулю, и путь формирования адреса следующей микрокоманды в случае выполнения неусловной микрокоманды определяетс именно значением выхода элемента ИЛИ 19, т.е. значением выхода 22 регистра 2 микрокоманд. С поступлением синхросигнала (ло гическая единица) по входу 13 устройства, соединенному со входом Р переноса сумматора 4, выходное соетояние последнего (было нулевое) увеличивается на единицу и поступает на вход блока 1 памяти и на первый информационный вход коммутатора 7. Если значение выхода 2 элемента ИЛИ 19 равно логическому нулю, то данное выходное состояние сумматора 4 (равное 1) через коммутатор 7 (по его входу 1) поступает на инфор мационный вход регистра 6 адреса и по переднему фронту синхросигнала по входу 9 перепишется в него и пос тупит на группу входов А сумматора 4. На выходе сумматора 4 (и, следовательно, на входе блока 1 памяти) установится (до момента окончания синхросигнала по входу 13) значение так как на выходе Р переноса сумматора 4 также присутствует сигнал логической единицы (синхросигнал с входа 13 устройства). С окончанием синхросигнала по входу 13 (фиг.4) на входе Р сумматрра 4, а следовательно, и на входе блока 1 памяти установится единично значение, так как при этом на входа 4414 В и Р сумматора 4 присутствует значение логического нуля. Б блоке 1 памяти выбирается первая линейка, содержимое которой поступает на информационный вход регистра 2 микрокоманд, и по переднему фронту следующего синхросигнала перепишется в него (в регистр 2) для вы полнения. Так (по +1) выбирается следующая микрокоманда в блоке 1 памяти при выполнении неусловной микрокоманды и значении выхода 22 регистра 2 микрокоманд, равном логическому -нулю. При значении выхода 22 регистра 2 микрокоманд, равном логической единице, значение выхода 2 элемента ИЛИ 19 равно логической единице (при наличии синхросигнала на входе 13 устройства). При этом значение выхода сумматора 4 равно единице, так как на входе Р его присутствует сигнал логической единицы, увеличивающий предществующее выходное значение сумматора 4 (нулевое) на единицу. По данному вы-ходному состоянию (единица) сумматора 4 в блоке 1 памяти выбирается первая линейка, содержимое которой с выхода блока 1 памяти поступает на второй информационный вход коммутатора 7. А так как значение выхода элемента ИДИ 19, соединенного с управляющим входом коммутатора 7, равно логической единице, выходное состояние блока 1 памяти (содержимое первой линейки блока 1) через коммутатор 7 поступает на информационный вход регистра 6 адреса и по переднему фронту хросигнала по входу 9 устройства перепишется в регистр 6 адреса и поступит на группу входов А сумматора 4. Данное входное состояние сумматог ра 4, после окончания синхросигнала на вход 13, проходит без изменения на его выход, и следовательно, на вход блока 1 памяти. По данному выходному состоянию умматора 4 (содержимое первой линейи блока 1 памяти), представляющему обой адрес операционной части слеующей микрокоманды, в блоке 1 памяи выбирается соответствующая линей-; а, содержимое которой (операционная асть следукнцей микрокоманды) постуает на информационный вход регистра микрокоманд и по переднему фронту следующего синхросигнала перепишется в него для выполнения. Так осуществляется выбор следующей микрокоманды при выполнении неус ловной микрокоманды и наличии сигнала логической единицы на выходе 22 регистра 2 микрокоманд. Следовательно, задавая конкретное значение выхода 22 регистра 2 микрокоманд, выбираем (по своему усмотрению) один из двух возможных в дйнном случае (при выполнении неусловной микрокоманды) путей формирования ад,реса следующей микрокоманды микропрограммы. Рассмотрим работу предлагаемого устройства для случая, когда микрокоманда, поступившая с нулевой линей ки блока памяти в регистр 2 микрокоманд для исполнения, является услов ной, т.е. значение выхода 20 регистр 2 микрокоманд равно логической единице . В этом случае в устройстве возмож ны восемь состояний в зависимости от конкретных значений выходов 21 и 22 регистра 2 микрокоманд, выхода мультиплексора 3 условий и их соотношений. Рассмотрим эти возможнью состояния, считая в каждом состоянии, что выполняемая микрокоманда является первой микрокомандой микропрограммы и считана она с нулевой линейки блока 1 памяти по. нулевому (исходному) выходному состоянию сумматора 4. В первом состоянии значение выходов 20 и 21 регистра 2 микрокоманд логическ&я единица, значение выхода 22 регистра 2 микрокоманд - логический нуль, а значение выхода мультиплексора 3 условий - логическая единица, т.е. выполняемая микрокоманда условная и условие выполняется). Тогда на выходе элемента 14 равно значности присутствует сигнал логическоЕО нуля (при равнозначных - логическая единица - входах его), который поступает на один из входов .элемента И 16 непосредственно, а на один из входов элемента И 17 - через элемент НЕ 15, т.е. инвертированный. С выхода 20 регистра 2 микроко-Манд сигнал логической единицы посту пает на вторые входы элементов И 16 и 17. СиП1ал логического нуля с выхо да 22 регистра 2 микрокоманд поступа ет на один из входов элемента И 18. И при поступлении синхросигнала по входу 13 устройства на третьи входы элементов И 16 и 17 и на второй вход элемента И 18, на выходе элемента И 16 подтвердится сигнал логического нуля, так как на его входе, соединенном с выходом элемента 14, присутствует сигнал логического нуля, а на выходе элемента И 17 - сигнал логической единицы, так как на всех его входах присутствуют сигналы логической единицы. На выходе элемента И 18 подтвердится состояние логического нуля. Сигнал логической единицы с выхода элемента И 17 через элемент ИЛИ 19 поступает на выход элемента ИЛИ 19, соединенный с управляющим входном коммутатора 7. В результате выход последнего переключается на свой второй информационный вход, соединенный с выходом блока 1 памяти. Одновременно с поступлением синхросигнала по входу 13 устройства на входе Р параллельной записи сумматора 4 выходное состояние последнего (равное нулю) увеличивается на единицу, т.е. становится равным 1 (так как на младшем разряде группы входов В сумматора при этом сигнал логического нуля с выхода элемента И 16), По данному (единица) выходному состоянию сумматора 4, поступающему на вход блока 1 памяти, в последнем выбирается первая линейка, содержимое которой через второй информационный вход коммутатора 7 поступает на его выход (так как на его управляющем входе сигнал логической единицы), и следовательно, на информационный вход регистра 6 адреса. По переднему фронту синхросигнала, поступающего по входу 9 устройства на вход параллельной записи регистра 6 адреса, данное содержимое первой линейки блока 1 памяти перепишется в регистр 6 и поступит на группу входов А сумматора 4. На выходе последнего и, следовательно, на входе блока 1 памяти уста-новится состояние, равное значению выхода регистра 6 адреса (содержимое 1-й линейки блока 1 памяти) плюс 1 (так как значение входа Р переноса сумматора 4 при наличии синхросигнала на входе 13 - логическая единица) . Со снятием синхросигнала по входу 13 на входе Р сумматора 4 установит-. ся сигнал логического нуля и состоя ние выхода сумматора 4 станет равным состоянию входов группы А его, т.е. состоянию выхода регистра 6 адреса (содержимое первой линейки блока 1) которое и является адресом следующей ;микрокоманды микропрограммы. По нему в блоке 1 выбирается соответствующая линейка, содержимое которой по перед нему фронту синхросигнала перепишет в регистр 2 микрокоманд для выпол; , нения. Следовательно, адрес следующей микрокоманды микропрограммы в данном состоянии устройства должен быть равен адресу выбираемой микрокоманды. Во втором состоянии значение выхода 20 регистра 2 микрокоманд - логическая единица, значение выходов 21 и 22 регистра 2 микрокоманд и зна чение выхода мультиплексора 3 условий - логический нуль, т.е. выполняе мая микрокоманда условная и условие не выполняется. Значение выхода элемента 14 равно значности - логический нуль (так как на обоих его входах присутствуют равнозначные сигналы логического нуля) . В результате на первом входе элемента И 16 - сигнал логического нуля, а на первом входе элемента И .17 - сигнал логической единицы. . Сигнал логической единицы с выхода 20 регистра 2 микрокоманд поступа ет на вторые входы элементов И 16 и 17, а сигнал логического нуля с вы-. хода 22 регистра 2 микрокоманд - на первый вход элемента И 18. Поэтому с поступление синхросиг нала по входу 13 на третьи входы эле ментов И1би17ина второй вход элемента И 18 на выходах элементов И 16 и 18 подтвердится сигнал логического нуля, а на выходе элемента И 17 - сигнал логической единицы. Далее работа аналогична, описанной в первом состоянии. В третьем состоянии значение выходов 20 и 21 регистра 2 микроко- , манд - логическая единица, значение выхода 22 регистра 2 микрокоманд и выхода мультиплексора 3 условий логический нуль. Значение выхода элемента 14 равнозначности равно в этом случае (при неравнозначных входах) логической единице, следовательно, на перво входе элемента И 16 присутствует сиг нал логической единицы, а на первом входе элемента И 17 - сигнал логического нуля. На вторых входах элементов И 16 и 17 присутствует сигнал логической единицы с выхода 20 регистра 2 микрокоманд, ка первом входе элемента И 18 - сигнал логического нуля с выхода 22 регистра 2 микрокоманд. Поэтому с поступлением синхросигнала по входу 13 на входы элементов И 16 и 17 и на вход элемента И 18 на выходе элемента И 16 устанавливается сигнал логической единицы, а на выходах элементов И 17 и 18 - сигнал логического нуля. Следовательно, на выходе элемента И 16 - сигнал логической единицы, а на выходе элемента ИЛИ 19 - сигнал логического нуля, т.е. на управляющем входе комм татора 7 - сигнал логического нуля, подтверждающий подключение его выхода на, собственный первый информационный вход, соединенный с выходом сумматора 4. При этом значение выхода сумматора 4 при наличии синхросигнала по входу 19 равно 2, так как на младшем разряде группы входов В и входе Р сумматора присутствуют сигналы логической единицы, а исходное состояние сумматора 4 принято равным нулю. Данное выходное состояние сумматора 4 поступает через коммутатор 7 (так как на его управляющем входе сигнал логического нуля) на информационный вход регистра 6 адреса, по переднему фронту синхросигнала на вход 13 перепишется в него и поступит на группу входов А сумматора 4, так как этот синхросигнал еще присутствует на его входах Р и В, то на выходе сумматора 4 установится значе:г ние, равное выходному состоянию т f гистра 6 адреса (2) , I.e. станет равно 4. Со снятием синхросигнала по входу на входах В и Р сумматора установятся сигналы логического нуля и на выходе сумматора 4 установится значение, равное выходному состоянию регистра 6 адреса, т.е. 2, являющееся адресом следующей микрокоманды в том : состоянии. По данному выходному состоянию сумматора 4 в блоке 1 памяти выбирается вторая линейка, содержиое которой (операционная часть слеующей микрокоманды) поступает на информационный вход регистра 2 микро команд и по переднему фронту следующего синхросигнала (вход 8 устройства) переЬисывается в него для выполкения. Следовательно, в данном состоянии операционная часть следующей микрокоманды кодируется в линей.ке блока 1 памяти с адресом, равным адресу выполняемой микрокоманды плюс 2. В четвертом состоянии значение вы хода 20 регистра 2 микрокоманд - логический нуль, значение выхода мультиплексора 3 условий - логическая единица. Значение выхода элемента 14 равно значности в этом случае (неравнознач ные входы) равно логической единице. Далее работа аналогична, описанной в третьем состоянии. В пятом состЪянии значение выходо 20-22 регистра 2 микрокоманд и выход мультиплексора 3 условий - логическая единица. Так как значение выхода 22 .регистра 2 микрокЪманд равно логи ческой единице, то адрес следующей микрокоманды будет формироваться путем считывания содержимого линейки блока 1 памяти в регистр 6 адреса через соответствующий вход коммутатора 7. Значение выхода 21 регистра 2 мик рокоманд и выхода мультиплексора 3 условий равнозначны и равны логической единице. Отсюда выход элемента равнозначности равен логическому нулю, который поступит на первый вход элемента И 16, а через элемент НЕ 15 уже как сигнал логической единицы поступит / на вход элемента И 17. Поэтому при поступлении синхросиг ,нала на вход 13 устройства на выходе элемента И 16 подтвердится значение логического нуля, а на выходах элементов И 17 и 18 установится значе: ние логической единицы. Таким образом, через элемент ШШ 19 коммутатор 7 пропустит через себя содержимое выхода линейки блока 1 па На вькоде сумматора 4 с поступле : нием синхросигнала по входу 13 сформируется значение, равное единице. Таким образом в регистр 6 адреса с поступлением переднего фронта синхро сигнала по входу 9 устройства перепишется Содержимое первой линейки блока 1 памяти, которое является адресом следующей-микрокоманды (ее операционной части). В шестом состоянии значение выходов 20 и 22 регистра 2 микрокоманд логическая единица, значение выхода 21 регистра 2 микрокоманд и выхода мультиплексора 3 условий - логический нуль. Работа устройства в этом . состоянии аналогична описанной в пятом состоянии. Формирование адреса следующей мик рокоманды в пятом и шестом состояниях устройства аналогично тому, как это осуществляется в известном устройстве, хотя и присутствует новый признак - признак безусловного перехода (выход 22 регистра 2 микрокоманд, равный логической единице). В седьмом состоянии значение выходов 20-22 регистра 2 микрокоманд логическая единица, значение выхода мультиплексора 3 условий - логический нуль. При поступлении синхросигнала (вход 13 устройства) на выходах элементов И 16 и 18 установится логическая единица, на выходе элемента И 17 подтвердится значение логического нуля. В результате этого на выходе сумматора 4 сформируется значение, равное 2. В блоке 1 памяти будет выбрана соответственно вторая линейка, содержимое которой через соответствующий вход коммутатора (на управляющем входе коммутатора 7 значение логической единицы с выхода И 18 и ИЛИ 19) поступит на информационный вход регистра 6 адреса и передним фронтом синхросигнала по выходу 9 устройства перепишется в регистр 6 адреса. С уходом синхросигнала по входу 13 на выходе сумматора 4 установится адрес следующей микрокоманды, который был считан с второй линейки блока 1 памяти. В восьмом состоянии значение выходов 20 и 22 регистра 2 микрокоманд и значение выхода мультиплексора 3 условий - логическая единица, а значение выхода 21 регистра 2 микрокоманд - логический нуль. Работа устройства в этом состойнии аналогична работе его в седьмом состоянии. Формула изобретения Микропрограммное устройство управ ления, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, сумматор, мультиплексор логических условий, причем группа выходов регистра адреса подключена к первой группе информационных входов сумматору, информационные входы стар ших разрядов второй группы которого подключены к шине нулевого потенциала устройства, выход сумматора соединен с адресным входом блока памяти микрокоманд, выход поля микроопераций которого подключен к выходу устройства, выход поля проверки условий регистра микрокоманд соединен с управляющим входом мультиплексора логи ческих условий, группа информационных входов которого подключена к группе входов логических условий уст ройства, первый, второй входы синхронизации устройства подключены соответственно к входам синхронизации регистра микрокоманд и регистра адре са, вход установки в ноль которого .соединен с входом начального пуска устройства, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит коммутатор адреса и блок анализа условий переходов, содержащий три эле.менуа И, элемент НЕ, элемент ИЛИ и 1 ГП44112элемент равнозначности, причем информационный вход регистра адреса соединен с выходом коммутатора адреса, первый и второй информационные входы которого соединены соответственно с выходами блока памяти микрокоманд и сумматора, управляющий вход коммутатора соединен с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, пер-; вые входы которых соединены с первым входом третьего элемента И, с входом переноса сумматора и подключены к третьему входу синхронизации устрой информационный вход младшего разряда второй группы сумматора сое выходом третьего элемента И, р которого соединен с выходом признака типа микрокоманды ре микрокоманд, первый выход признака типа перехода которого соед первым входом элемента равнозначности, второй вход которого соединен с выходом мультиплексора логических условий, второй выход признака типа перехода регистра микрокоманд соединен с вторым входом второго элемента И, выход элемента равнозначноез и соединен с третьим входом третьего элемента И и через элемент НЕ соединен с третьим входом первого элемента И. 5Ш1Г1ЯГ1ЛШ1ЛЛЛЛШШЛЯ 5:ArLJT JT Jl Jl JlJl Jl -JT-JIJI-JLJLJIJIJI п svji it/atfff I L

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1304022A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1293729A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1304021A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1429114A1 |

| Микропрограммное устройство управления (его варианты) | 1984 |

|

SU1159020A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1310816A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

Микропрограммное устройство управления относится к вычислительной технике и наиболее эффективно может быть использовано при построении управляющих систем, а также самостоятельных микропрограммных автоматов. Цель изобретения - увеличение быс тродействия. Устройство содержит блок памяти микрокоманд, регистр микрокоманд, сумматор, регистр адреса, коммутатор адреса, мультиплексор логических условий и блок анализа условий перехода с соответствующими связями. Указанная совокупность признаков позволяет достигнуть цели изобретения. 3 ил. О) С

| Майоров С.А., Новиков Г.И | |||

| Принципы организации цифровых машин | |||

| Л.: Машиностроение, 1974, с | |||

| Приспособление для подвешивания тележки при подъемках сошедших с рельс вагонов | 1920 |

|

SU216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления (его варианты) | 1984 |

|

SU1159020A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1984-07-27—Подача