j1304021-2

Изобретение относится к вычисли- ходные состояния блоков 1 и 6 далее тельной технике и может быть исполь- не проходят (см. фиг,2). зовано при riocTp.oeHHH управляющих си- По исходному -(нулевому) состоянию стем, а также самостоятельных микро- регистра 2 микрокоманд, как указыва- программных автоматов.операционные 5 лось на выходе 14 устройства, выходах части которых в два и более раз пре- 32, 33- регистра 2 микрокоманд и входе восходят адресные по разрядности. А мультиплексора 3 логических условий

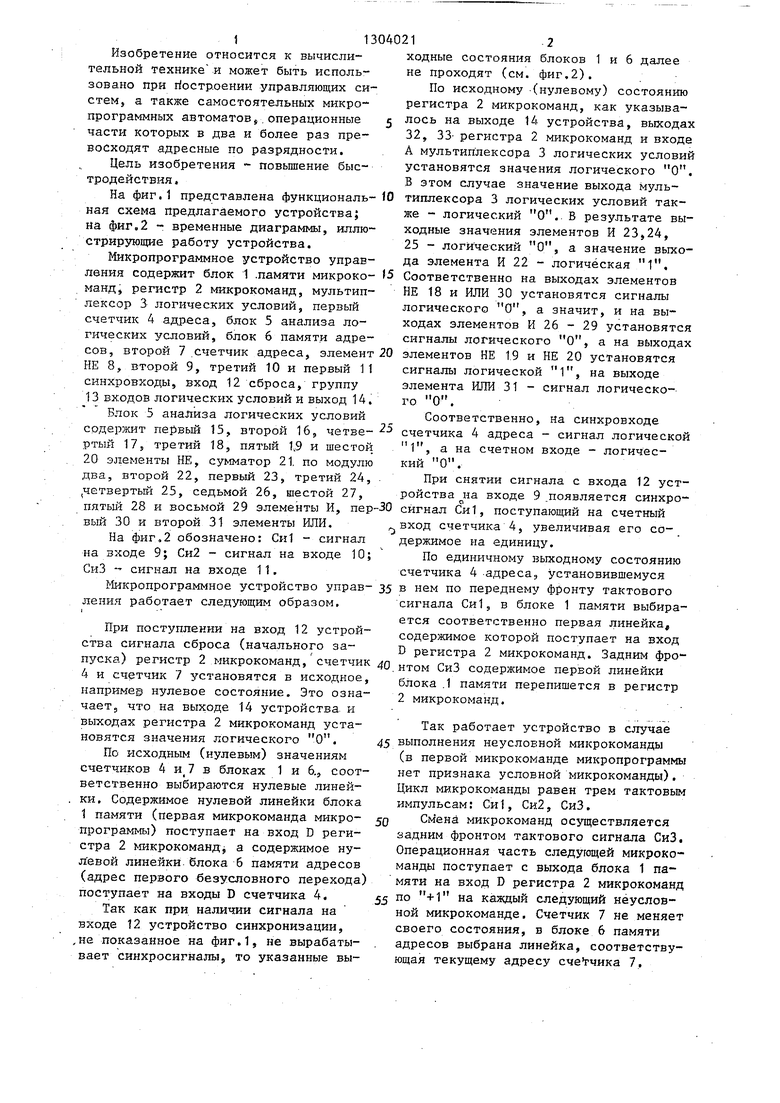

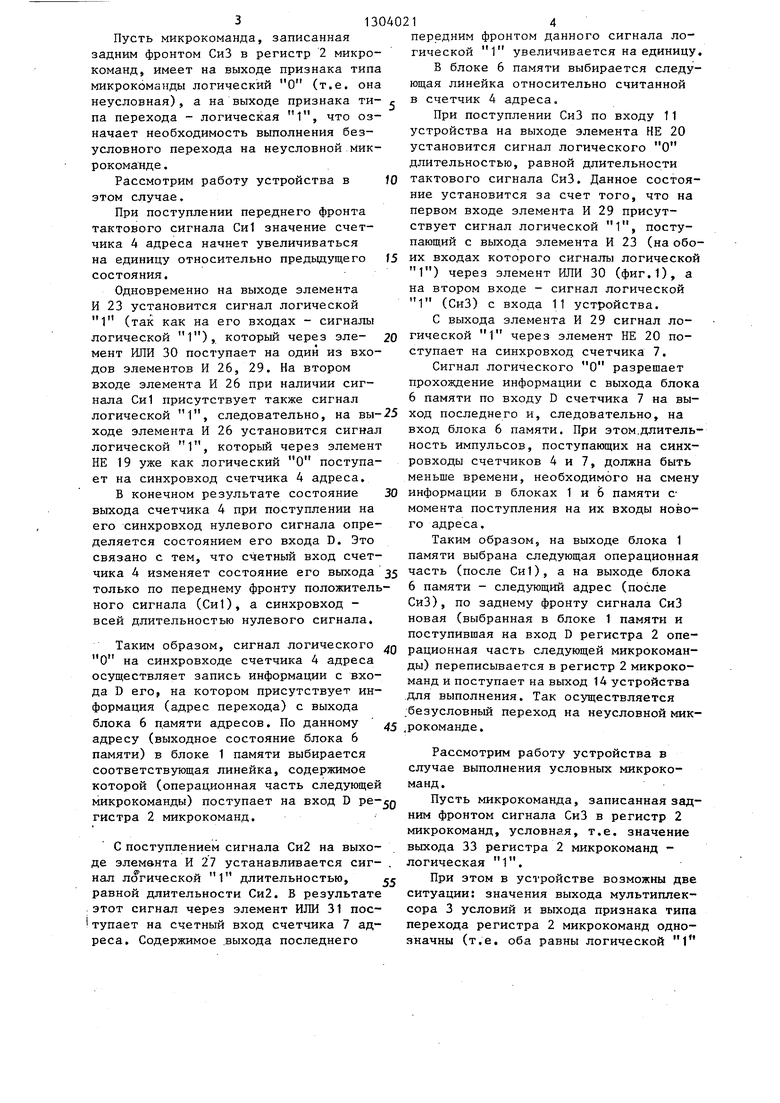

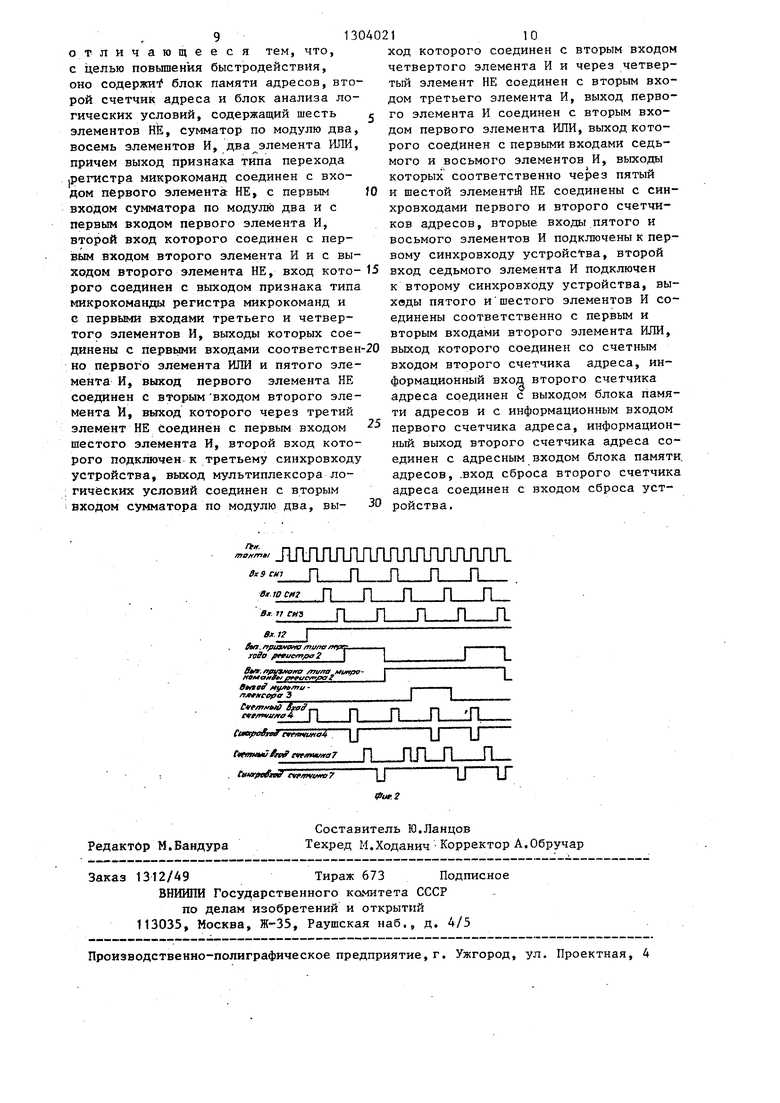

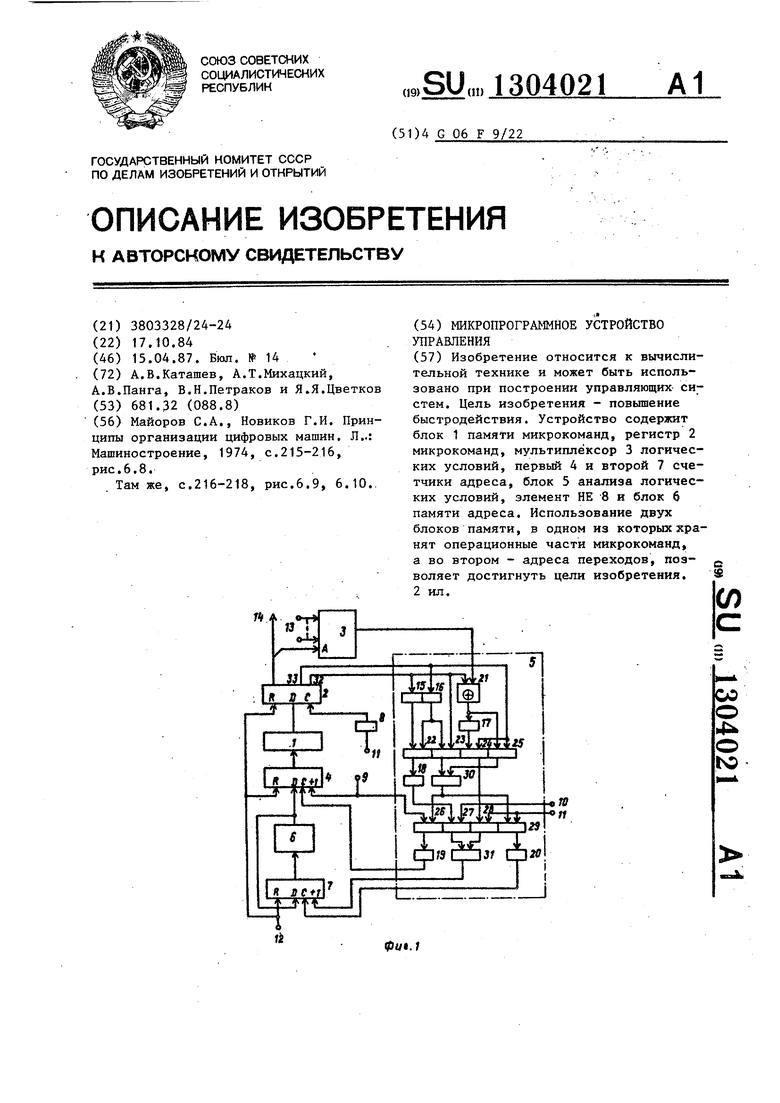

Цель изобретения повьшение быс- установятся значения логического О. тродействия,В этом случае значение выхода мульНа фиг.1 представлена функциональ-10 типлексора 3 логических условий так- ная схема предлагаемого устройства; же - логический О.. В результате вы- на фиг,2 - временные диаграммы, иллю ходные значения элементов И 23,24, стрирзтащие работу устройства.25 - логический О, а значение выхоМикропрограммное устройство управ- да элемента И 22 - логическая 1. Ленин содержит блок 1 .памяти микроко- (5 Соответственно на выходах элементов манд регистр 2 микрокоманд, мультип- НЕ 18 и ИЛИ 30 установятся сигналы лексор 3- логических условий, первый логического О, а значит, и на вы- счетчик 4 адреса, блок 5 анализа ло- ходах элементов И 26 - 29 установятся гическнх условий, блок 6 памяти адре- сигналы логического О, а на выходах сов, второй 7 .счетчик адреса, элемент 20 элементов НЕ 19 и НЕ 20 установятся НЕ 8, второй 9, третий 10 и первый 11 сигналы логической 1, на выходе синхровходы, вход 12 сброса, группу элемента ИЛИ 31 - сигнал логическо- 13 входов логических условий и выход 14. го О.

Блок 5 анализа логических условий Соответственно, на синхровходе содержит первый 15, второй 16,, четве- счетчика 4 адреса - сигнал логической ртый 17, третий 18, пятый 1,9 и шестой . 1, а на счетном входе - логичес- 20 элементы НЕ, сумматор 21, по модулю кий О.

два, второй 22, первый 23, третий 24, . При снятии сигнала с входа 12 уст- ,четвертьгй 25, седьмой 26, шестой 27, ройства на входе 9 .появляется синхро- пятый 28 и восьмой 29 элементы И, пер-30 сигнал Си1, поступающий на счетный вый 30 и второй 31 элементы ИЛИ. вход счетчика 4, увеличивая его соНа фиг..2 обозначено: Си1 - сигнал держимое на единицу.

на входе 9; Си2 - сигнал на входе 10; По единичному выходному состоянию СиЗ - сигнал на входе 11.счетчика 4 -адреса, установившемуся

Микропрограммное устройство управ- 35 в нем по переднему фронту тактового ления работает следующим образом, сигнала Си1, в блоке 1 памяти выбирается соответственно первая линейка.

При поступлении на вход 12 устрой- содержимое которой поступает на вход ства сигнала сброса (начального за- регистра 2 микрокоманд. Задним фро- пуска) регистр 2 микрокоманд, счетчик о нтом СиЗ содержимое первой линейки 4 и счетчик / установятся в исходное, блока .1 памяти перепишется в регистр напримеэ нулевое состояние. Это озна- 2 микрокоманд. чаеТэ что на выходе 14 устройства и выходах регистра 2 микрокоманд уста- Так работает устройство в случае новятся значения логического О. 5 выполнения неусловной микрокоманды

По исходным (нулевым) значениям (в первой микрокоманде микропрограммы счетчиков 4 в блоках 1 и 6., соот- нет признака условной микрокоманды). ветственно выбираются нулевые линей- Цикл микрокоманды равен трем тактовым ки. Содержимое нулевой линейки блока импульсам: Си1, Си2, СиЗ. 1 памяти (первая микрокоманда микро- jO См ена микрокоманд осуществляется программы) поступает на вход D реги- задним фронтом тактового сигнала СиЗ. стра 2 микрокоманд а содержимое ну- Операционная часть следующей микроко- л евой линейки- блока 6 памяти адресов манды поступает с выхода блока 1 па- (адрес первого безусловного перехода) мяти на вход D регистра 2 микрокоманд поступает на входы D счетчика 4. 55 ° +1 на каждый следующий нёусловТак как при наличии сигнала на ной микрокоманде, Счетчик 7 не меняет входе 12 устройство синхронизации, своего состояния, в блоке 6 памяти ,не показанное на фиг.1, не вырабаты- . адресов выбрана линейка, соответству- вает синхросигналы, то указанные вы- ющая текущему адресу сче гчика 7,

Пусть микрокоманда, записанная задним фронтом СиЗ в регистр 2 микрокоманд, имеет на выходе признака типа микрокоманды логический О (т.е. она

передним фронтом да

В блоке 6 памяти ющая линейка относи

неусловная), а на выходе признака ти- г в счетчик 4 адреса.

па перехода - логическая 1 , что означает необходимость выполнения безусловного перехода на неусловной микрокоманде .

Рассмотрим работу устройства в 10 этом случае.

При поступлении переднего фронта тактового сигнала Си1 значение счетчика 4 адреса начнет увеличиваться на единицу относительно предьщущего состояния.

Одновременно на выходе элемента И 23 установится сигнал логической 1 (так как на его входах - сигналы логической 1), который через элемент ИЛИ 30 поступает на один из входов элементов И 26, 29. На втором входе элемента И 26 при наличии сигПри поступлении устройства на выход установится сигнал

длительностью, равн тактового сигнала С ние установится за первом входе элемен ствует сигнал логич пающий с выхода эле f5 их входах которого 1) через элемент на втором входе - с 1 (СиЗ) с входа 1

С выхода элемент гической 1 через ступает на синхровх

Сигнал логическо прохождение информа 6 памяти по входу D

20

Сигнал логического О разрешает прохождение информации с выхода блока 6 памяти по входу D счетчика 7 на вынала Си1 присутствует также сигнал

логической 1, следовательно, на вы-25 ход последнего и, следовательно, на

ходе элемента И 26 установится сигнал вход блока 6 памяти. При этом.длительлогической 1, который через элемент НЕ 19 уже как логический О поступает на синхровход счетчика 4 адреса. В конечном результате состояние выхода счетчика 4 при поступлении на его синхровход нулевого сигнала определяется состоянием его входа D. Это связано с тем, что счетный вход счетчика 4 изменяет состояние его выхода 35 часть (после Си1), а на выходе блока только по переднему фронту положитель- 6 памяти - следующий адрес (после ного сигнала (Си1), а синхровход - всей длительностью нулевого сигнала.

СиЗ), по заднему фронту сигнала СиЗ новая (выбранная в блоке 1 памяти и поступившая на вход D регистра 2 опеТаким образом, сигнал логического Q рационная часть следующей микрокоманды) переписывается в регистр 2 микрокоманд и поступает на выход 14 устройства

О на синхровходе счетчика 4 адреса осуществляет запись информации с входа D его, на котором присутствует информация (адрес перехода) с выхода блока 6 памяти адресов. По данному адресу (выходное состояние блока 6 памяти) в блоке 1 памяти выбирается соответствующая линейка, содержимое которой (операционная часть следующей микрокоманды) поступает на вход D гистра 2 микрокоманд.

для выполнения. Так осуществляется .безусловный переход на неусловной мик- 45 .рокоманде.

Рассмотрим работу устройства в случае вьшолнения условных микрокоманд .

Пусть микрокоманда, записанная задним фронтом сигнала СиЗ в регистр 2 микрокоманд, условная, т.е. значение выхода 33 регистра 2 микрокоманд Пусть микрокоманда, записанная задним фронтом сигнала СиЗ в регистр 2 микрокоманд, условная, т.е. значение выхода 33 регистра 2 микрокоманд tl л II

I .

с поступлением сигнала Си2 на выходе элемента И 27 устанавливается сиг- . логическая нал логической 1 длительностью, При этом в устройстве возможны две равной длительности Си2. В результате ситуации: значения выхода мультиплек.этот сигнал через элемент ИЛИ 31 пос тупает на счетный вход счетчика 7 адреса. Содержимое .выхода последнего

сора 3 условий и выхода признака типа перехода регистра 2 микрокоманд однозначны (т.е. оба равны логической 1

4

фронтом данного сигнала лоВ блоке 6 памяти выбирается следующая линейка относительно считанной

При поступлении СиЗ по входу 11 устройства на выходе элемента НЕ 20 установится сигнал логического О

длительностью, равной длительности тактового сигнала СиЗ. Данное состояние установится за счет того, что на первом входе элемента И 29 присутствует сигнал логической 1, поступающий с выхода элемента И 23 (на обо- их входах которого сигналы логической 1) через элемент ИЛИ 30 (фиг.1), а на втором входе - сигнал логической 1 (СиЗ) с входа 11 устройства.

С выхода элемента И 29 сигнал логической 1 через элемент НЕ 20 поступает на синхровход счетчика 7.

Сигнал логического О разрешает прохождение информации с выхода блока 6 памяти по входу D счетчика 7 на вы

ность импульсов, поступающих на синх- ровходы счетчиков 4 и 7, должна быть меньше времени, необходимого на смену информации в блоках 1 и 6 памяти с- момента поступления на их входы нового адреса.

Таким образом, на выходе блока 1 памяти выбрана следующая операционная

о

для выполнения. Так осуществляется .безусловный переход на неусловной мик- 5 .рокоманде.

Рассмотрим работу устройства в случае вьшолнения условных микрокоманд .

Пусть микрокоманда, записанная задним фронтом сигнала СиЗ в регистр 2 микрокоманд, условная, т.е. значение выхода 33 регистра 2 микрокоманд tl л II

I .

. логическая При этом в устройстве возможны две ситуации: значения выхода мультиплексора 3 условий и выхода признака типа перехода регистра 2 микрокоманд однозначны (т.е. оба равны логической 1

йли оба - логическому О); значения выхода мультиплексора 3 условий и выхода признака типа перехода регистра 2 микрокоманд неоднозначны (1,0 или 0,1).

сигнал логической 1 с выхода признака типа микрокоманды регистра 2 микрокоманд. Сигнал логической 1 длительностью, равной длительности СиЗ, с выхода элемента И 28 через второй вход элемента ИЛИ 31 поступает на счетный вход счетчика 7 адреса:, увеличивая содержимое последнего еще на единицу (передним фронтом СиЗ). По

Рассмотрим работу устройства в первой ситуации.

Пусть значения выхода мультиплексора 3 условий и выхода признака типа перехода регистра 2 микрокоманд одно-fo данному выходному состоянию счетчика значны и равны логическому О. В 7 в блоке 6 памяти выбирается следую- этом случае значение выхода сумматора щая (за выбранной по Си2) линейка, со- 21 по модулю два равно логическому О. Значение выходов элементов И 22, 23, 25 равно логическому О, так как f5 хотя бы на одном из входов каждого из них присутствует сигнал логического О. На выходе элемента И 24 - лодержимое которой поступает на вход D счетчиков 4 и 7.

Задним фронтом сигнала СиЗ содержимое выхода блока t памяти переписывается в регистр 2 микрокоманд и поступает на выход.14 устройства для выполнения.

гическая 1 так как

входов - сигнал логической 1

на одном из его

с вы- 20

хода элемента НЕ 17, ,а на втором - сигнал логической 1 с выхода признака типа М11крокоманды регистра 2 микрокоманд .

По переднему фронту сигнала Си1 25 значение выхода счетчика 4 изменяется (увеличивается на единицу), в блоке 1 памяти выбирается следующая за выполняемой микрокоманда.

При поступлении сигнала Си2 по вхо-30 ды микропрограммы, а по +2 относиДУ 10 устройства на выходе элемента И 27 устанавливается сигнал логической 1 длительностью, равной длительности Си2, так как на одном из его входов сигнал логической 1 с входа 10(Си2) устройства, а на втором - сигнал логической 1 с выхода элемента НЕ 18 (сигнал логического О с выхода 32 регистра 2 микрокоманд через элементы НЕ 15, И 22 и НЕ 18). Сигнал логической 1 с выхода элемента И 27 через элемент ИПИ 31 поступает на соответствующий выход блок 5. Длительность этого сигнала равна длительности тактового сигнала Си2. Сигнал логической 1, поступая на счетный вход счетчика 7, увеличивает его содержимое на единицу. По полученному таким образом выходному состоянию счетчика 7 в блоке 6 памяти выбирается следующая линейка, содер- зкимое которой поступает на информационные входы D счетчиков 4 и 7.

При поступлении сигнала СиЗ по входу 11 устройства на выходе элемен та И 28 устанавливается сигнал логической 1, ,так как на одном из его входов - сигнал логической 1 с вхо 11 (СиЗ) устройства, а на втором

сигнал логической 1 с выхода признака типа микрокоманды регистра 2 микрокоманд. Сигнал логической 1 длительностью, равной длительности СиЗ, с выхода элемента И 28 через второй вход элемента ИЛИ 31 поступает на счетный вход счетчика 7 адреса:, увеличивая содержимое последнего еще на единицу (передним фронтом СиЗ). По

данному выходному состоянию счетчика 7 в блоке 6 памяти выбирается следую- щая (за выбранной по Си2) линейка, со-

данному выходному состоянию счетчика 7 в блоке 6 памяти выбирается следую- щая (за выбранной по Си2) линейка, со-

держимое которой поступает на вход D счетчиков 4 и 7.

Задним фронтом сигнала СиЗ содержимое выхода блока t памяти переписывается в регистр 2 микрокоманд и поступает на выход.14 устройства для выполнения.

. Так осуществляется выбор адреса следующей микрокоманды микропрограммы при выполнении условий микрокоманды и естественном порядке следования микрокоманд.

По +1 относительно адреса выполняемой микрокоманды - содержимого счетчика 4 адреса в блоке 1 памяти (с поступлением Си1) выбирается операционная часть следующей микрокоман5

тельно адреса - содержимого счетчика 7 адресов (переходов) в блоке 6 памяти (с поступлением Си2 и СиЗ) выбирается линейка с адресом следующего пе5 рехода.

. Работа устройства при единичном значении выхода мультиплексора 3 логических условий и выхода 32 регистра 2 микрокоманд аналогична описанной.

0 Рассмотрим работу устройства во второй ситуации.

Пусть значения выхода мультиплексора 3 условий и выхода признака типа перехода регистра 2 микрокоманд неод5 нозначны (1,0 или 0,1). Это означает, что на входы сумматора 21 по модулю два поступают неоднозначные сигналы и на выходе суммато ра 21 устанавливается сигнал логической 1.

С поступлением сигнала Си1 значение счетчика 4 начнет увеличиваться на единицу. Одновременно с выхода сумматора 21 сигнал логической 1 поступает на один из входов элемента и 25, на втором входе также присутствует сигнал логической 1 с выхода признака типа микрокоманды регистра .2 микрокоманд (так как выполняемая микрокоманда условная). В результате

0

713

на выходе элемента И 25 устанавливается сигнал логической 1.

Черег элемент ВДИ 30 сигнал логической 1 поступает на один из входов элементов Е 29 и 26, а так как на втором входе элемента И 26 присутствует сигнал логической 1 с входа 9 устройства (вход Си1), то на выходе элемента И 26 устанавливается сигнал

логической 1, поступающий через эле мент НЕ 19 уже как сигнал логическо- 0.

го

15

Так осуществляется выбор следующей микрокоманды и адрес следующего перехода при безусловном переходе на условной микрокоманде: по Си1 значение выхода блока 6 памяти переписывается в счетчик 4 адреса я представляет собой адрес следующей микрокоманды (адрес операционной части ее), по Си2 содержимое счетчика 7. увеличивается на единицу и по полученному таким образом выходному состоянию (адресу) в блоке 6 памяти выбирается соответствующая линейка, содержимое которой представляет собой адрес следующего перехода.

По переднему фронту тактового сигнала СиЗ данное выходное состояние блока 6 памяти переписьшается в счетчик 7 адреса и поступает на вход блоПоступая с выхода элемента НЕ 19 на синхровход счетчика 4 адреса сигнал логического О осуществляет запись информации (адрес .следующей микрокоманды) с выхода блока 6 памяти адресов переходов в счетчик 4 адреса.

По данному адресу (выходное состояние блока 6 памяти) в блоке .1 памяти 20 ка 6 памяти, а операционная часть выбирается соответствующая Jlинeйкa, следующей микрокоманды задним фронтом содержимое которой представляет собой операционную часть следующей за выполняемой микрокоманды.

При поступлении Си2 на один из входов элемента И 27 (сигнала логической 1) на выходе последило устанавливается сигнал логической 1,

25

тактового сигнала СиЗ (вход 11 устройства) переписывается в регистр 2 микрокоманд и поступает на выход 14 устройства для выполнения.

Машинный цикл в устройстве равен в этом случае трем тактовым импульсам: Си1, Си2, СиЗ.

так; как на втором из входов элемента И 27 также присутствует сигнал логической 1 независимо от конкретного значения (О или 1) выхода признака типа перекода регистра 2 микрокоманд. С выхода элемента И 27 сигнал лоМикропрограммное устройство управ ления, содержащее блок памяти микрокоманд, регистр микрокоманд, первый

гической 1 через элемент ИЛИ 31 по- 35 счетчик адреса, мультиплексор логиступает на счетный вход счетчика 7. Содержимое последнего увеличивается на единицу. В блоке 6 памяти по этому адресу выбирается линейка, содержимое которой поступает на входы D счетчиков 4 и 7

При поступлении сигнала СиЗ на один из входов элемента И 29 на выходе последнего устанавливается сигнал- логической 1, так как на втором входе этого элемента - сигнал логической 1 с выхода элемента ИЛИ 30.

Сигнал логической 1 с выхода элемента И 29 поступает через элемент НЕ 20 уже как сигнал логического О,

Поступая на синхровход счетчика 7, этот сигнал разрешает .запись информации с выхода блока 6 памяти по входу D счетчика 7 в последний. По ному таким образом адресу в блоке 6 памяти выбирается следующая линейка, содержимое которой представляет собой адрес следующего перехода.

40

ческих условий и элемент НЕ, причем выход блока памяти микрокоманд соеди нен с информационным входом регистра микрокоманд, вход сброса которого со единен с входом сброса первого счетчика адреса и подключен к входу сбро са устройства, синхровход регистра - микрокоманд через элемент НЕ подключен к первому синхровходу устройства

45 счетный вход первого счетчика адреса подключен к второму синхровходу устройства, адресный вход блока памяти микрокоманд соединен с информационны выходом первого счетчика адреса, вы ход поля проверки логических условий регистра микрокоманд соединен с упра вляющим входом мультиплексора логических условий, выход поля микроопераций регис;,тра микрокоманд подключен

к выходу устройства, группа входов логических условий устройства подклю чена к группе информационных входов мультиплексора логических условий.

8

О

5

Так осуществляется выбор следующей микрокоманды и адрес следующего перехода при безусловном переходе на условной микрокоманде: по Си1 значение выхода блока 6 памяти переписывается в счетчик 4 адреса я представляет собой адрес следующей микрокоманды (адрес операционной части ее), по Си2 содержимое счетчика 7. увеличивается на единицу и по полученному таким образом выходному состоянию (адресу) в блоке 6 памяти выбирается соответствующая линейка, содержимое которой представляет собой адрес следующего перехода.

По переднему фронту тактового сигнала СиЗ данное выходное состояние блока 6 памяти переписьшается в счетчик 7 адреса и поступает на вход бло0 ка 6 памяти, а операционная часть следующей микрокоманды задним фронтом

ка 6 памяти, а операционная часть следующей микрокоманды задним фронто

тактового сигнала СиЗ (вход 11 устройства) переписывается в регистр 2 микрокоманд и поступает на выход 14 устройства для выполнения.

Машинный цикл в устройстве равен в этом случае трем тактовым импульсам: Си1, Си2, СиЗ.

30

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, первый

35 счетчик адреса, мультиплексор логи

ческих условий и элемент НЕ, причем выход блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, вход сброса которого соединен с входом сброса первого счетчика адреса и подключен к входу сброса устройства, синхровход регистра микрокоманд через элемент НЕ подключен к первому синхровходу устройства,

счетный вход первого счетчика адреса подключен к второму синхровходу устройства, адресный вход блока памяти микрокоманд соединен с информационным выходом первого счетчика адреса, выход поля проверки логических условий регистра микрокоманд соединен с управляющим входом мультиплексора логических условий, выход поля микроопераций регис;,тра микрокоманд подключен

к выходу устройства, группа входов логических условий устройства подключена к группе информационных входов мультиплексора логических условий.

отличающееся тем, что, с целью пов1|Лпения быстродействия, оно содержи блок памяти адресов, второй счетчик адреса и блок анализа логических условий, содержащий шесть элементов НЕ, сумматор по модулю два, восемь элементов И, два элемента ИЛИ, причем выход признака типа перехода .регистра микрокоманд соединен с входом первого элемента НЕ, с первым входом сумматора по модулю два и с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и с выходом второго элемента НЕ, вход кото- рого соединен с выходом признака типа микрокоманд1я регистра микрокоманд и с первыми входами третьего и четвертого элементов И, выходы которых соединены с первьми входами соответствен но первого элемента ИЛИ и пятого элемента И, выкод первого элемента НЕ соединен с вторым входом второго элемента И, выход которого через третий элемент НЕ соединен с первым входом шестого элемента И, второй вход которого подключен к третьему синхровходу устройства, выход мультиплексора логических условий соединен с вторым входом сумматора по модулю два, вы

/.

JiTiTLJimijrumjuiruimmji

ход которого соединен с вторым входом четвертого элемента И и через четвертый элемент НЕ соединен с вторым входом третьего элемента И, выход первого элемента И соединен с вторым входом первого элемента ИЛИ, выход которого соединен с первьми входами седьмого и восьмого элементов И, выходы которых соответственно через пятый и шестой элемент НЕ соединены с син- хровходами первого и второго счетчиков адресов, вторые входы пятого и восьмого элементов И подключены к первому синхровходу устройства, второй вход седьмого элемента И подключен к второму синхровходу устройства, вы- хвды пятого и шестого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен со счетным входом второго счетчика адреса, информационный вход второго счетчика адреса соединен с выходом блока памяти адресов и с информационным входом первого счетчика адреса, информационный выход второго счетчика адреса соединен с адресным входом блока памяти, адресов, .вход сброса второго счетчика адреса соединен с входом сброса устройства.

8xS CMJ

в, to снг

Bt. J7 Cut

вх.12

fia. npiavoMa типа r.

ma, npuvoMo типа mtxf,

roSo fteuemfKii

Bvr.. HtMcii

Oltftfff MtfffffTru frjTffreezer 3

/тюла MuHoe-

ffffacf /x f

Cwmrrue ffpf. PvefTHfjifffa 4

Cuey oSttf епчятяа4 feenWHUAff nraminra

faaryegi tvfjnvt io7

Лпялri

и-IT

ir

Редактор M,Бандура

Составитель Ю.Ланцов Техред М.Ходанич Корректор А.Обручар

Заказ 1312/49Тираж 673 Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1304022A1 |

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1293729A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1429114A1 |

| Микропрограммное устройство управления (его варианты) | 1984 |

|

SU1159020A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1275441A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих- систем. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, мультиплексор 3 логических условий, первый 4 и второй 7 счетчики адреса, блок 5 анализа логических условий, элемент НЕ 8 и блок 6 памяти адреса. Использование двух блоков памяти, в одном из которых хранят операционные части микрокоманд, а во втором - адреса переходов, позволяет достигнуть цели изобретения. 2 ил. i СЛ со о 4 О Is5 гпгр т i фи.1

| Майоров С.А., Новиков Г.И | |||

| Принципы организации цифровых машин | |||

| Л..: Машиностроение, 1974, с.215-216, рис.6.8 | |||

| Там же, с.216-218, рис.6.9, 6.10. |

Авторы

Даты

1987-04-15—Публикация

1984-10-17—Подача