Изобретение относится к вычисли- тельной технике, в частности к умно- жителям.

Цель изобретения - расширение фунциональных возможностей за счет обес печения возможности обработки чисел со знаками.

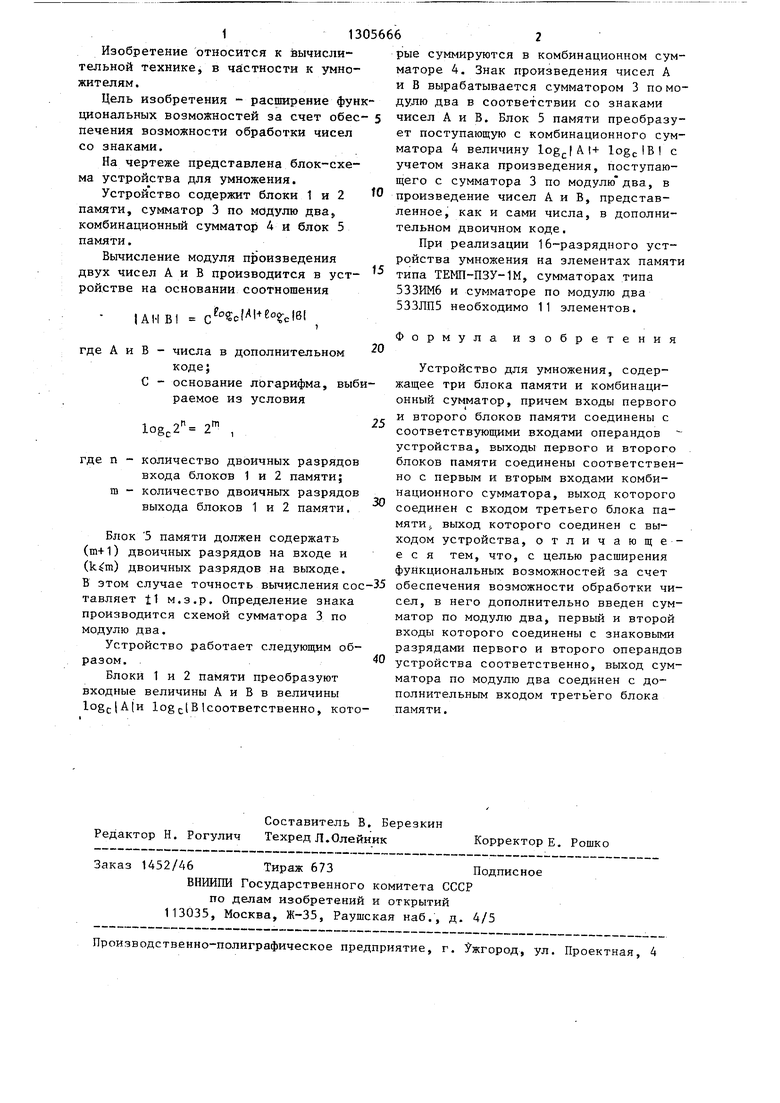

На чертеже представлена блок-схема устройства для умножения.

Устрой ство содержит блоки 1 и 2 памяти, сумматор 3 по модулю два,, комбинационный сумматор 4 и блок 5 памяти.

Вычисление модуля произведения двух чисел А и В производится в устройстве на основании соотношения

IAHBI

где А и В - числа в дополнительном

коде;

С - основание льгарифма, выбираемое из условия

log,2 2

где п - количество двоичных разрядов

входа блоков 1 и 2 памяти; m - количество двоичных разрядов выхода блоков 1 и 2 памяти.

Блок 5 памяти должен содержать (т+1) двоичных разрядов на входе и () двоичных разрядов на выходе.

В этом случае точность вычисления сос-35 обеспечения возможности обработки читавляет t1 м.з.р. Определение знака производится схемой сумматора 3 по модулю два.

Устройство работает следующим образом.

Блоки 1 и 2 памяти преобразуют входные величины А и В в величины logj-(A|H log ct В 1соответственно, котоСоставитель В. Березкин Редактор Н. Рогулич Техред Л.Олейник

Кор Под

1452/46 Тираж 673

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

рые суммируются в комбинационном сумматоре 4. Знак произведения чисел А и В вырабатывается сумматором 3 по модулю два в соответствии со знаками чисел А и В. Блок 5 памяти преобразует поступающую с комбинационного сумматора 4 величину с учетом знака произведения, поступающего с сумматора 3 по модулю два, в произведение чисел А и В, представленное, как и сами числа, в дополнительном двоичном коде.

При реализации 16-разрядного устройства умножения на элементах памяти типа ТЕМП-ПЗУ-Ш, сумматорах типа 533ИМ6 и сумматоре по модулю два 533ЛП5 необходимо 11 элементов.

Формула изобретения

Устройство для умножения, содержащее три блока памяти и комбинационный сумматор, причем входы первого и второго блоков памяти соединены с соответствующими входами операндов устройства, выходы первого и второго блоков памяти соединены соответственно с первым и вторым входами комбинационного сумматора, выход которого соединен с входом третьего блока памяти , выход которого соединен с выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет

сел, в него дополнительно введен сумматор по модулю два, первый и второй входы которого соединены с знаковыми разрядами первого и второго операндов устройства соответственно, выход сумматора по модулю два соединен с дополнительным входом третьего блока памяти.

Корректор Е. Рошко Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1432507A2 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Вычислительное устройство | 1990 |

|

SU1742814A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

Изобретение относится к вычислительной технике, в частности к умножителям. Устройство позволяет вычислить произведение двух чисел, пред- ставленньпс в дополнителвном двоичном коде. Целью изобретения является расширение функциональных возможностей за счет обработки чисел со знаками. Устройство состоит из трех блоков 1, 2, 5 памяти, сумматора 3 по модулю два и комбинационного сумматора 4. Первые два блока 1, 2 памяти вычисляют логарифм первого и второго сомножителей. Логарифмы.сомножителей суммируются в комбинационном сумматоре 4. Третий блок 5 памяти преобразует сумму логарифмов сомножителей в их произведение. Знак произведения определяется в сумматоре 3 по модулю два и поступает на третий блок 5. 1 ил. & (Л с со о СП 05 О5 О5

| Бузунов Ю.А., Вавилов Е.Н | |||

| Принципы построения цифровых вычислительных машин | |||

| - Киев: Техника, 1972, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| Потапов В.И | |||

| и др | |||

| Быстродействующие АЛУ ЦВМ | |||

| - Новосибирск: НИСИ, 1978, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-04-23—Публикация

1985-05-29—Подача