Од

СП

Изобретение относится к вычисли- т ельной технике, в частности к умно- з телям, и является усовершенствованием изобретения по авт.св.№ 1305666. Цель изобретения - расширение области применения за счет обработки Сомножителей, равных нулю.

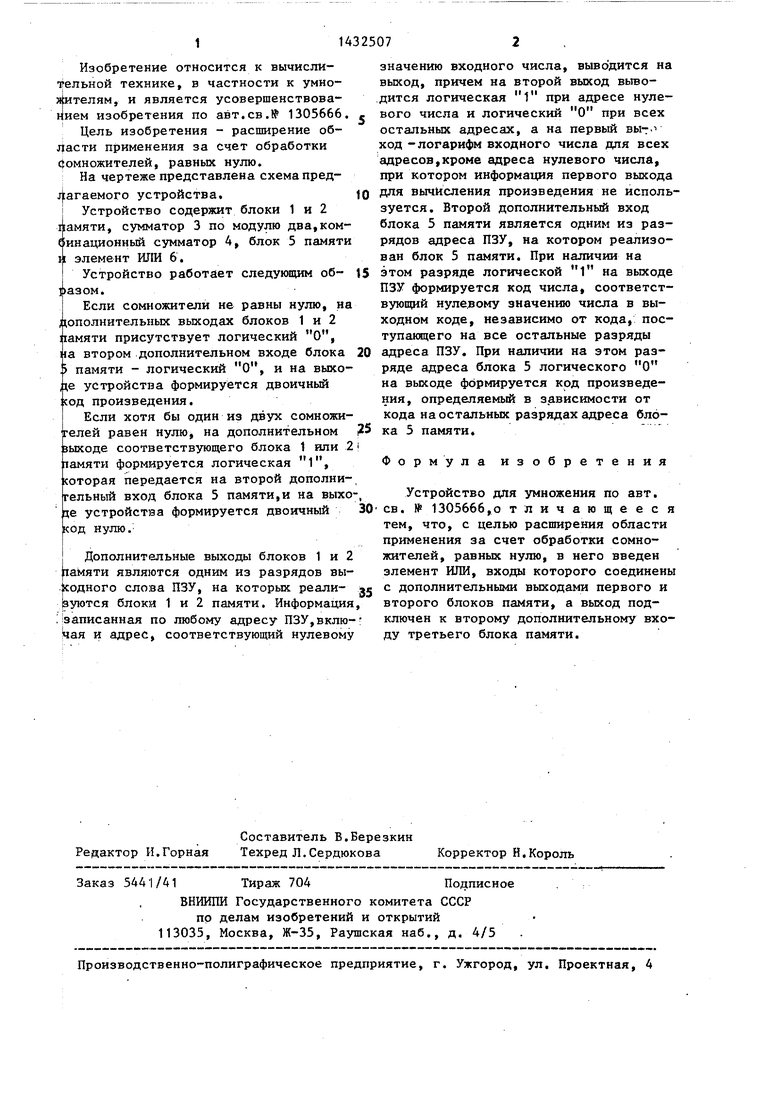

На чертеже представлена схема пред агаемого устройства,

I Устройство содержит блоки 1 и 2 амяти, сумматор 3 по модулю два,ком- инационный сумматор 4, блок 5 памяти

элемент ИЛИ 6. j Устройство работает следукидим об фазом.

I Если сомножители не равны нулю, на дополнительных выходах блоков 1 и 2 памяти присутствует логический О, на втором дополнительном входе блока .) памяти - логический О, и на выходе устройства формируется двоичный код произведения.

Если хотя бы один из двух сомножителей равен нулю, на дополнительном зыходе соответствующего блока 1 или 2 памяти формируется логическая 1, шторая передается на второй дополнительный вход блока 5 памяти,и на выхо а;е устройства формируется двоичный код нулю.

j Дополнительные выходы блоков 1 и 2 амяти являются одним из разрядов вы- содного слова ПЗУ, на которых реали- jj Дуются блоки 1 и 2 памяти. Информация, Написанная по любому адресу ПЗУ,вклю-: чая и адрес, соответствующий нулевому

значению входного числа, выводится на выход, причем на второй выход вьгоо- дится логическая 1 при адресе нулевого числа и логический О при всех остальных адресах, а на первый вы-Г ход -логарифм входного числа для всех адресов,кроме адреса нулевого числа, при котором информация первого выхода для вычисления произведения не используется. Второй дополнительный вход блока 5 памяти является одним из разрядов адреса ПЗУ, на котором реализован блок 5 памяти. При наличии на этом разряде логической 1 на выходе ПЗУ формируется код числа, соответствующий нуле,вому значению числа в выходном коде, независимо от кода, поступающего на все остальные разряды адреса ПЗУ. При наличии на этом разряде адреса блока 5 логического О на выходе формируется код произведения, определяемый в зависимости от кода на остальных разрядах адреса блока 5 памяти.

Формула изобретения

Устройство для умножения по авт. св. № 1305666,0 тличающееся тем, что, с целью расширения области применения за счет обработки сомножителей, равных нулю, в него введен элемент ИЛИ, входы которого соединены с дополнительными выходами первого и второго блоков памяти, а выход подключен к второму дополнительному входу третьего блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1305666A1 |

| Интерполятор | 1986 |

|

SU1405074A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА | 2021 |

|

RU2766990C1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Изобретение относится к вычисли- т льной технике, в частности к умножителям, и является усовершенствованием изобретения по авт.св.№ 1305666. Целью изобретения является расширение области применения за .счет о бработки сомножителей, равных нулю. Устройство содержит блоки 1, 2 памяти, сумматор 3 по модулю два, комбинационный сумматор 4,блок 5 памяти и вновь введенный элемент ИЛИ 6. 1 ил.

| Устройство для умножения | 1985 |

|

SU1305666A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-01-20—Подача