13056682

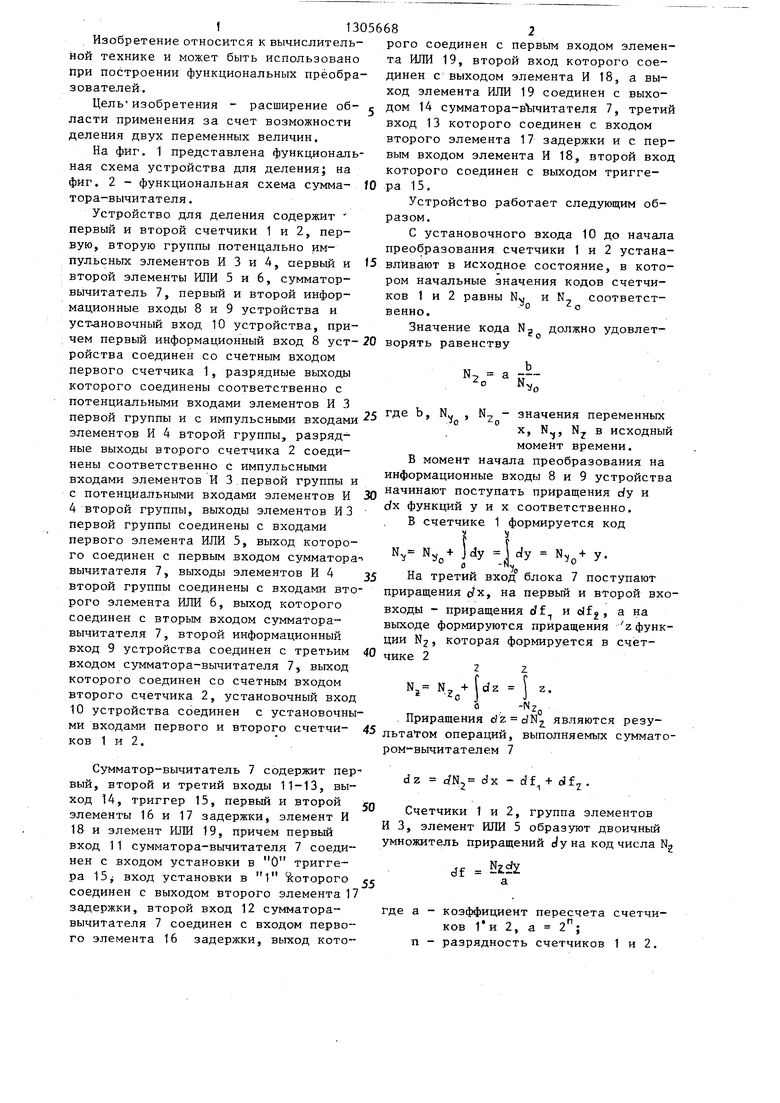

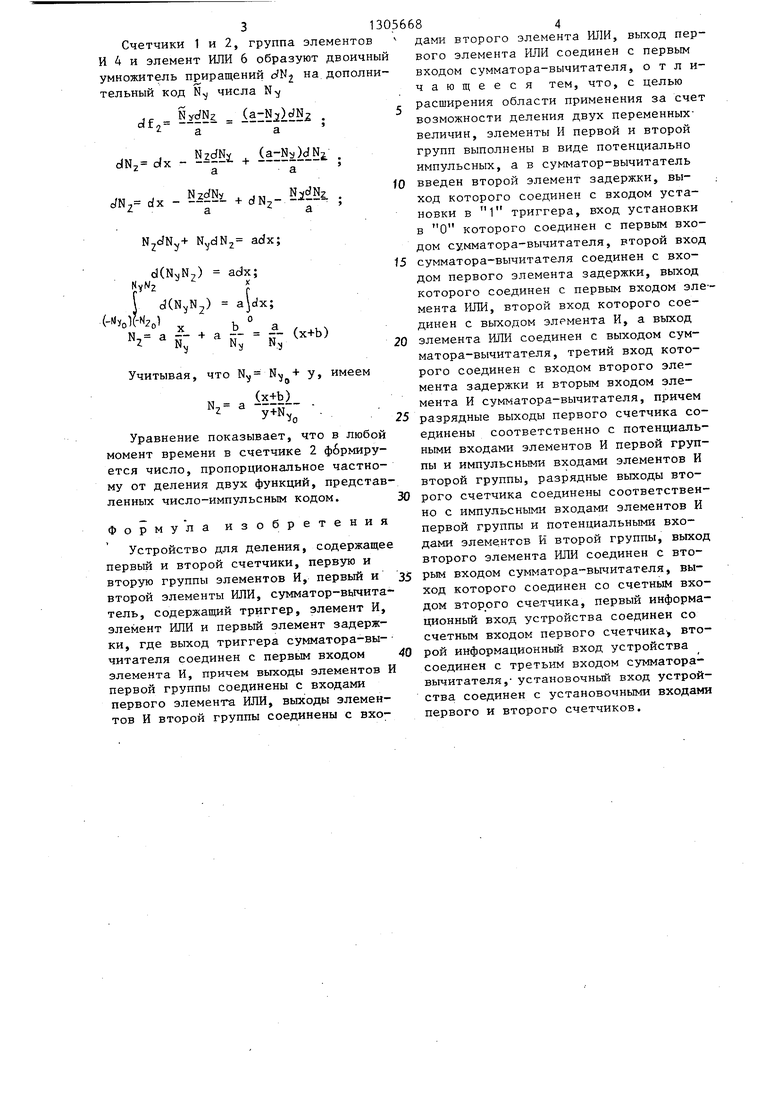

Изобретение относится к вычислитель- рого соединен с первым входом элемен- ной технике и может быть использовано та ИЛИ 19, второй вход которого сое- при построении функциональных прёобра- дивен с выходом элемента И 18, а вы- зователей.ход элемента ИЛИ 19 соединен с выхоЦель изобретения - расширение об- с дом 14 сумматора-вЪгчитателя 7, третий ласти применения за счет возможности вход 13 которого соединен с входом деления двух переменных величин, второго элемента 17 задержки и с перНа фиг. 1 представлена функциональ- вым входом элемента И 18, второй вход ная схема устройства для деления; на которого соединен с выходом тригге- фиг. 2 - функциональная схема сумма- fO pa 15, тора-вычитателя.Устройство работает следующим обУстройство для деления содержит разом.

первый и второй счетчики 1 и 2, пер- С установочного входа 10 до начала вую, вторую группы потенцально им- преобразования счетчики 1 и 2 устана- пульсных элементов И 3 и 4, первый и 15 вливают в исходное состояние, в кото- второй элементы ИЛИ 5 и 6, сумматор- ром начальные значения кодов счетчи- вычитатель 7, первый и второй инфор- ков 1 и 2 равны No и N.. соответст- мационные входы 8 и 9 устройства и венно.

уст-ановочный вход 10 устройства, при- Значение кода Nj должно удовлет- чем первый информационный вход В уст- 20 ворять равенству ройства соединен со счетным входом,

первого счетчика 1, разрядные выходыN- а --

которого соединены соответственно сVo

потенциальными входами элементов ИЗ и ч .т

ус где Ь, N.. , N-, - значения переменных первой группы и с импульсными входами - о о ., ,

„ , „X, Ы„, N в исходный

элементов И ч второй группы, разряд- т z

омомент времени,

ные выходы второго счетчика 2 соеди- ,,

В момент начала преобразования на нены соответственно с импульсными ,о п „ « „информационные входы 8 и 9 устройства

входами элементов И 3 первой группы и , «,

с потенциальньши входами элементов И 30 начинают поступать приращения dy и 4 второй группы, вьпсоды элементов И 3 Функций у и х соответственно, первой группы соединены с входами счетчике 1 формируется код первого элемента ИЛИ 5, выход которо- f j го соединен с первым входом сумматора- о - о вычитателя 7, выходы элементов И 4 35 На третий вход блока 7 поступают второй группы соединены с входами вто- приращения , на первый и второй вхо- рого элемента ИЛИ 6, выход которого - приращения df и df, а на соединен с вторым входом сумматора- выходе формируются приращения z функ- вычитателя 7, второй информационный ции N2, которая формируется в счет- вход 9 устройства соединен с третьим 40 чике 2 входом сумматора-вычитателя 7, выход2 z

которого соединен со счетным входом j jj + Ij,, - второго счетчика 2, установочный вход J L

10 устройства соединен с установочны- Приращения с z являются резу- ми входами первого и второго счетчи- 45 операций, выполняемых суммато- ков 1 и Z,ром-вычитателем 7

Сумматор-вычитатель 7 содержит пер , .„ , ,. .. „ :, „ 11 -зclz , dx-df+dlf7.

выи, второй и третий входы 11-13, вы-2 i /

ход 14, триггер 15, первый и второйсп ,, -,

., ,-, II Счетчики 1 и 2,группа элементов

элементы 16 и 17 задержки, элемент И , „ ,„„, I

,0 ,,гтт1 in ИЗ, элемент ИЛИ 5образуют двоичньш

18 и элемент ИЛИ 19, причем первыйг f

,,-, умножитель приращений ау на код числа N-j

вход 11 сумматора-вьгаитателя 7 соеди- --ч« м 2

иен с входом установки в О тригге- N2.

ра 15j вход установки в 1 Которого а

соединен с выходом второго элемента 17

задержки, второй вход 12 сумматора- где а - коэффициент пересчета счетчивычитателя 7 соединен с входом перво-ков 2, а 2 ;

го элемента 16 задержки, выход кото- п - разрядность счетчиков 1 и 2,

31305668

Счетчики 1 и 2, группа элементов 4 и элемент ИЛИ 6 образуют двоичный множитель приращений c Nj на дополниельный код NX; числа N,

, NydNz ( Ч а а

dN, dx - N

д в вх

ра во ве гр им вв хо но в до су до ко ме ди эл ма ро ме ме ра ед ны пы вт ро но пе да вт ры хо до ци сч ро со вы ст пе

dx

a

+ dNjN dNza

N2dN,+ N,,dN.j adx;

) adx; NyNz X ff

У )

)(-N2o) „ г, ° „

NZ

ir

b

sr

г7- (x+b)

что Щ

N, + у, имеем

N,

Vo (x+b)

y+N

0

Уравнение показывает, что в любой момент времени в счетчике 2 фбрмиру- ется число, пропорциональное частному от деления двух функций, представленных число-импульсным кодом.

Формула изобретения

Устройство для деления, содержащее первый и второй счетчики, первую и вторую группы элементов И, первый и второй элементы ИЛИ, сумматор-вычита- тель, содержащий триггер, элемент И, элемент ИЛИ и первый элемент задержки, где выход триггера сумматора-вы- читателя соединен с первым входом элемента И, причем выходы элементов И первой группы соединены с входами первого элемента ИЛИ, выходы элементов И второй группы соединены с входами второго элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом сумматора-вычитателя, о т л и10

5

0

5

0

5 0

расширения области применения за счет возможности деления двух переменных- величин, элементы И первой и второй групп выполнены в виде потенциально импульсных, а в сумматор-вычитатель введен второй элемент задержки, вы- ; ход которого соединен с входом установки в 1 триггера, вход установки в О которого соединен с первым входом сумматора-вычитателя, второй вход сумматора-вычитателя соединен с входом первого элемента задержки, выход которого соединен с первьм входом элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход элемента ИЛИ соединен с выходом сумматора-вычитателя, третий вход которого соединен с входом второго элемента задержки и вторым входом элемента И сумматора-вычитателя, причем разрядные выходы первого счетчика соединены соответственно с потенциальными входами элементов И первой группы и импульсными входами элементов И второй группы, разрядные выходы второго счетчика соединены соответственно с импульсными входами элементов И первой группы и Потенциальными входами элементов И второй группы, выход второго элемента ИЛИ соединен с вторым входом сумматора-вычитателя, выход которого соединен со счетным входом второго счетчика, первый информационный вход устройства соединен со счетным входом первого счетчика второй информационньш вход устройства соединен с третьим входом сумматора- вычитателя,- установочный вход устройства соединен с установочными входами первого и второго счетчиков.

1

JS

18

15

16

.

12

Составитель В. Гусев Редактор Н. Рогулич Техред Л.Олейник

Заказ 1452/46 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

11

Корректор С. Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Устройство для вычисления логарифмической функции | 1985 |

|

SU1280617A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1120322A1 |

| Функциональный преобразователь | 1984 |

|

SU1226449A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении функциональных преобразователей. Цель изобретения расширение области применения за счет возможности деления двух переменных величин. Устройство содержит два датчика 1, 2, две группы потенциально- импульсных элементов ИЗ, 4, два элемента ИЛИ 5, 6, сумматор-вычитатель 7, два информационных входа 8, 9 и установочный вход 10 с соответствующими связями. Сумматор-вычитатель 7 содержит три входа, выход, триггер, два элемента задержки,- элемент И, элемент ИЛИ с соответствующими связями. Образование частного при поступлении единичных приращений на информационные входы устройства выполняются с помощью операции умножения сумматором-вычита- с телем по формуле х - df + dfy. ® (Л 2 ил. Фиг.1

| Майоров Ф.В | |||

| Электронные цифровые интегрирующие машины | |||

| - М.: Маш- гиз, 1962, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Вычислительное устройство | 1978 |

|

SU840902A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1986-01-02—Подача