1 13

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Цель изобретения - повышение быст родействия за счет вычисления таблично-алгоритмическим методом.

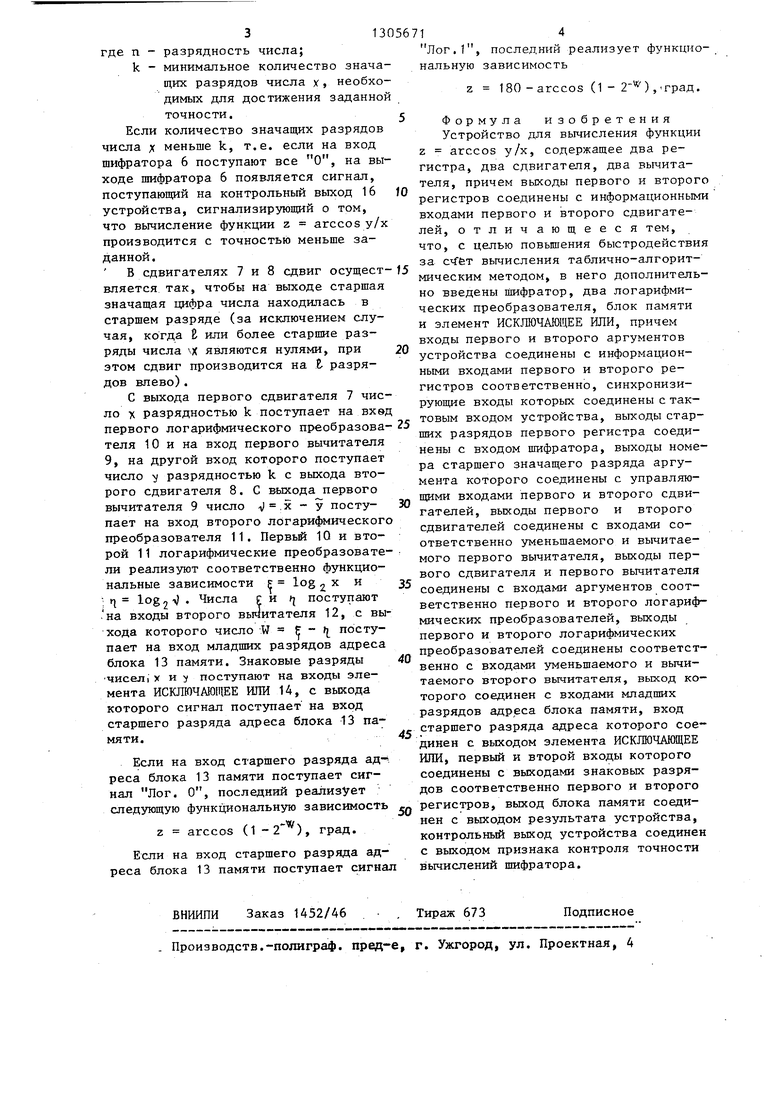

На чертеже представлена функциональная схема устройства.

Устройство содержит вход 1 первог аргумента, вход 2 второго аргумента, первый регистр 3, второй регистр 4, тактовьй вход 5, шифратор 6, первый сдвигатель 7, второй сдвигатель 8, первый вьиитатель 9, первый логарифмический преобразователь 10, второй логарифмический преобразователь 11, второй вычитатель 12, блок 13 памяти элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, выход 15 результата и контрольный выход 16.

Увеличение быстродействия вычисления функций может быть получено при переходе от итерационных методов вычисления к таблично-алгоритмическим при узкой специализации вычислительного процесса.

Вычисление функции z arccos у/х :производят В следующем порядке.

Одним из известных алгоритмов вы

числяют значение V -, затем, подав

Л.

значение V на адресный вход блока памяти, на выходе получают значение функции Z arccos V.

При малых значениях выходных уг- лов, что соответствует значениям V близким к единице, из-за высокой чувствительности функции z arccos в этой области устройство обладает значительной инструментальной погреш ностью, для снижения котсфой необходимо увеличивать входную разрядную сетку блока памйти.

Бходные числа и у, поступающие по входам 1 и 2, заносятся соответственно в первый 3 и второй 4 регистры

Искусственным алгоритмическим спо-г

-, -,- 44 по сигналам тактового входа 5 устройсобом можно обеспечить требуемую точ- з«

ность вычисления без увеличения затства. Число с выхода первого регистра

3поступает на вход первого 7 сдвигате- ля, а число V с выхода второго регистра

рат аппаратуры.

Представляют значение

V у/х в виде

V у/х 1 ...+ Ь2

0,1,2,...;

,-п--1

где n

О i i 2 Выражение (2) переписьшают

2 - 1

„.„ +е

(3)

5

огда

5

0

25

После преобразований получают n-log(1-e-2 )log2X-log,,(x-y). (4) Так как t, ,то

loRjd )(J -1; 0. Обозначают

m - 2 ),

n +m logjX - log5,(x - y), (5)

где n 0,1,2,...;

Ojfm .1.

Таким образом, у числа n +m n - его целая часть, a m - дробная.

Если m однозначно зависит от , правая часть выражения (5) насет полную информацию о числе V.

Подавая на адресный вход блока ПЗУ не число V, а результат вычисления выражения (5), можно сократить входную разрядную сетку блока памяти, так как при этом не требуется подавать значительное количество

11 и

1, а информацию

30

о количестве 1 снимать с целой части результата вычисления выражения (5). Работа устройства описывается следующими математическими соотношениями: i

I xl - I у(;

ом,

«I Iog2 ;

W - h;. (6)

z arccos (1 -2), если xy:j.O; z 180-arcos( ), еслиxy 0. Устройство работает следующим обазом,

Бходные числа и у, поступающие по входам 1 и 2, заносятся соответственно в первый 3 и второй 4 регистры

г

«

ства. Число с выхода первого регистра

3поступает на вход первого 7 сдвигате- ля, а число V с выхода второго регистра

4- на вход второго сдвигателя 8. Старшие разряды числа х поступают на вход шифратора 6, на выходе которого образуется двоичный параллельный код номера старшего значащего разряда числа , управляющий работой сдвигателей 7 и 8.

Количество 1 старших разрядов чиса X, поступающих на вход приоритетного шифратора, выбирается из соотноения,

1 п - k + 1, (7)

31305671

n - разрядность числа;

k - минимальное количество значащих разрядов числа у, необходимых для достижения заданной

точности.

Если количество значащих разрядов числа X меньше k, т.е. если на вход шифратора 6 поступают все О, на выходе шифратора 6 появляется сигнал, поступающий на контрольный выход 16 устройства, сигнализирующий о том, что вычисление функции г arccos у/х производится с точностью меньше заданной.

В сдвигателях 7 и 8 сдвиг осущест вляется так, чтобы на выходе старшая значащая цифра числа находилась в старшем разряде (за исключением случая, когда Е или более старшие разряды числа х являются нулями, при этом сдвиг производится на t разрядов влево).

С выхода первого сдвигателя 7 число X разрядностью k поступает на вхвд первого логарифмического преобразова- теля 10 и на вход первого вычитателя 9, на другой вход которого поступает число у разрядностью k с выхода второго сдвигателя 8. С выхода первого вычитателя 9 число .х - у поступает на вход второго логарифмического преобразователя 11. Первьй 10 и второй 11 логарифмические преобразователи реализ5тат соответственно функциональные зависимости log х и ; q log 2 л) . Числа и fj поступают . на входы второго вычитателя 12, с выхода которого число W f} поступает на вход младших разрядов адреса блока 13 памяти. Знаковые разряды чисел у и поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ШШ 14, с выхода которого сигнал поступает на вход старшего разряда адреса блока 13 памяти.

Если на вход старшего разряда ад-. реса блока 13 памяти поступает сигнал Лог. О, последний реализует следующую функциональную зависимость

Z arccos (1 -2 ), град.

Если на вход старшего разряда адреса блока 13 памяти поступает сигнал

ВНИИПИ Заказ 1452/46 . . Тираж 673 Подписное . Производств.-полиграф, пред-е, г. Ужгород, ул. Проектная, 4

Лог.1, последний реализует функциональную зависимость

Z 180-arccos (1 - ), Град.

10

15 0

5

30

5

0

5

0

Формула изобретения Устройство для вычисления функции Z arccos у/х, содержащее два регистра, два сдвигателя, два вычитателя, причем выходы первого и второго регистров соединены с информационными входами первого и второго сдвигате- лей, отлич ающееся тем, что, с целью повышения быстродействия за вычисления таблично-алгоритмическим методом, в него дополнительно введены шифратор, два логарифмических преобразователя, блок памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем входы первого и второго аргументов устройства соединены с информационными входами первого и второго регистров соответственно, синхронизирующие входы которых соединены с тактовым входом устройства, выходы старших разрядов первого регистра соединены с входом шифратора, выходы номера старшего значащего разряда аргумента которого соединены с управляющими входами первого и второго сдви- гателей, выходы первого и второго сдвигателей соединены с входами соответственно уменьшаемого и вычитаемого первого вычитателя, выходы первого сдвигателя и первого вычитателя соединены с входами аргументов соответственно первого и второго логарифмических преобразователей, выходы первого и второго логарифмических преобразователей соединены соответственно с входами уменьшаемого и вычитаемого второго вычитателя, выход которого соединен с входами младших разрядов адреса блока памяти, вход старшего разряда адреса которого соединен с выходом элемента ИСКЛЮЧАЩЕЕ ИЛИ, первый и второй входы которого соединены с выходами знаковых разрядов соответственно первого и второго регистров, выход блока памяти соединен с выходом результата устройства, контрольный выход устройства соединен с выходом признака контроля точности вычислений шифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Цифровой логарифмический преобразователь | 1987 |

|

SU1425665A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Преобразователь логарифмического кода в двоичный код | 1990 |

|

SU1716506A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

Изобретение относится к вь мислительной технике и может быть использовано в специализированных вычислителях автономно или в качестве функционального расширителя в составе больших ЭВМ. Целью изобретения является повьшение быстродействия за счет вычисления таблично-алгоритмическим методом. Устройство содержит вход 1 первого аргумента, вход 2 второго аргумента, первый регистр 3, второй регистр 4, тактовый вход 5, шифратор 6, первый сдвигатель 7, второй сдвига- тель 8, первьй вычитатель 9, первый логарифмический преобразователь 10, второй логарифмический преобразователь 11, второй вьиитатель 12, блок памяти 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, выход 15 результата, контрольный выход 16, 1 ил. i (Л оо о 01 05

| Анализатор кодов | 1977 |

|

SU703828A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Байков В.Д., Смолов В.Б | |||

| Аппаратурная реализация .элементарных функций в УВМ.- Л.: ЛГУ, 1975, с.71, рис.Зй. | |||

Авторы

Даты

1987-04-23—Публикация

1985-12-10—Подача