Изобретение относится к импульсной технике и може.т быть использовано в устройствах автоматики и вычислительной техники и в синтезаторах частот.

Цель изобретения - повышение быст- родействия.

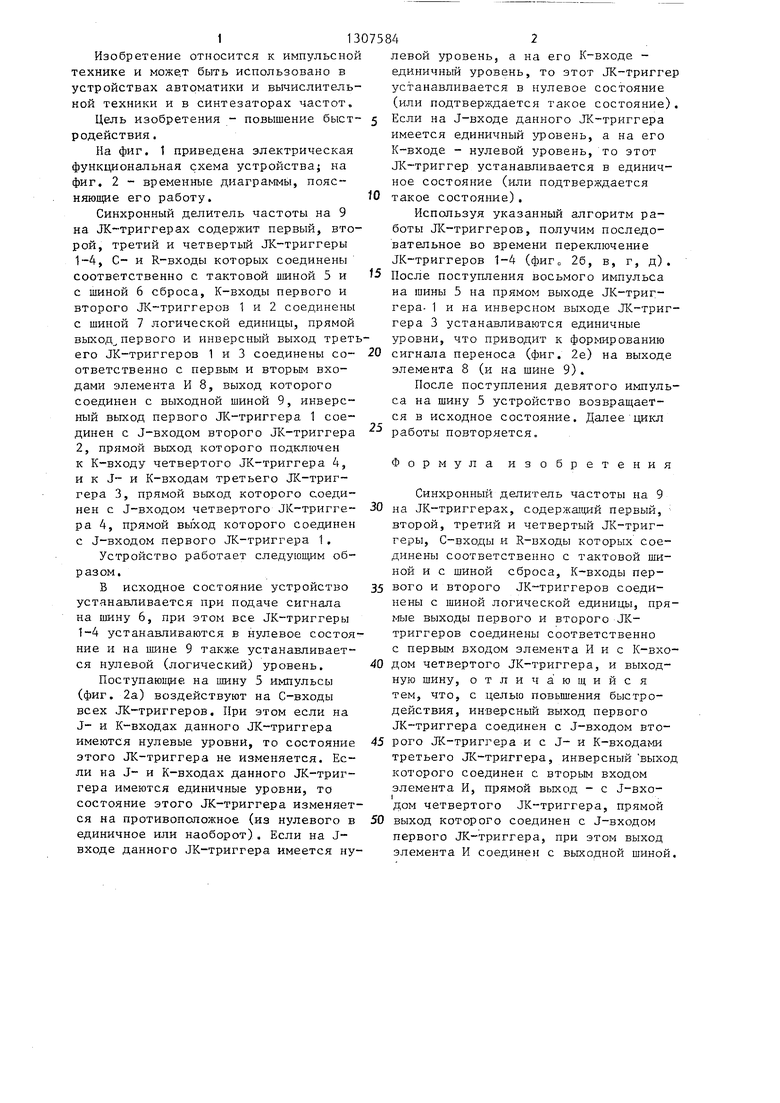

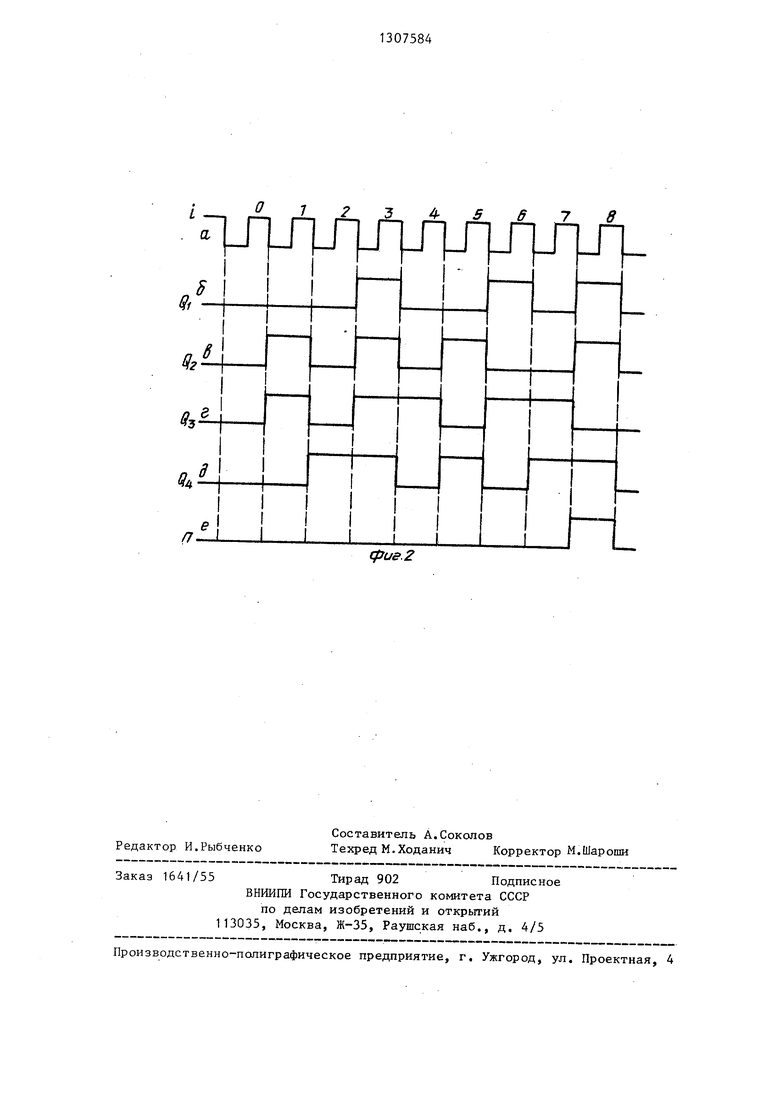

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Синхронный делитель частоты на 9 на JK-триггерах содержит первый, второй, третий и четвертьш JK-триггеры 1-4, С- и R-входы которых соединены соответственно с тактовой шиной 5 и с шиной 6 сброса, К-входы первого и второго ЛС-триггеров 1 и 2 соединены с шиной 7 логической единиды, прямой выход первого и инверсный выход третего JK-триггеров 1 и 3 соединены соответственно с первым и вторым входами элемента И 8, выход которого соединен с выходной шиной 9, инверсный выход первого ЛС-триггера 1 соединен с J-входом второго JK-триггера 2, прямой выход которого подключен к К-входу четвертого JK-триггера 4, и к J и К-входам третьего JK-триггера 3, прямой выход которого соединен с J-входом четвертого JK-триггера 4, прямой выход которого соединен с J-входом первого JK-триггера 1.

Устройство работает следующим образом,

Б исходное состояние устройство устанавливается при подаче сигнала на шину 6, при этом все JK-триггеры 1-4 устанавливаются в нулевое состояние и на шине 9 также устанавливается нулевой (логический) уровень.

Поступающие на шину 5 импульсы (фиг. 2а) воздействуют на С-входы всех ЛС-триггеров. При этом если на J- и К-входах данного JK-триггера имеются нулевые уровни, то состояние этого JK-триггера не изменяется. Если на J- и К-входах данного JK-триггера имеются единичные уровни, то состояние этого JK-триггера изменяется на противоположное (из нулевого в единичное или наоборот), Если на J входе данного JK-триггера имеется ну

левой уровень, а на его К-входе - единичньй уровень, то этот JK-триггер устанавливается в нулевое состояние (или подтверждается такое состояние). Если на J-входе данного JK-триггера имеется единичный уровень, а на его К-входе - нулевой уровень, то этот JK-триггер устанавливается в единичное состояние (или подтверждается такое состояние),

Используя указанный алгоритм работы JK-триггеров, получим последовательное во времени переключение JK-триггеров 1-4 (фиго 26, в, г, д). После поступления восьмого импульса на шины 5 на прямом выходе JK-триггера- 1 и на инверсном выходе JK-триггера 3 устанавливаются единичные уровни, что приводит к формированию сигнала переноса (фиг. 2е) на выходе элемента 8 (и на шине 9).

После поступления девятого импульса на шину 5 устройство возвращается в исходное состояние. Далее цикл

работы повторяется.

ормула изобретения

Синхронный делитель частоты на 9 на JK-триггерах, содержащий первый, второй, третий и четвертый JK-триггеры, С-входы и R-входы которых соеинены соответственно с тактовой шиной и с шиной сброса, К-входы первого и второго JK тpиггepoв соединены с шиной логической единицы, пря- г-1ые выходы первого и второго JK- триггеров соединены соответственно с первым входом элемента И и с К-вхоом четвертого JK-триггера, и выходную шину, отлича ющийся тем, что, с целью повьпнения быстродействия, инверсный выход первого JK-триггера соединен с J-входом второго JK-триггера и с J- и К-входами третьего JK-триггера, инверсный выход которого соединен с вторь1м входом

элемента И, прямой выход - с J-BXO1

дом четвертого JK-триггера, прямой

выход которого соединен с J-входом первого JK-триггера, при этом выход элемента И соединен с выходной шиной.

О 7 2

L 7

.-ШЛ

L/lAj

/7.

Редактор И.Рыбченко

Составитель А.Соколов

Техред М.ХоданичКорректор М.Шароши

1641/55

Тирад 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5678

L

сриа.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 9 на JK-триггерах | 1987 |

|

SU1444938A1 |

| Синхронный делитель частоты | 1986 |

|

SU1385291A1 |

| Делитель частоты на 10 | 1986 |

|

SU1403364A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

| Синхронный делитель частоты | 1989 |

|

SU1676097A1 |

| Синхронный делитель частоты на 15 на @ -триггерах | 1985 |

|

SU1307585A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Синхронный делитель частоты на 9 | 1986 |

|

SU1378055A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Делитель частоты на 11 | 1987 |

|

SU1522398A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники в синтезаторах частот. Синхронный делитель частоты (СДЧ) на 9 на JK-триггерах содержит JK-триггеры 1-4, шину (Ш) 5 и Ш 6 сброса, Ш 7 логической единицы, элемент И 8 и входную Ш 9. Введение новых электрических связей между функциональными элементами повышает быстродействие СДЧ. 2 ил.

| Будинский Я | |||

| Логические цепи в цифровой технике | |||

| Пер | |||

| с чешек.- М.: Связь, 1977 | |||

| с | |||

| Льночесальная машина | 1923 |

|

SU245A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-30—Публикация

1985-12-18—Подача