дования. С этой целью в устройство, содержащее блоки 1 и 2 памяти микрокоманд, регистры 3 и 4 микрокоманд, элемент ИЛИ 7, элементы И 8 и 9 и триггер 10 пуска, введены блоки элементов ИЛИ 5, 6 и 33, блоки элементов И 11 и 28, элементы 17-22 задержки.

Изобретение относится к вычислительной технике и может быть использовано в процессорах с микропрограммным управлением.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения управления асинхронными объектами и сокращение объема оборудования.

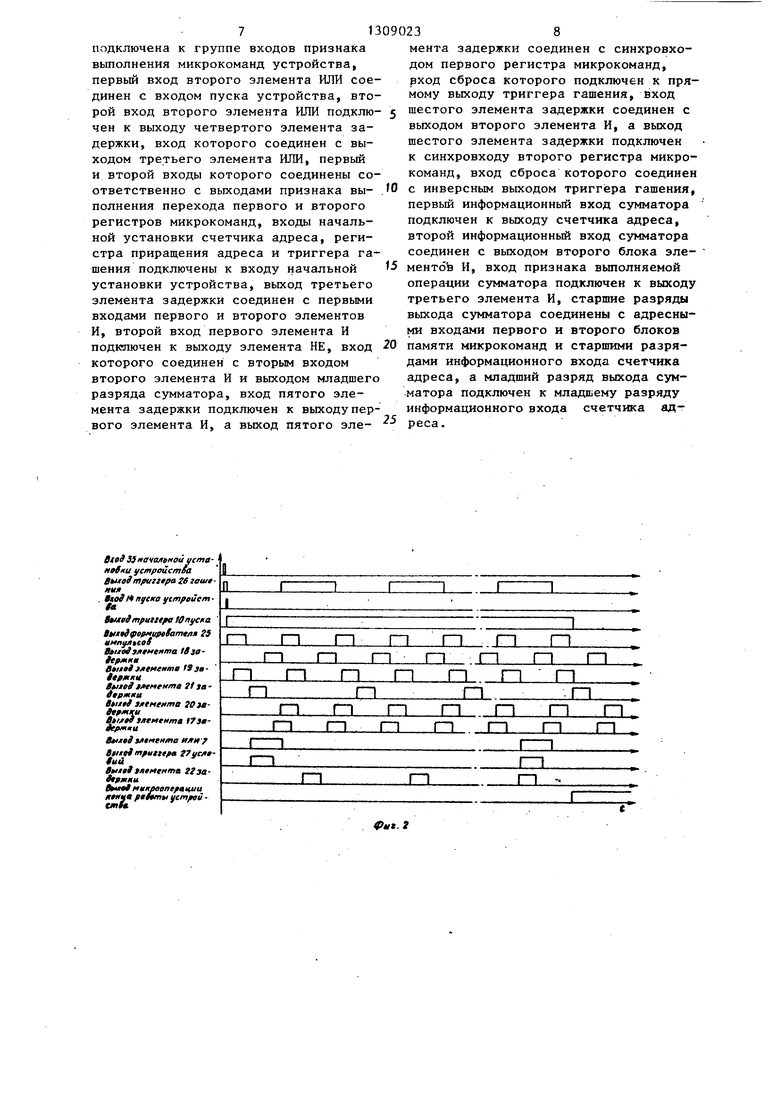

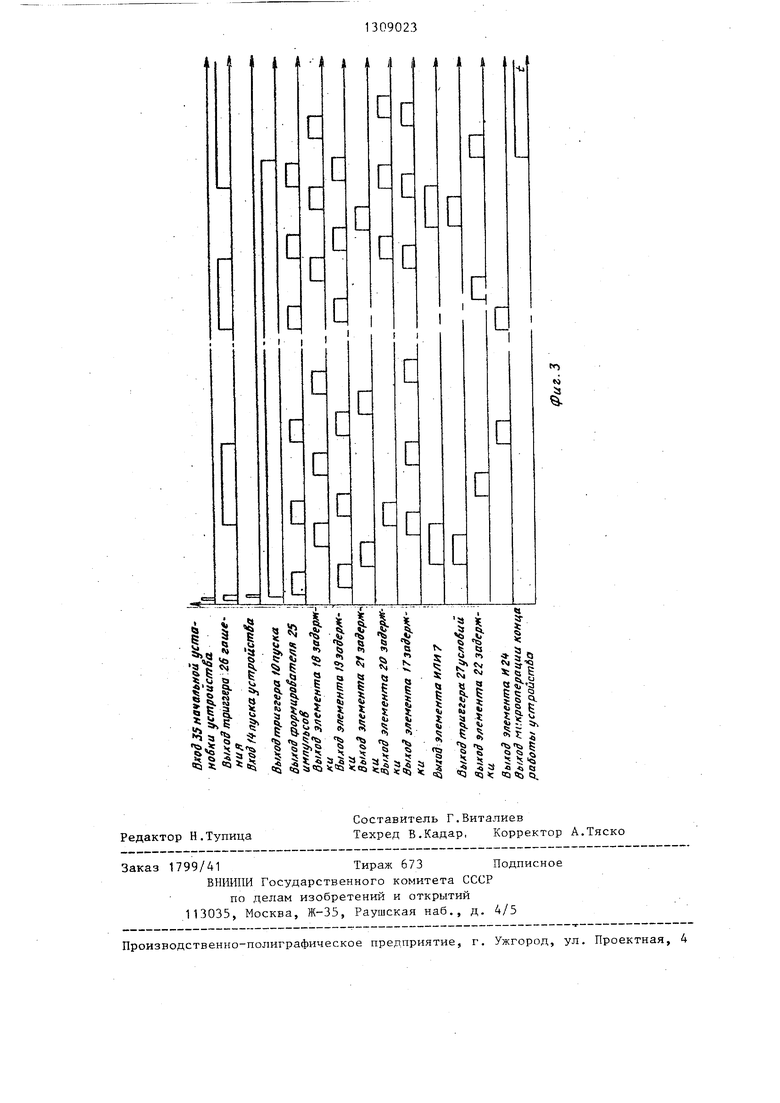

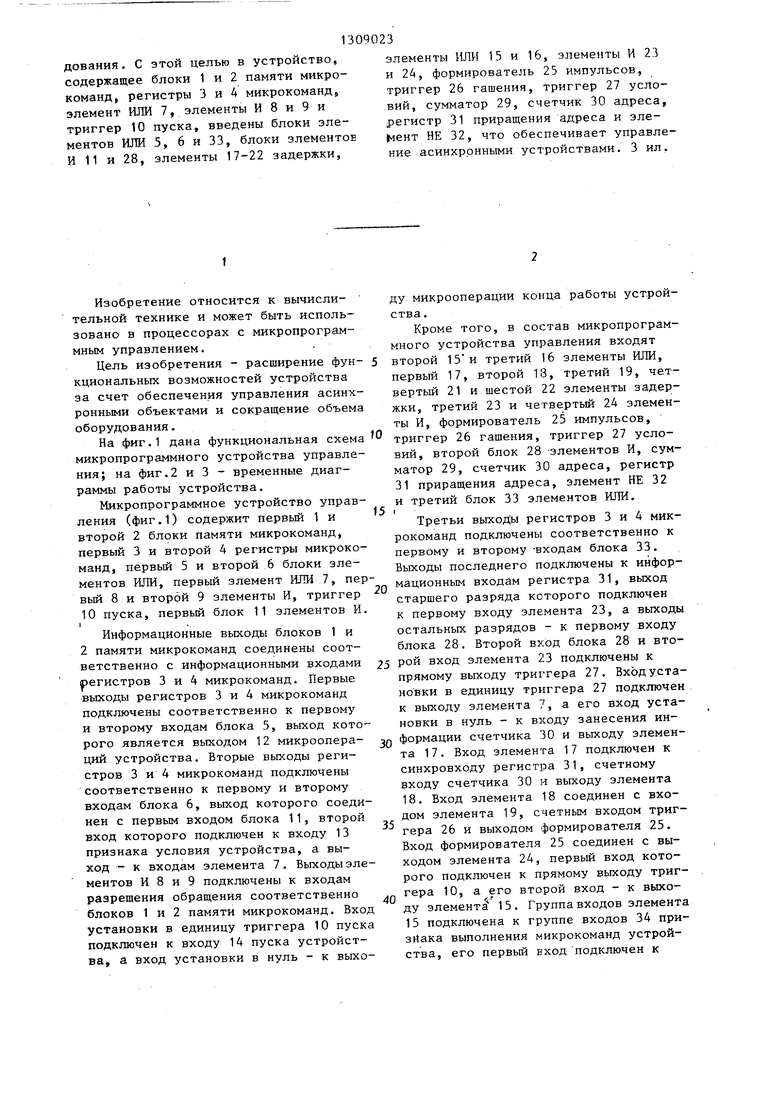

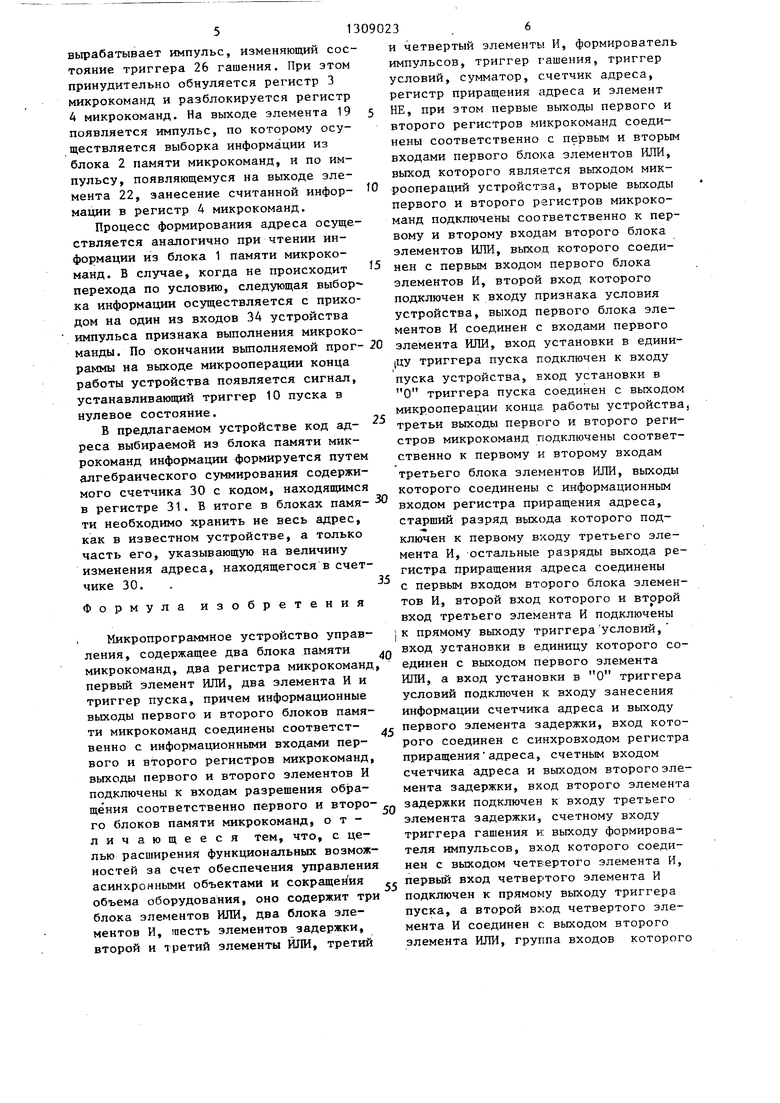

На фиг.1 дана функциональная схема микропрограммного устройства управления ; на фиг.2 и 3 - временные диаграммы работы устройства.

Микропрограммное устройство управления (фиг.1) содержит первый 1 и второй 2 блоки памяти микрокоманд, первый 3 и второй 4 регистры микрокоманд, первый 5 и второй 6 блоки элементов ИЛИ, первьй элемент ИЛИ 7, первый 8 и второй 9 элементы И, триггер

10 пуска, первый блок 11 элементов И I

Информационные выходы блоков 1 и 2 памяти микрокоманд соединены соответственно с информационными входами регистров 3 и 4 микрокоманд. Первые выходы регистров 3 и 4 микрокоманд подключены соответственно к первому и второму входам блока 5, выход которого является выходом 12 микроопераций устройства. Вторые выходы регистров 3 и 4 микрокоманд подключены соответственно к первому и второму входам блока 6, выход которого соединен с первым входом блока 11, второй вход которого подключен к входу 13 признака условия устройства, а выход - к входам элемента 7. Выходы элементов И 8 и 9 подключены к входам разрешения обращения соответственно блоков 1 и 2 памяти микрокоманд. Вход установки в единицу триггера 10 пуска подключен к входу 14 пуска устройства, а вход установки в нуль - к выхоэлементы ИЛИ 15 и 16, элементы И 23 и 24, формирователь 25 импульсов, триггер 26 гашения, триггер 27 условий, сумматор 29, счетчик 30 адреса, регистр 31 приращения адреса и эле- (иент НЕ 32, что обеспечивает управление асинхронными устройствами. 3 ил.

ду микрооперации конца работы устройства.

Кроме того, в состав микропрограммного устройства управления входят

второй 15 и третий 16 элементы ИЛИ, первый 17, второй 18, третий 19, четвертый 21 и шестой 22 элементы задержки, третий 23 и четвертый 24 элементы И, формирователь 25 импульсов,

триггер 26 гашения, триггер 27 условий, второй блок 28 элементов И, сумматор 29, счетчик 30 адреса, регистр 31 приращения адреса, элемент НЕ 32

и третий блок 33 элементов ИЛИ. I

Третьи выходы регистров 3 и 4 микрокоманд подключены соответственно к первому и второму -входам блока 33. Выходы последнего подключены к инфорQ мационным входам регистра 31, выход старшего разряда которого подключен к первому входу элемента 23, а выходы остальных разрядов - к первому входу блока 28. Второй вход блока 28 и вто5 рой вход элемента 23 подключены к

прямому выходу триггера 27. Вход установки в единицу триггера 27 подключен к выходу элемента 7, а его вход установки в нуль - к входу занесения инQ формации счетчика 30 и выходу элемента 17. Вход элемента 17 подключен к синхровходу регистра 31, счетному входу счетчика 30 и выходу элемента 18. Вход элемента 18 соединен с входом элемента 19, счетным входом триггера 26 и выходом формирователя 25. Вход формирователя 25 соединен с выходом элемента 24, первый вход которого подключен к прямому выходу триггера 10, а его второй вход - к выходу элемента 15. Группа входов элемента 15 подключена к группе входов 34 при- эйака выполнения микрокоманд устройства, его первый вход подключен к

0

входу 14 пуска устройства, а второй вход - к выходу элемента 20. Вход элемента 20 подключен к выходу элемента 16, первый и второй входы которого подключены соответственно к выхо дам признака выполнения перехода регистров 3 и 4 микрокоманд. Входы начальной установки счетчика 30, регистра 31 и триггера 26 подключены к входу 35 начальной установки устрой- ства. Выход элемента 19 подключен к первым входам элементов 8 и 9. Второй вход элемента 8 подсоединен к выходу элемента 32, вход которого подключен к второму входу элемента 9 и выходу младшего разряда сумматора 29. Вход элемента 21 подключен к выходу элемента 8, а его выход - к синхровходу регистра 3, вход сброса которого подключен к прямому выходу триггера 26. Вход элемента 22 подсоединен к выходу элемента 9, а его выход - к синхро-.. входу регистра 4, вход сброса которого подключен к инверсному выходу триггера 26. Первый информационный вход сумматора 29 подключен к выходу счетчика 30, его второй информационный вход - к выходу блока 28, вход признака выполняемой операции - к выходу

Информация с первого выхода регистра 3 микрокоманд поступает через блок 5 на выход 12 микроопераций уст ройства. Информация с второго выхода регистра 3 микрокоманд через блок 6 поступает на первый вход блока 11, где сравнивается с поступающими на второй вход блока 11 признаками усло вия, поступающими на входы 13 устрой ства. В случае совпадения на выходе элемента 7 появляется единичный сигнал, устанавливающий триггер 27 усло вий в единичное состояние. Информация с третьего выхода регистра 3 микрокоманд поступает через блок 33 на инфор мационньш вход регистра 31, Импульс, появляющийся на выходе элемента 18,

элемента 23, выходы старших разрядов-- 0 заносит информацию в регистр 31 и

к адресным входам блоков 1 и 2 памяти микрокоманд и старшим информационным входам, с.четчика 30, а выход младшего разряда - к младшему информационному входу счетчика 30.

Устройство работает следующим образом.

Сигнал начальной установки, поступающий на вход 35 устройства, обнуляет счетчик 30 и регистр 31 и устанав-40 полняемой операции (сложение или выливает триггер 26 в состояние, при котором регистр 3 микрокоманд принудительно обнулен выходным сигналом триггера 26. На адресных входах блоков 1 и 2 памяти микрокоманд присут- 45 знака выполняемой операции. Получен- ствует нулевой адрес. Сигнал пуска, результат заносится в счетчик 30

увеличивает содержимое счетчика 30 на единицу.

В случае, когда триггер 27 условий установлен в единицу (выполняется пе- 35 реход по условрш), в сумматоре 29 осуществляется алгебраическое сложение содержимого счетчика 30 и содержимого младших разрядов регистра 31, поступающего через блок 28. Тип вычитание содержимого младщих разрядов регистра 31) определяется содержимым старшего разряда регистра 31, поступающим через элемент 23 на вход припоступающий на вход 14 устройства, устанавливает триггер 10 в единичное состояние. Одновременно этот сигнал проходит через элемент 15 и элемент 50 24 и поступает на вход формирователя 25. Последний вырабатывает импульс, изменяющий состояние триггера 26. В . результате разблокируется регистр 3 микрокоманд и принудительно обнуляет-55 ся регистр 4 микрокоманд.

Импульс, вырабатываемый формирователем 25, поступает также на входы

импульсов, появляющимся на выходе элемента 17.. Этот же импульс обнуляет триггер 27 условий. На выходах сумматора 29 находится код сформированного адреса. I

В случае, когда выполняется переход по условию, потенциал, присутствующий на выходе признака выполнения перехода регистра 3 микрокоманд, проходит через элемент 16, элемент 20, элемент 15 и элемент 24 и появляется на входе формирователя 25. Последний

элементов 18 и 19 задержки. Пройдя через элемент 19, импульс поступает на первые входы элементов 8 и 9. Поскольку на выходе младшего разряда сумматора присутствует нулевой уровень, импульс проходит через элемент 8 на вход разрешения обращения блок 1 памяти микрокоманд. Считываемая из блока 1 памяти информация поступает на информационный вход регистра 3 микркоманд и заносится в него импульсом, поступающим с выхода элемента 21.

Информация с первого выхода регистра 3 микрокоманд поступает через блок 5 на выход 12 микроопераций устройства. Информация с второго выхода регистра 3 микрокоманд через блок 6 поступает на первый вход блока 11, где сравнивается с поступающими на второй вход блока 11 признаками условия, поступающими на входы 13 устройства. В случае совпадения на выходе элемента 7 появляется единичный сигнал, устанавливающий триггер 27 условий в единичное состояние. Информация с третьего выхода регистра 3 микрокоманд поступает через блок 33 на инфор мационньш вход регистра 31, Импульс, появляющийся на выходе элемента 18,

заносит информацию в регистр 31 и

полняемой операции (сложение или вызнака выполняемой операции. Получен- результат заносится в счетчик 30

увеличивает содержимое счетчика 30 на единицу.

В случае, когда триггер 27 условий установлен в единицу (выполняется пе- реход по условрш), в сумматоре 29 осуществляется алгебраическое сложение содержимого счетчика 30 и содержимого младших разрядов регистра 31, поступающего через блок 28. Тип выполняемой операции (сложение или вызнака выполняемой операции. Получен- результат заносится в счетчик 30

читание содержимого младщих разрядов регистра 31) определяется содержимым старшего разряда регистра 31, поступающим через элемент 23 на вход приимпульсов, появляющимся на выходе элемента 17.. Этот же импульс обнуляет триггер 27 условий. На выходах сумматора 29 находится код сформированного адреса. I

В случае, когда выполняется переход по условию, потенциал, присутствующий на выходе признака выполнения перехода регистра 3 микрокоманд, проходит через элемент 16, элемент 20, элемент 15 и элемент 24 и появляется на входе формирователя 25. Последний

вьфабатьшает импульс, изменяющий состояние триггера 26 гашения. При этом принудительно обнуляется регистр 3 микрокоманд и разблокируется регистр 4 микрокоманд. На выходе элемента 19 появляется импульс, по которому осуществляется выборка информации из блока 2 памяти микрокоманд, и по импульсу, появляющемуся на выходе элемента 22, занесение считанной информации в регистр 4 микрокоманд.

Процесс формирования адреса осуществляется аналогично при чтении информации из блока 1 памяти микрокоманд. В случае, когда не происходит перехода по условию, следующая выбор ка информации осуществляется с приходом на один из входов 34 устройства импульса признака выполнения микроко

и четвертый элементы И, формирователь импульсов, триггер гашения, триггер условий, сумматор, счетчик адреса, регистр приращения адреса и элемент

5 НЕ, при этом первые выходы первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами первого блока элементов ИЛИ, выход которого является выходом микJO роопераций устройства, вторые выходы первого и второго регистров микрокоманд подключены соответственно к первому и второму входам второго блока элементов ИЛИ, выход которого соеди 5 нен с первым входом первого блока элементов И, второй вход которого подключен к входу признака условия устройства, выход первого блока элементов И соединен с входами первого

манды. По окончании выполняемой прог- 20 элемента ШШ, вход установки в единираммы на выходе микрооперации конца работы устройства появляется сигнал, устанавливающий триггер 10 пуска в нулевое состояние.

В предлагаемом устройстве код гщ- реса выбираемой из блока памяти микрокоманд информации Формируется путем алгебраического суммирования содержи;цу триггера пуска подключен к входу пуска устройства, вход установки в О триггера пуска соединен с выходо микрооперации конца работы устройств третьи выходы первого и второго реги стров микрокоманд подключены соответ ственно к первому и второму входам третьего блока элементов ИЛИ, выходы которого соединены с информационным

мого счетчика 30 с кодом, находящимся

в регистре 31. В итоге в блоках памя- входом регистра приращения адреса, ти необходимо хранить не весь адрес, старший разряд выхода которого под- как в известном устройстве, а только часть его, указывающую на величину изменения адреса, находящегося в счетчике 30. .35

ключен к первому входу третьего элемента И, остальные разряды выхода ре гистра приращения адреса соединены с первым входом второго блока элемен тов И, второй вход которого и второй вход третьего элемента И подключены к прямому выходу триггера условий, вход установки в единицу которого со единен с выходом первого элемента ИЛИ, а вход установки в О триггера условий подключен к входу занесения информации счетчика адреса и выходу с первого элемента задержки, вход кото рого соединен с синхровходом регистр приращения адреса, счетным входом счетчика адреса и выходом второго эл мента задержки, вход второго элемент задержки подключен к входу третьего элемента задержки, счетному входу триггера гапгения и выходу формирователя импульсов, вход которого соединен с выходом четвертого элемента И,

Формула изобретения

Микропрограммное устройство управления, содержащее два блока памяти ,Q микрокоманд, два регистра микрокоманд, первый элемент ИЛИ, два элемента И и триггер пуска, причем информационные выходы первого и второго блоков памяти микрокоманд соединены соответственно с информационными входами первого и второго регистров микрокоманд, выходы первого и второго элементов И подключены к входам разрешения обращения соответственно первого и второго блоков памяти микрокоманд, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения управления

с

50

асинхронными объектами и сокращег ия ,, первый вход четвер того элемента И объема оборудования, оно содержит три подключен к прямому выходу триггера блока элементов ИЛИ, два блока элементов И, шесть элементов задержки, второй и третий элементы ШШ, третий

пуска, а второй вход четвертого эле мента И соединен с выходом второго элемента ИЛИ, группа входов которо

09023 , 6

и четвертый элементы И, формирователь импульсов, триггер гашения, триггер условий, сумматор, счетчик адреса, регистр приращения адреса и элемент

5 НЕ, при этом первые выходы первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами первого блока элементов ИЛИ, выход которого является выходом микJO роопераций устройства, вторые выходы первого и второго регистров микрокоманд подключены соответственно к первому и второму входам второго блока элементов ИЛИ, выход которого соеди 5 нен с первым входом первого блока элементов И, второй вход которого подключен к входу признака условия устройства, выход первого блока элементов И соединен с входами первого

;цу триггера пуска подключен к входу пуска устройства, вход установки в О триггера пуска соединен с выходом микрооперации конца работы устройства, третьи выходы первого и второго регистров микрокоманд подключены соответственно к первому и второму входам третьего блока элементов ИЛИ, выходы которого соединены с информационным

входом регистра приращения адреса, старший разряд выхода которого под-

входом регистра приращения адреса, старший разряд выхода которого под-

ключен к первому входу третьего элемента И, остальные разряды выхода регистра приращения адреса соединены с первым входом второго блока элементов И, второй вход которого и второй вход третьего элемента И подключены к прямому выходу триггера условий, вход установки в единицу которого соединен с выходом первого элемента ИЛИ, а вход установки в О триггера условий подключен к входу занесения информации счетчика адреса и выходу первого элемента задержки, вход которого соединен с синхровходом регистра приращения адреса, счетным входом счетчика адреса и выходом второго элемента задержки, вход второго элемента задержки подключен к входу третьего элемента задержки, счетному входу триггера гапгения и выходу формирователя импульсов, вход которого соединен с выходом четвертого элемента И,

первый вход четвер того элемента И подключен к прямому выходу триггера

пуска, а второй вход четвертого элемента И соединен с выходом второго элемента ИЛИ, группа входов которого

подключена к группе входов признака выполнения микрокоманд устройства, первый вход второго элемента ИЛИ соединен с входом пуска устройства, второй вход второго элемента ИЛИ подключен к выходу четвертого элемента задержки, вход которого соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами признака выполнения перехода первого и второго регистров микрокоманд, входы начальной установки счетчика адреса, регистра приращения адреса и триггера гашения подключены к входу начальной установки устройства, выход третьего элемента задержки соединен с первыми входами первого и второго элементов И, второй вход первого элемента И подключен к выходу элемента НЕ, вход которого соединен с вторым входом второго элемента И и выходом младшего разряда сумматора, вход пятого элемента задержки подключен к выходу первого элемента И, а выход пятого эле20

мента задержки соединен с синхровхо- дом первого регистра микрокоманд, рход сброса которого подключен к прямому выходу триггера гашения, вход

с шестого элемента задержки соединен с выходом второго элемента И, а выход шестого элемента задержки подключен к синхровходу второго регистра микрокоманд, вход сброса которого соединен

0 с инверсным выходом триггера гашения, первый информационный вход сумматора подключен к выходу счетчика адреса, второй информационный вход сумматора соединен с выходом второго блока эле5 ментов И, вход признака выполняемой операции сумматора подключен к выходу третьего элемента И, старшие разряды выхода сумматора соединены с адресными входами первого и второго блоков

0 памяти микрокоманд и старшими разрядами информационного входа счетчика адреса, а младший разряд выхода сумматора подключен к младшему разряду информационного входа счетчика адреса.

Редактор Н.Тупица

Заказ 1799/41Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель Г.Виталиев

Техред В.Кадар, Корректор А.Тяско

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Генератор случайных чисел | 1987 |

|

SU1524048A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1104515A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

Изобретение относится к области вычислительной техники и может быть использовано в процессорах с микропро - граммным управлением. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения управления асинхронными объектами и сокращение объема обору1 3S (Л

| Микропрограммное устройство управления | 1978 |

|

SU705450A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU830384A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-08-13—Подача