1

Изобретение относится к вычислительной технике.

Известно микропрограммное устройсво управления, содержащее триггерял, коммутаторы, элементы И, регистры адреса, запоминающие блоки 1.

Недостаток устройства - избыток оборудования, так как оно содержит два коммутатора и два регистра адреса.

Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее два запоминакяцнх блока, соединённых с соответствующими регистрами адреса, два блока проверки условий, два триггера блокировки и два элемента И 2.

Недостатком данного устройства является избыток оборудования, обусловленный наличием двух блоков проверки, двух триггеров блокировки, двух регистров адреса, работающих поочередно.

Цель изобретения - упрощение устройства..

Цель достигается тем, что в устройство, содержащее запоминающие блки, элементы И, триггер блокировки

и регистр адреса, первый разрядный выход которого соединен с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены с выходами первого и второго Элементов И соответственно, первые входы которых соединены с первым управляющим входом устройства, первые выходы первого и второго за0поминающих блоков соединены с первым и вторым управляющими выходами устройства, введен блок проверки условий, выход которого соединен со входом триггера блокировки выход триггера

5 блокировки соединен со вторыми входами первого и второго элементов И, третий вход первого элемента И соединен со вторым разрядным выходом регистра адреса, третий вход второ0го элемента И соединен с третьим разрядным выходом регистра адреса, первый вход регистра адреса соединен со вторым выходом первого запоминающего блока, второй вход ре5гистра адреса соединен со вторым выходом второго запоминающего блока, третьи выходы первого и второго запоминающих блоков соединены с первым и вторым входами блока проверки условий соответственно, третий вход которого соединен со вторым управляющих входом устройства.

Кроме того, блок проверки условий содержит двр схемы сравнения и элемент ИЛИ, причем первые входы первой и второй схем сравнения соединены соответственно с первым и вторым входами блока, вторые входы первой и второй схем сравнения соединены с третьим входом блока, выходы первой и второй схем сравнения соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого содинен с выходом блока.

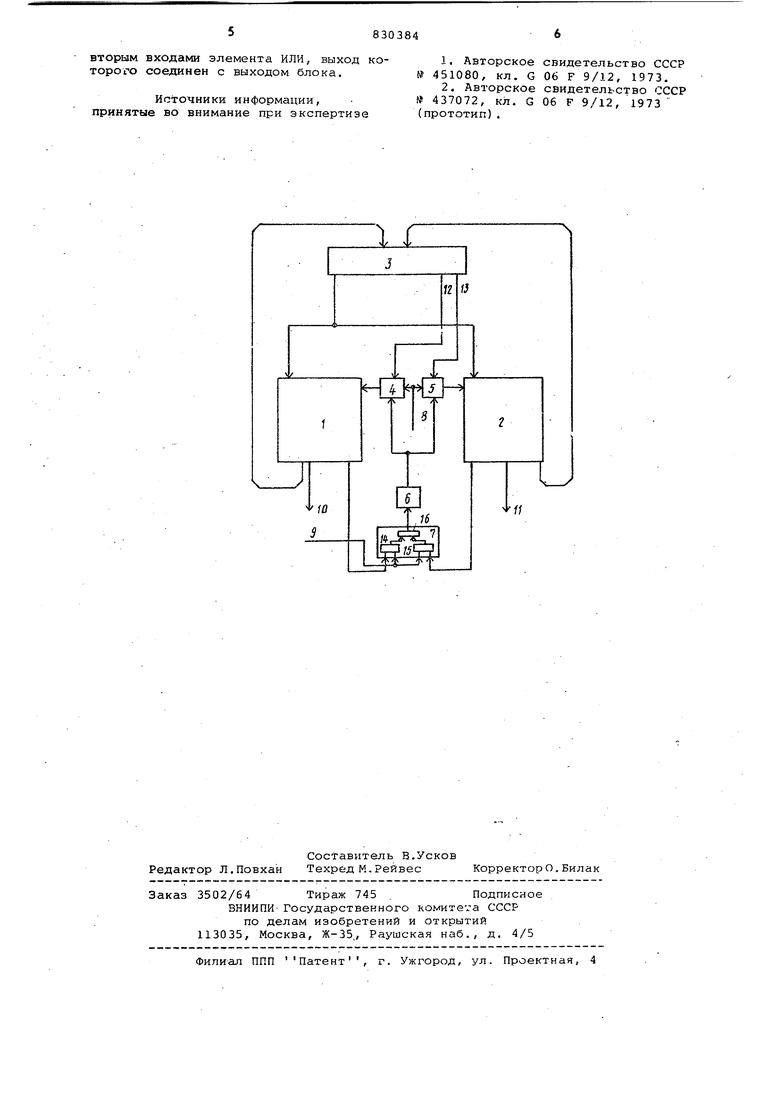

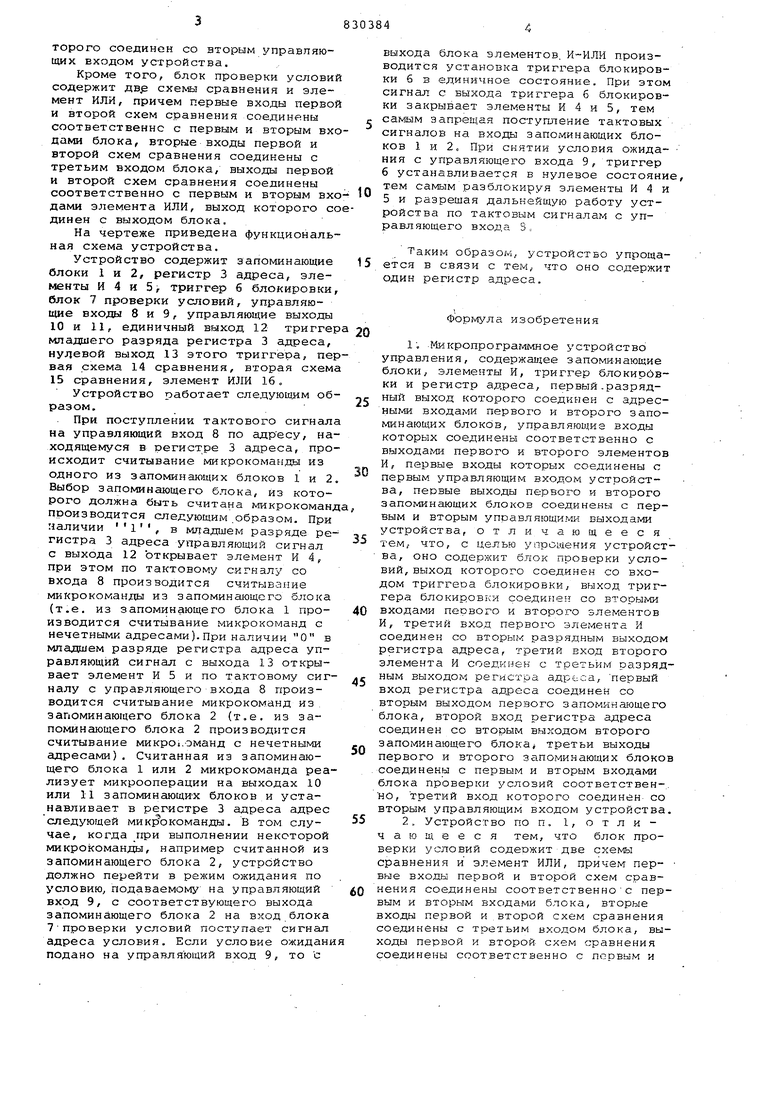

На чертеже приведена функциональная схема устройства.

Устройство содержит запоминающие блоки 1 и 2, регистр 3 адреса, элементы И 4 и 5f триггер б блокировки, блок 7 проверки условий, управляющие входы 8 и 9, управляющие выходы 10 и 11, единичный выход 12 триггер младшего разряда регистра 3 адреса, нулевой выход 13 этого триггера, первая схема 14 сравнения, вторая схема 15 сравнения, элемент ИЛИ 16.

Устройство работает следующим образом.

При поступлении тактового сигнала на управляющий вход 8 по адресу, находящемуся в регистре 3 адреса, происходит считывание микрокоманды из одного из запоминающих блоков 1 и 2, Выбор запоминающего блока, из которого должна быть считана микрокоманд производится следующим .образом. При наличии , в младшем разряде регистра 3 адреса управляющий сигнал с выхода 12 открывает элемент И 4, при этом по тактовому сигналу со входа 8 производится считывание микрокоманды из запоминающего блока (т.е. из запоминающего блока 1 производится считывание микрокоманд с нечетными адресами). При наличии О в младшем разряде регистра адреса управляющий сигнал с выхода 13 открывает элемент И 5 и по тактовому сигналу с управляющего входа 8 производится считывание микрокоманд из, запоминающего блока 2 (т.е. из запоминающего блока 2 производится считывание микрокоманд с нечетными адресами). Считанная из запоминающего блока 1 или 2 микрокоманда реализует микрооперации на выходах 10 или 11 запоминающих блоков и устанавливает в регистре 3 адреса адрес следующей микрокоманды. В том случае, когда при выполнении некоторой микрокоманды, например считанной из запоминающего блока 2, устройство должно перейти в режим ожидания по условию, подаваемому на управляющий вход 9, с соответствующего выхода запоминающего блока 2 на вход блока 7проверки условий поступает сигнал адреса условия. Если условие ожидани подано на управляющий вход 9, то с

выхода блока элементов. производится установка триггера блокировки б в единичное состояние. При этом сигнал с выхода триггера б блокировки закрывает элементы И 4 и 5, тем caNffiiM запрещая поступление тактовых сигналов на входы запоминающих блоков 1 и 2„ При снятии условия ожидания с управляющего входа 9, триггер 6 устанавливается в нулевое состояни тем самым разблокируя элементы И 4 и 5 и разрешая дальнейщую работу устройства по тактовым сигналам с управляющего входа 3

Таким образом, устройство упрощается в связи с тем, что оно содержит один регистр адреса.

изобретения

1; Микропрограммное устройство управления, содержащее запоминающие блоки, элементы И, триггер блокировки и регистр адреса, первый.разрядный выход которого соединен с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены с первым управляющим входом устройства, первые выходы первого и второго запоминающих блоков соединены с первым и вторым управляющими выходами устройства, отличающееся тем,- что, с целью упрощения устройства, оно содержит блок проверки условий, выход которого соединен со входом триггеоа блокировки, выход триггера блокировки соединен со вторыг и входами первого и второгО злементов И, третий вход первого элемента И соединен со вторым разрядным выходом регистра адреса, третий вхо.ц второго элемента И соедкнек с третьим разрядным выходом регистра адреса, первый вход регистра адреса соединен со вторым выходом первого запоминающего блока, второй вход регистра адреса соединен со вторым выходом второго запоминающего блока третьи выходы первого и второго запоминающих блоко соединены с первым и вторым входами блока проверки условий соответственно, третий вход которого соединен со вторым управляющим входом устройства

2. Устройство по п. 1, отличающееся тем, что блок проверки условий содеожит две схемы сравнения и элемент ИЛИ, причем первые входы первой и второй схем сравнения соединены соответственнос первым и вторым входами блока, вторые входы первой и второй схем сравнения соединены с третьим входом блока, выходы первой и второй схем сравнения соединены соответственно с первым и

вторым входаАш элемента ИЛИ, выход которого соединен с выходом блока,

Источники информации, принятые во внимание при экспертизе

свидетельство СССР 06 F 9/12, 1973.

свидетельство СССР 06 F 9/12, 1973

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1972 |

|

SU437072A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммный процессор | 1972 |

|

SU474008A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

Авторы

Даты

1981-05-15—Публикация

1979-06-14—Подача