сечение изображения. Использование устройства при решении задач обработки изображений приводит к значительному сокращению времени обработ

1

Изобретение относится к вычислительной технике.

Целью изобретения является повышение производительности.

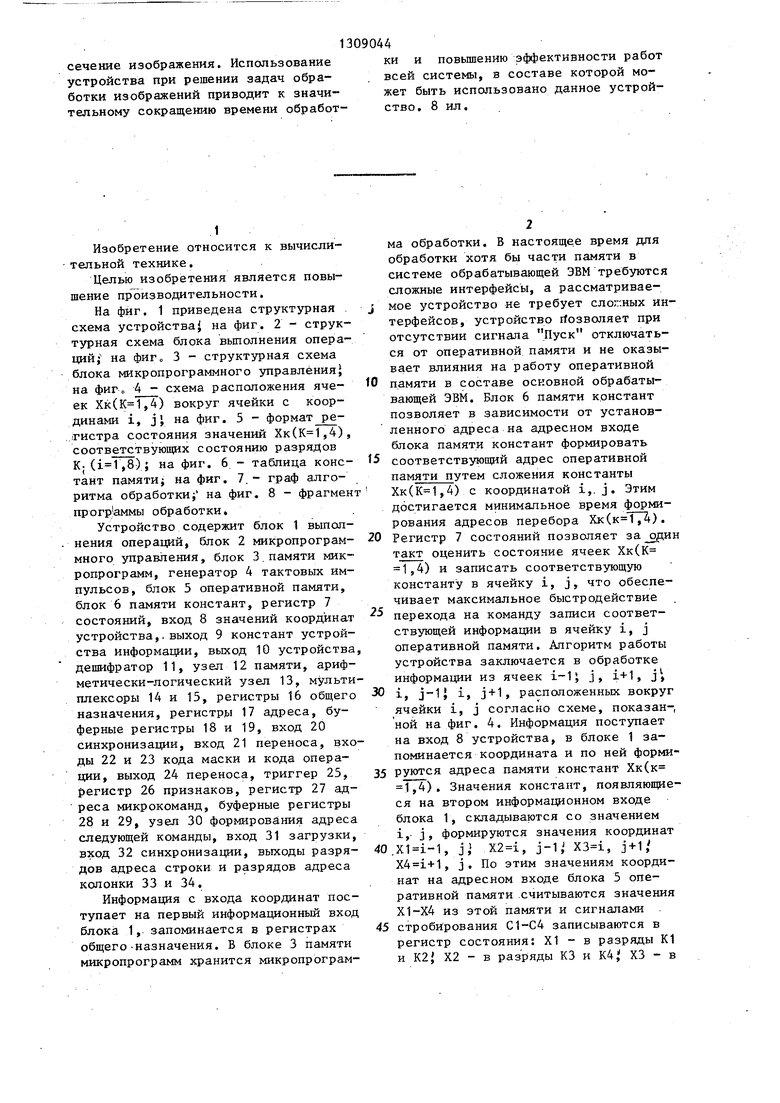

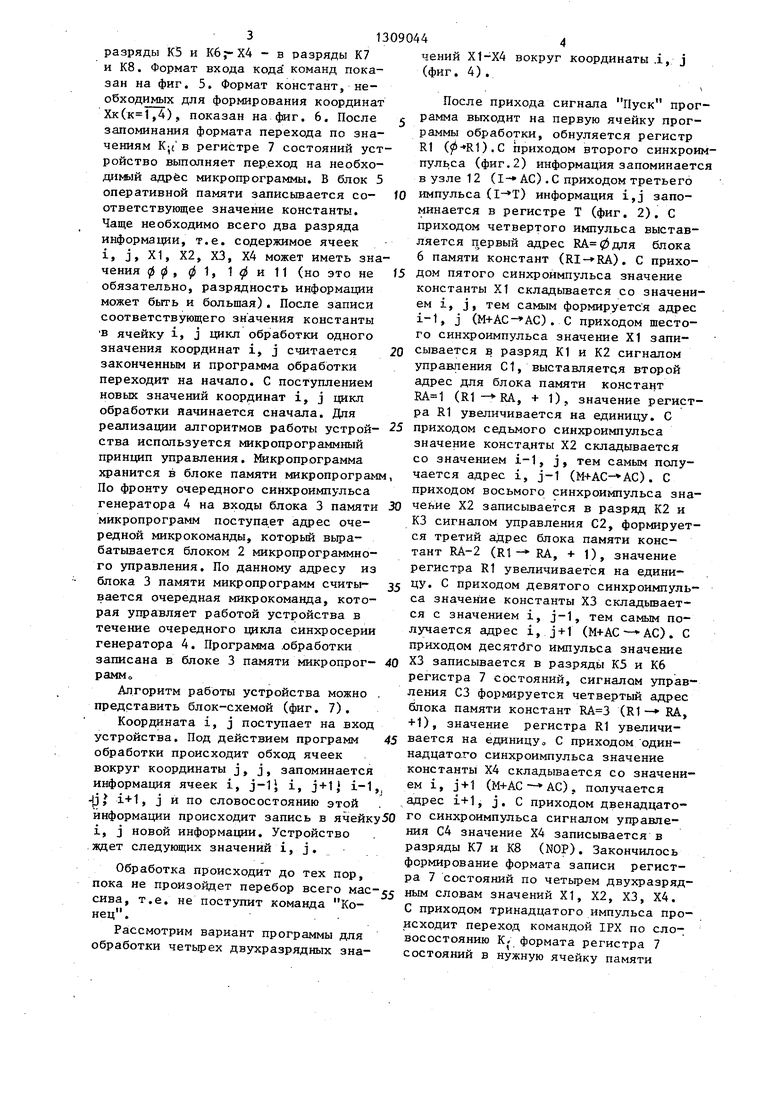

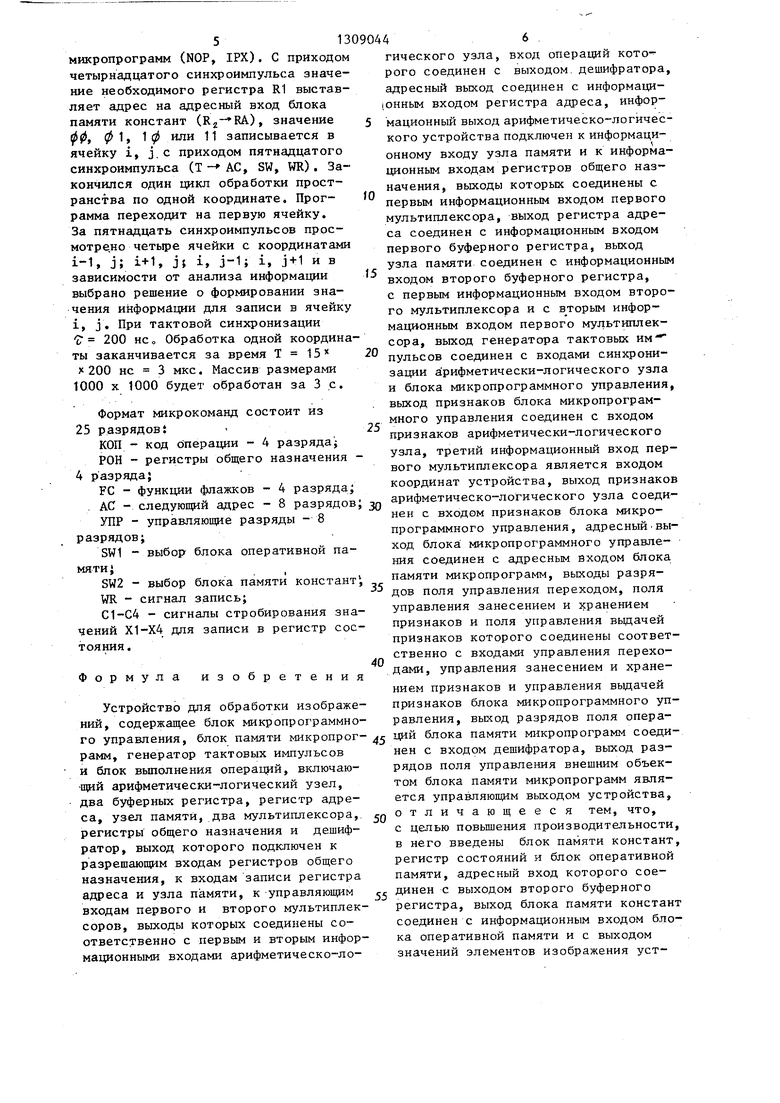

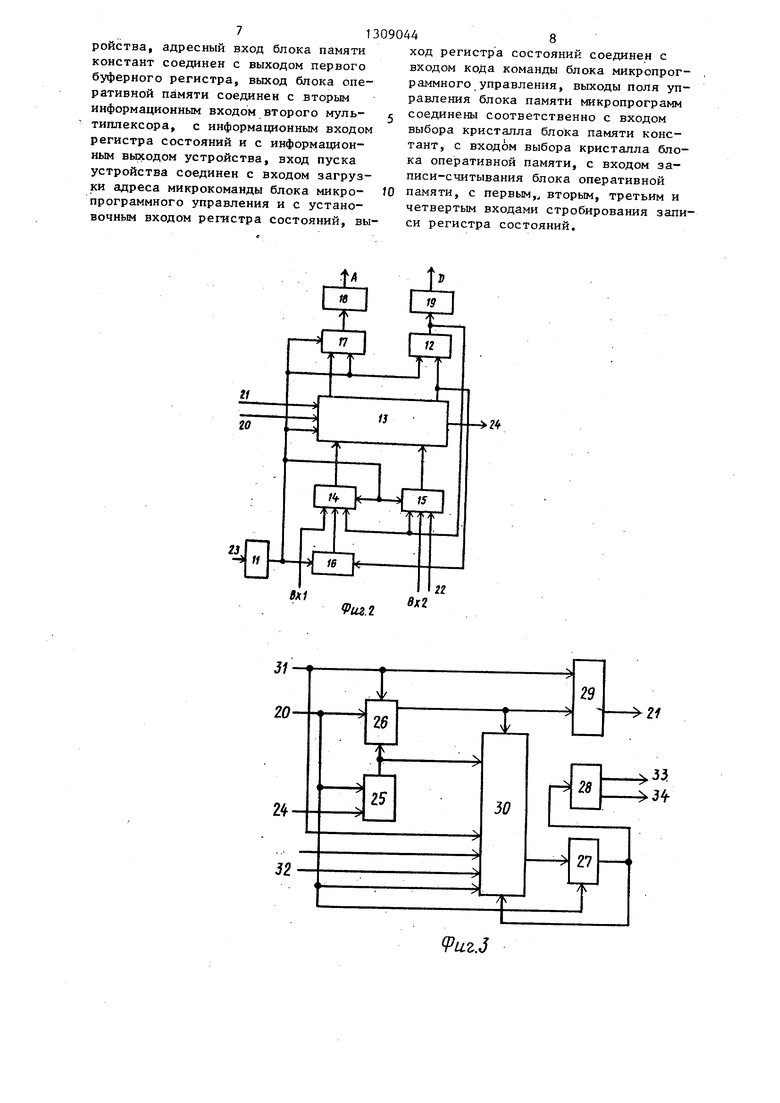

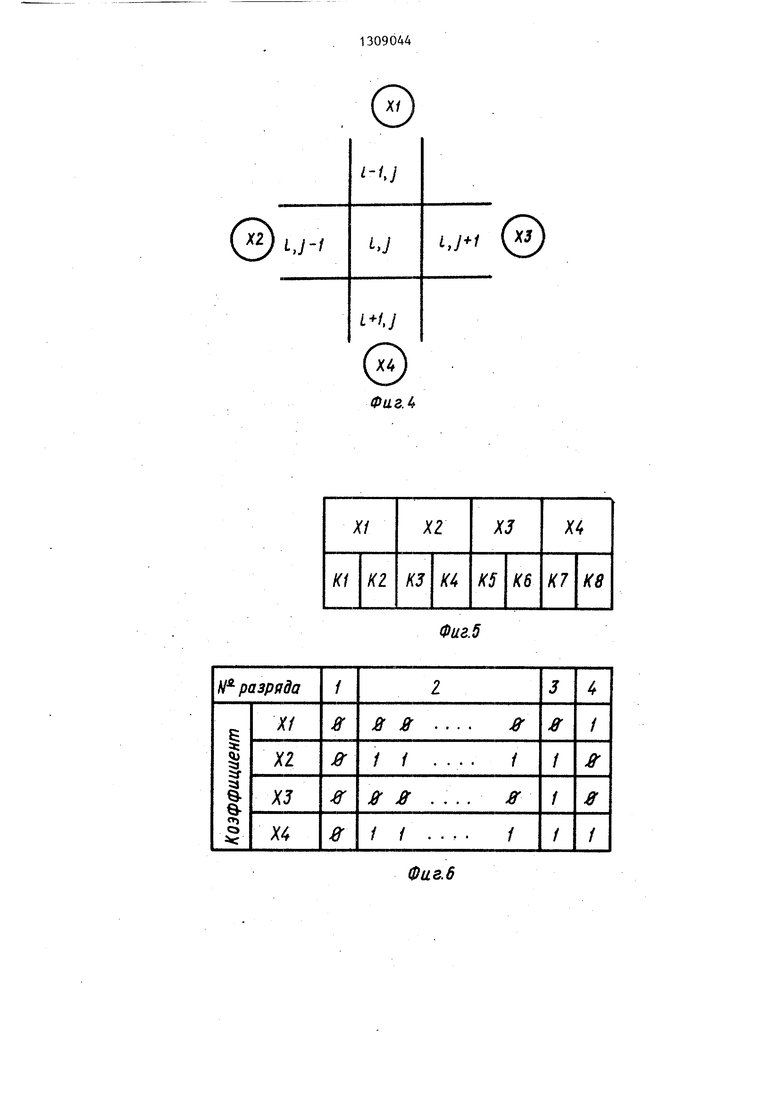

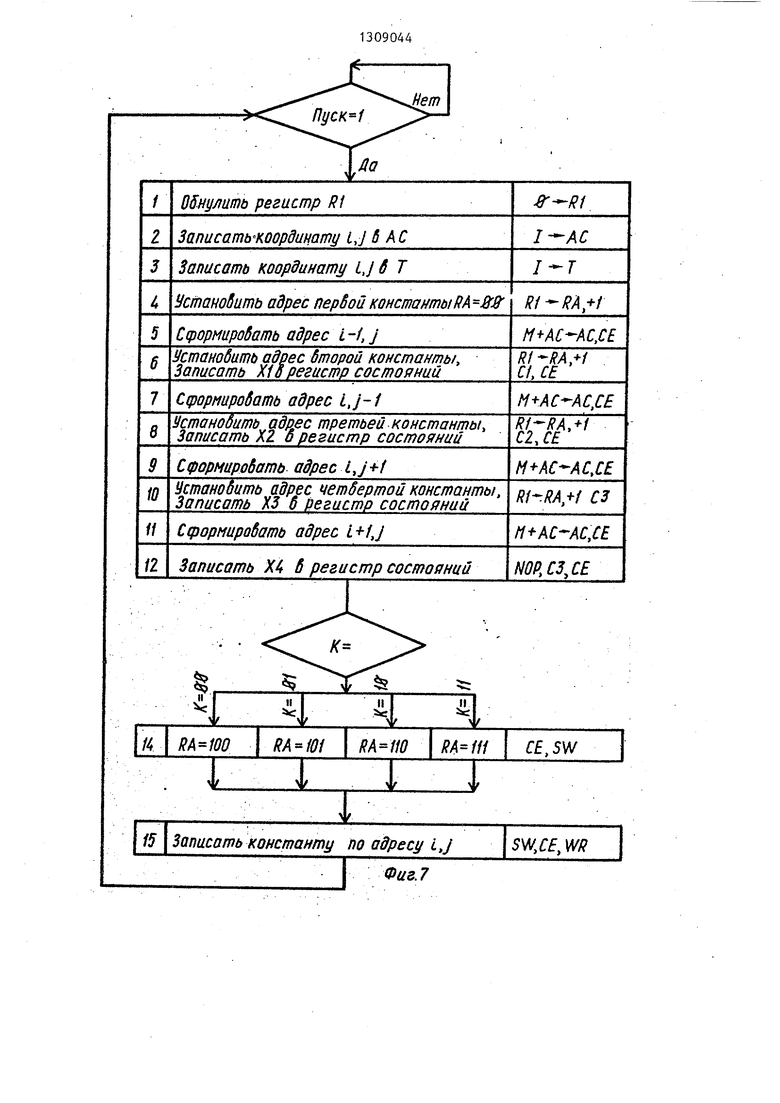

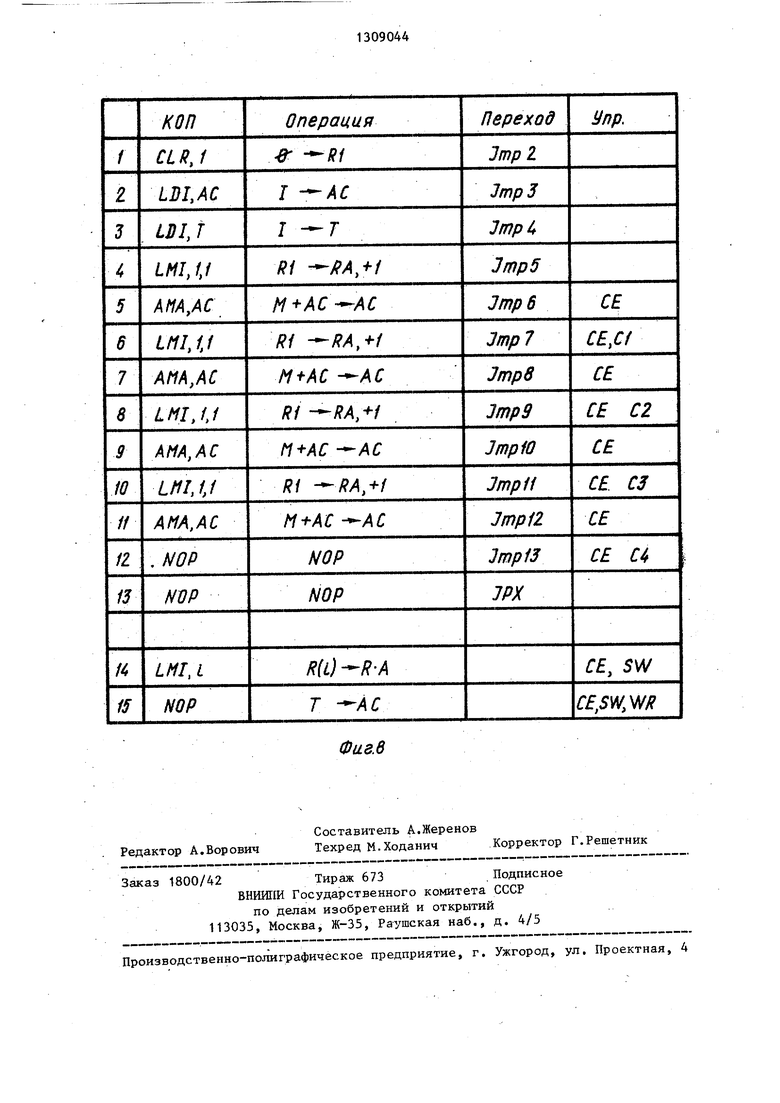

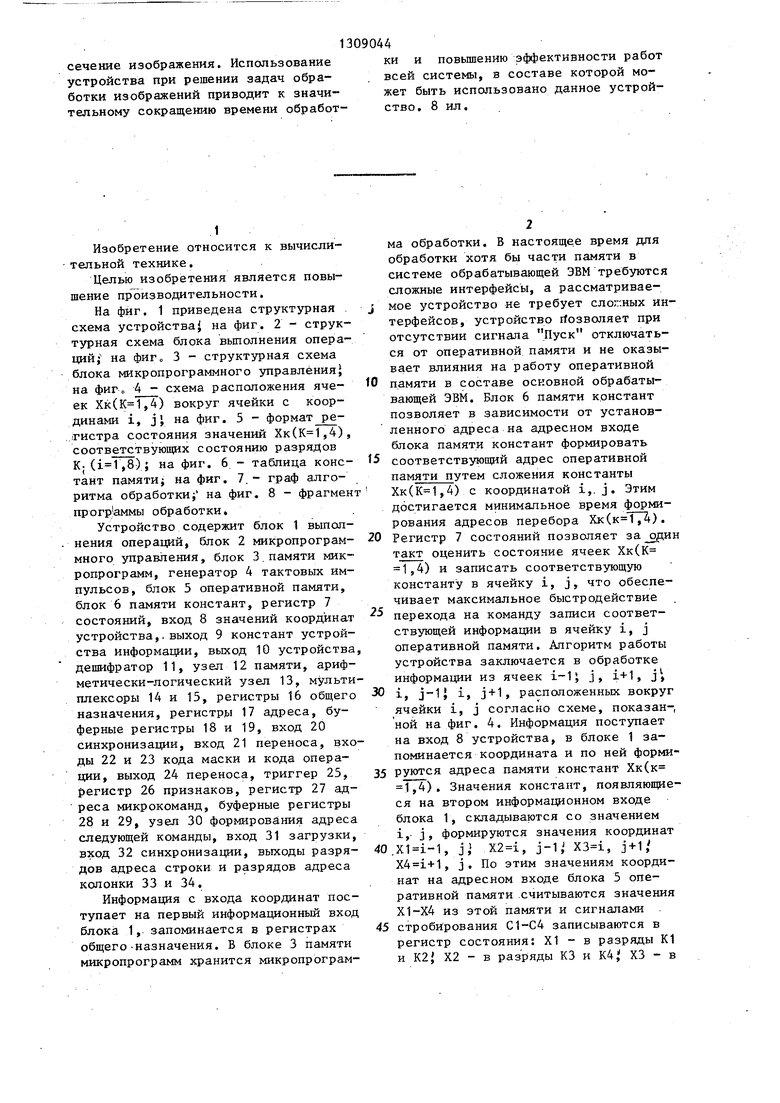

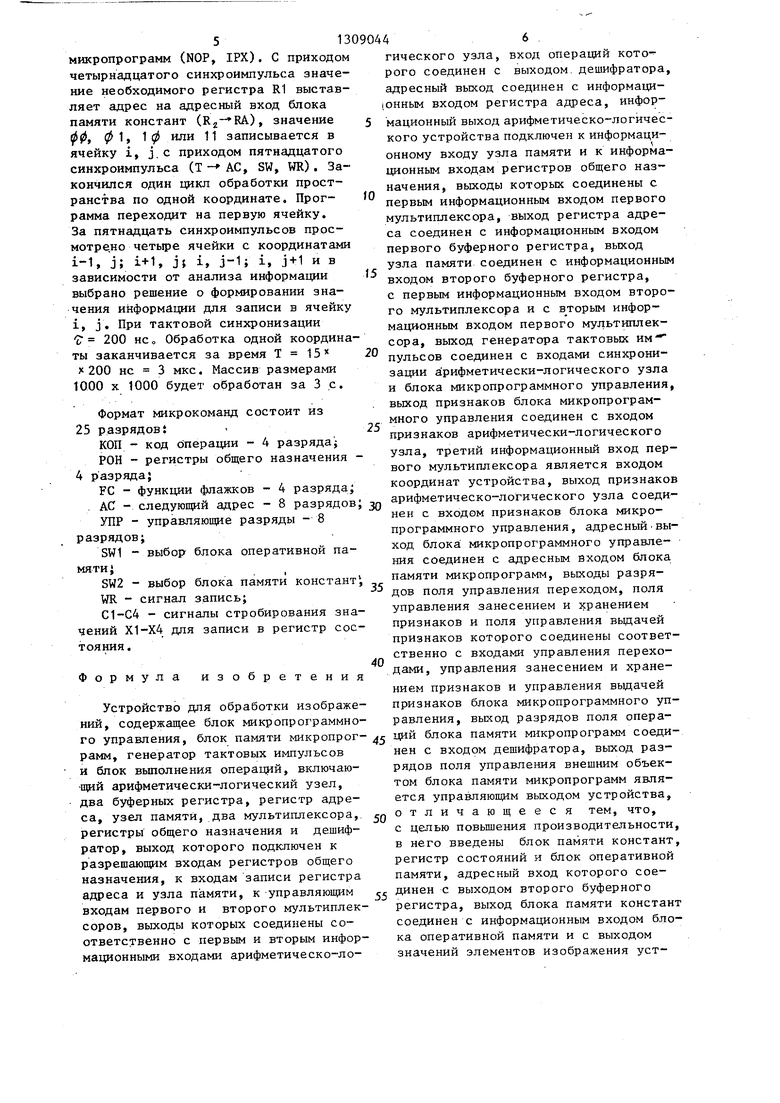

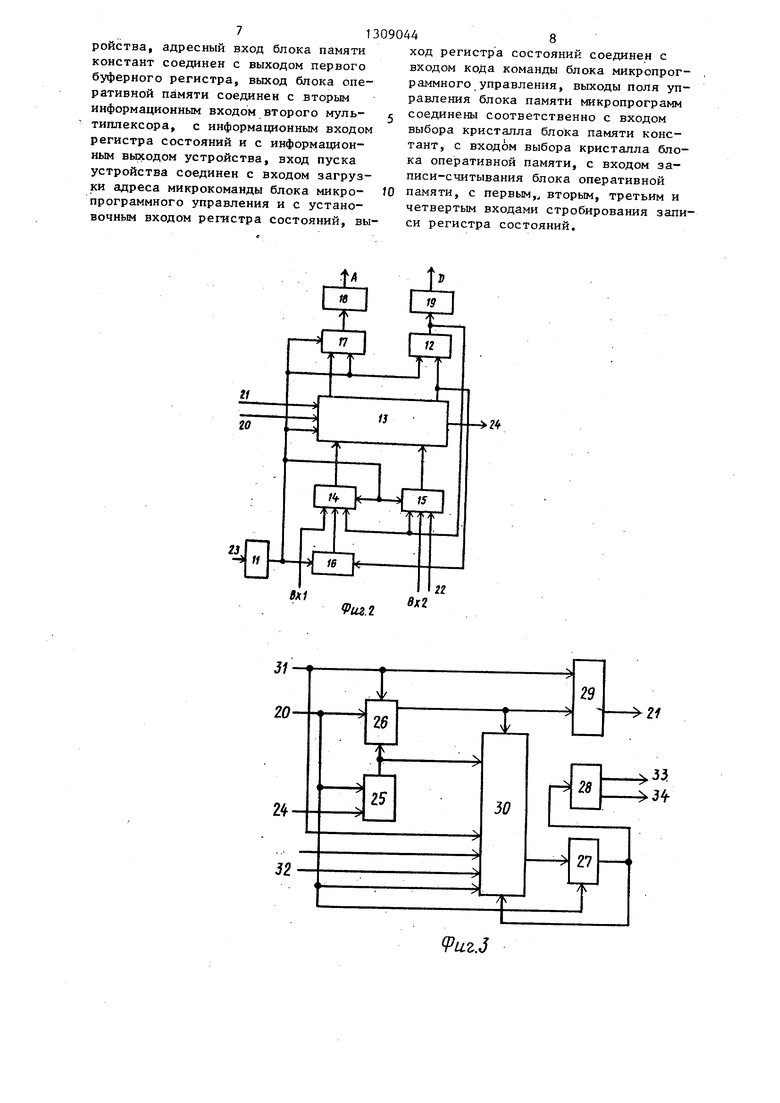

На фиг. 1 приведена структурная . схема устройстваJ на фиг. 2 - структурная схема блока вьшолнения операций; на фиг о 3 - структурная схема блока микропрограммного управленияJ на фиг 4 - схема расположения яче- ек Хк(,4) вокруг ячейки с коор- динами i, j на фиг. 5 - формат ре- гистра состояния значений Хк(,4), соответствуюдр1х состоянию разрядов К.(,8); на фиг. 6. - таблица констант памяти} на фиг. 7,- граф алгоритма обработки; на фиг. 8 - фрагмен прогр аммы обработки.

Устройство содержит блок 1 выполнения операций, блок 2 микропрограммного управления, блок 3.памяти микропрограмм, генератор 4 тактовых импульсов, блок 5 оперативной памяти, блок 6 памяти констант, регистр 7 состояний, вход 8 значений координат устройства,, выход 9 констант устройства Информации, выход 10 устройства дешифратор 11, узел 12 памяти, арифметически-логический узел 13, мультиплексоры 14 и 15, регистры 16 общего назначения, регистры 17 адреса, буферные регистры 18 и 19, вход 20 синхронизации, вход 21 переноса, входы 22 и 23 кода маски и кода операции, выход 24 переноса, триггер 25, регистр 26 признаков, регистр 27 адреса микрокоманд, буферные регистры 28 и 29, узел 30 формирования адреса следующей команды, вход 31 загрузки, вход 32 синхронизации, выходы разря- дон адреса строки и разрядов адреса колонки 33 и 34.

Информация с входа координат поступает на первый информационный вход блока 1, запоминается в регистрах общего-назначения. В блоке 3 памяти микропрограмм хранится микропрограм

ки и повышению эффективности работ всей системы, в составе которой может быть использовано данное устройство. 8 ил.

5

5 0

5

0

5

0

ма обработки. В настояще е время для обработки хотя бы части памяти в системе обрабатывающей ЭВМ требуются сложные интерфейсы, а рассматриваемое устройство не требует сло;::ных интерфейсов, устройство йозволяет при отсутствии сигнала Пуск отключаться от оперативной памяти и не оказывает влияния на работу оперативной памяти в составе основной обрабатывающей ЭВМ. Блок 6 памяти констант позволяет в зависимости от установленного адреса на адресном входе блока памяти констант формировать соответствующий адрес оперативной памяти путем сложения константы Хк(,4) с координатой 1,. j. Этим достигается минимальное время формирования адресов перебора Хк(,4). Регистр 7 состояний позволяет такт оценить состояние ячеек Хк(К 1,4) и записать соответствующую константу в ячейку i, j, что обеспечивает максимальное быстродействие перехода на команду записи соответствующей информации в ячейку i, j оперативной памяти. Апгоритм работы устройства заключается в обработке информации из ячеек 1-1 j, i+1, j i, j-1{ i, j+1, расположенных вокруг ячейки i, j согласно схеме, показан-, ной на фиг. 4. Информация поступает на вход 8 устройства, в блоке 1 запоминается координата и по ней формируются адреса памяти констант Хк(к 1,4). Значения констант, появляющиеся на втором информационном входе блока 1, складываются со значением i,- j, формируются значения координат ., j, , j-l , j + 1, , j. По этим значениям координат на адресном входе блока 5 оперативной памяти .считываются значения Х1-Х4 из этой памяти и сигналами . стробирования С1-С4 записываются в регистр состояния: XI - в разряды К1 и К2{ Х2 - в разряды КЗ и К4, ХЗ - в

разряды К5 и K6j-X4 - в разряды К7 и К8. Формат входа кода команд показан на фиг. 5. Формат констант, не- обходимых для формирования координат Хк(,4), показан на фиг. 6. После запоминания формата перехода по значениям K;t в регистре 7 состояний устройство выполняет пер.еход на необходимый адрес микропрограммы. В блок 5 оперативной памяти записывается со- 10 ответствующее значение константы. Чаще необходимо всего два разряда информации, т.е. содержимое ячеек 1, J, XI, Х2, ХЗ, Х4 может иметь значения 0 , 1, 1 и 11 (но это не f5 обязательно, разрядность информации может быть и большая). После записи соответствующего значения константы В ячейку i, j цикл обработки одного значения координат i, j считается 20 законченным и программа обработки переходит на начало. С поступлением новых значений координат i, j цикл обработки начинается сначала. Для реализации алгоритмов работы устрой- 25 ства используется микропрограммный принцип управления. Микропрограмма хранится в блоке памяти микропрограмм, По фронту очередного синхроимпульса генератора 4 на входы блока 3 памяти 30 микропрограмм поступает адрес очередной микрокоманды, который выра- батьшается блоком 2 микропрограммного управления. По данному адресу из блока 3 памяти микропрограмм считы- 35 вается очередная микрокоманда, которая управляет работой устройства в течение очередного цикла синхросерии генератора 4. Программа .обработки записана в блоке раммо

Алгоритм работы устройства можно представить блок-схемой (фиг. 7).

Координата i, j поступает на вход устройства. Под действием программ обработки происходит обход ячеек вокруг координаты j, j, запоминается информация ячеек i, j-1 i, j + 1, i-1,,

чений XI-X4 вокруг координаты .i, j (фиг. 4).

После прихода сигнала Пуск программа выходит на первую ячейку программы обработки, обнуляется регистр R1 (-«RD.C приходом второго синхроим- (фиг. 2) информация запоминается вузле12 (I- АС) .С приходом третьего импульса () информация i,j запоминается в регистре Т (фиг. 2). С приходом четвертого импульса выставляется первый адрес блока 6 памяти констант (RI-+RA). С приходом пятого синхроимпульса значение константы XI складывается со значением i, j, тем самым формируетс я адрес 1-1, j (М+АС- АС). С приходом шестого синхроимпульса значение XI записывается в разряд К1 и К2 сигналом управления С1, выставляется второй адрес для блока памяти констант (R1 , + 1), значение регистра R1 увеличивается на единицу. С приходом седьмого синхроимпульса значение конста,нты Х2 складывается со значением i-1, j, тем самым получается адрес i, j-1 (М+АС- АС). С приходом восьмого синхроимпульса значение Х2 записывается в разряд К2 и КЗ сигналом управления С2, формируется третий адрес блока памяти констант RA-2 (R1 RA, + 1), значение регистра R1 увеличивается на единицу. С приходом девятого синхроимпульса значение константы ХЗ складьшает- ся с значением i, j-1, тем самым получается адрес i, j + 1 (М+АС- АС). С

приходом десятбго импульса значение 3 памяти микропрог- 40 3 записывается в разряды К5 и Кб

регистра 7 состояний, сигналом управления СЗ формируется четвертый адрес блока памяти констант (R1 НА, +1), значение регистра R1 увеличивается на единицу С приходом один- надцатаго синхроимпульса значение константы Х4 складывается со значением i, j + 1 (М+АС- АС), получается адрес i+1, j. С приходом двенадцато45

-0 i+l j и по словосостоянию этой информации происходит запись в ячейку50 о синхроимпульса сигналом управле- i, j новой информации. Устройство . ™« С4 значение Х4 записывается в

разряды К7 и К8 (NOP). Закончилось формирование формата записи регистра 7 состояний по четьфем двухразряд.ждет следующих значений i, j

разряды К7 и К8 (NOP). Закончилось формирование формата записи регистра 7 состояний по четьфем двухразрядОбработка происходит до тех пор,

пока не произойдет перебор всего мас-55 ным словам значений хГ, Х2, Хз , Х4.

сива, т.е. не поступит команда Ко-с приходом тринадцатого импульса про- неп

исходит переход командой IPX по слоРассмотрим вариант программы длявосостоянию К. формата регистра 7

обработки четырех двухразрядных зна-состояний в нужную ячейку памяти

чений XI-X4 вокруг координаты .i, j (фиг. 4).

После прихода сигнала Пуск программа выходит на первую ячейку программы обработки, обнуляется регистр R1 (-«RD.C приходом второго синхрои (фиг. 2) информация запоминаетс вузле12 (I- АС) .С приходом третьего импульса () информация i,j запоминается в регистре Т (фиг. 2). С приходом четвертого импульса выставляется первый адрес блока 6 памяти констант (RI-+RA). С приходом пятого синхроимпульса значение константы XI складывается со значением i, j, тем самым формируетс я адрес 1-1, j (М+АС- АС). С приходом шестого синхроимпульса значение XI записывается в разряд К1 и К2 сигналом управления С1, выставляется второй адрес для блока памяти констант (R1 , + 1), значение регистра R1 увеличивается на единицу. С приходом седьмого синхроимпульса значение конста,нты Х2 складывается со значением i-1, j, тем самым получается адрес i, j-1 (М+АС- АС). С приходом восьмого синхроимпульса значение Х2 записывается в разряд К2 и КЗ сигналом управления С2, формируется третий адрес блока памяти констант RA-2 (R1 RA, + 1), значение регистра R1 увеличивается на единицу. С приходом девятого синхроимпульса значение константы ХЗ складьшает- ся с значением i, j-1, тем самым получается адрес i, j + 1 (М+АС- АС). С

,

45

о синхроимпульса сигналом управле- ™« С4 значение Х4 записывается в

разряды К7 и К8 (NOP). Закончилось формирование формата записи регистра 7 состояний по четьфем двухразрядным словам значений хГ, Х2, Хз , Х4.

микропрограмм (NOP, IPX), С приходом четырнадцатого синхроимпульса значение необходимого регистра R1 выставляет адрес на адресный вход блока памяти констант (К,), значение

00,01, 10 или 11 записывается в ячейку i, j, с приходом пятнадцатого синхроимпульса (Т- АС, SW, WR). Закончился один цикл обработки пространства по одной координате. Прог- рамма переходит на первую ячейку.

За пятнадцать синхроимпульсов прос- мотре.но четыре ячейки с координатами i-1, j; i+1, j; i, j-1; i, j+1 и в зависимости от анализа информации выбрано решение о формировании значения информации для записи в ячейку

1,j. При тактовой синхронизации

200 НС о Обработка одной координаты заканчивается за время Т 15 х200 НС 3 МКС. Массив размерами 1000 X 1000 будет обработан за 3 с.

гического узла, вход операций кото- рого соединен с выходом, дешифратора, адресный выход соединен с информаци- 10ННЫМ входом регистра адреса, информационный выход арифметическо-логичес- кого устройства подключен к информационному входу узла памяти и к информационным входам регистров общего назначения, выходы которых соединены с первым информационным входом первого мультиплексора, выход регистра адреса соединен с информационным входом первого буферного регистра, выход узла памяти соединен с информационным входом второго буферного регистра, с первым информационным входом второго мультиплексора и с вторым инфор- махщонным входом первого мультиплексора, выход генератора тактовых им- пульсов соединен с входами синхронизации арифметически-логического узла и блока микропрограммного управления, выход признаков блока микропрограммного управления соединен с входом признаков арифметически-логического узла, третий информационный вход первого мультиплексора является входом координат устройства, выход признаков

Формат микрокоманд состоит из 25 разрядовt -25

КОП - код операции - 4 разряда;

РОН - регистры общего назначения - 4 разряда;

FC - функции флажков - 4 разряда

АС - следующий адрес - 8 разрядов; зо арифметическо-логического узла соедиУПР - управляющие разряды - 8 ен с входом признаков блока микроразрядов программного управления, адресный ВЫSW1 - выбор блока оперативной па- «Д блока микропрограммного управлемяти;

. I

SW2 - выбор блока памяти констант ,

WR - сигнал запись;

С1-С4 - сигналы стробирования значений XI-Х4 для записи в регистр состояния.

40 Формула изобретения

35

ния соединен с адресным входом блока памяти микропрограмм, выходы разрядов поля управления переходом, поля управления занесением и хранением признаков и поля управления выдачей признаков которого соединены соответственно с входами управления переходами, управления занесением и хранением признаков и управления выдачей признаков блока микропрограммного управления, выход разрядов поля операУстройство для обработки изображений, содержащее блок микропрограммного управления, блок памяти микропрог- ций блока памяти микропрограмм соединен с входом дешифратора, выход разрядов поля управления внешним объектом блока памяти микропрограмм является управляюш г1м выходом устройства, отличающееся тем, что, с целью повьш1ения производительности, в него введены блок памяти констант, регистр состояний и блок оперативной памяти, адресный вход которого соединен с выходом второго буферного регистра, выход блока памяти констант соединен с информационным входом блока оперативной памяти и с выходом значений элементов изображения устрамм, генератор тактовых импульсов и блок выполнения операций, включаю- -щий арифметически-логический узел, два буферных регистра, регистр адреса, узел памяти, два мультиплексора,. регистры общего назначения и дешифратор, выход которого подкпючен к разрешающим входам регистров общего назначения, к входам записи регистра адреса и узла памяти, к управляющим входам первого и второго мультиплексоров, выходы которых соединены соответственно с первым и вторым информационными входами арифметическо-логического узла, вход операций кото- рого соединен с выходом, дешифратора, адресный выход соединен с информаци- 10ННЫМ входом регистра адреса, информационный выход арифметическо-логичес- кого устройства подключен к информационному входу узла памяти и к информационным входам регистров общего назначения, выходы которых соединены с первым информационным входом первого мультиплексора, выход регистра адреса соединен с информационным входом первого буферного регистра, выход узла памяти соединен с информационным входом второго буферного регистра, с первым информационным входом второго мультиплексора и с вторым инфор- махщонным входом первого мультиплексора, выход генератора тактовых им- пульсов соединен с входами синхронизации арифметически-логического узла и блока микропрограммного управления, выход признаков блока микропрограммного управления соединен с входом признаков арифметически-логического узла, третий информационный вход первого мультиплексора является входом координат устройства, выход признаков

«Д блока микропрограммного управле40

35

ния соединен с адресным входом блока памяти микропрограмм, выходы разрядов поля управления переходом, поля управления занесением и хранением признаков и поля управления выдачей признаков которого соединены соответственно с входами управления переходами, управления занесением и хранением признаков и управления выдачей признаков блока микропрограммного управления, выход разрядов поля опера ций блока памяти микропрограмм соеди50

55

нен с входом дешифратора, выход разрядов поля управления внешним объектом блока памяти микропрограмм является управляюш г1м выходом устройства, отличающееся тем, что, с целью повьш1ения производительности, в него введены блок памяти констант, регистр состояний и блок оперативной памяти, адресный вход которого соединен с выходом второго буферного регистра, выход блока памяти констант соединен с информационным входом блока оперативной памяти и с выходом значений элементов изображения устройства, адресный вход блока памяти констант соединен с выходом первого буферного регистра, выход блока оперативной памяти соединен с вторьм информационным входом второго мультиплексора, с информационным входом регистра состояний и с информационным выходом устройства, вход пуска устройства соединен с входом загрузки адреса микрокоманды блока микропрограммного управления и с установочным входом регистра состояний, вы

ход регистра состояний соединен с входом кода команды блока микропрограммного управления, выходы поля управления блока памяти микропрограмм соединены соответственно с входом выбора кристалла блока памяти констант, с входом выбора кристалла блока оперативной памяти, с входом записи-считывания блока оперативной памяти, с первым, вторым, третьим и четвертым входами стробирования записи регистра состояний.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммный процессор | 1985 |

|

SU1312595A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1495789A1 |

Изобретение относится, к вычислительной технике. Целью изо етения является повышение производительности. Устройство содержит блок 1 выполнения операций, блок 2 микропрограммного управления, блок 3 памяти микрокоманд, генератор 4 тактовых импульсов, блок 5 оперативной памяти, блок 6 памяти констант, регистр 7 сост-ояний, вход 8 координат, вход 9 координат, информационнь й выход 10. Устройство обрабатывает массив информации 6 памяти, которая является памятью ЭВМ и в которой массив данных может нести информацию об одном конкретном участии, например конкретное с «е (Л 00 о со о 4 4

Р

(Puz.J

Фиг.5

Фа г. 6

AQ

§

:

(

II

sL

II

5с

f

/4

/еХ /i / I I f,5W I

1

i

U5 Записать KOffcma/f/ni/ no адресу IJ5W,rf,VW

II

5с

f

.7

Фа 8.6

Редактор А.Ворович

Составитель Л.Жеренов

Техред М.ХоданичКорректор Г.Решетник

Заказ 1800/42Тираж 673Подписное

ВНИЖШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Многофункциональное устройство для логической обработки бинарных изображений | 1983 |

|

SU1136179A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США 4060719, кп | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Березенко А.И | |||

| и др | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Радио и связь, 1981, с | |||

| Приспособление, заменяющее сигнальную веревку | 1921 |

|

SU168A1 |

| Лл./ | |||

Авторы

Даты

1987-05-07—Публикация

1985-12-13—Подача