Изобретение относится к запоминающим устройствам (ЗУ) и может быть использовано при создании больших интегральных схем памяти (БИС ЗУ).

Цель изобретения - повышение быстродействия устройства.

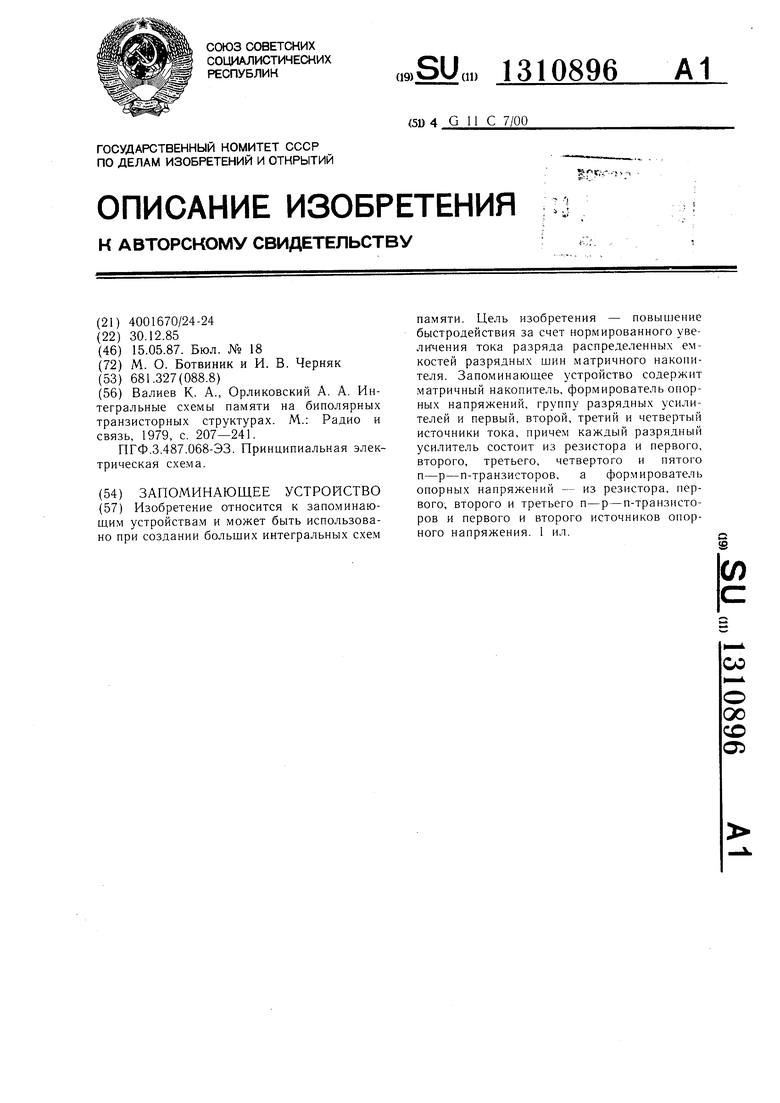

На чертеже приведена функциональная схема устройства.

Устройство содержит матричный накопитель 1, формирователь 2, опорных напряжений, группу разрядных усилителей 3 и первый 4, второй 5, третий 6, четвертый 7 источники тока. Разрядный усилитель 3 состоит из резистора 8, первого 9, второго 10, третьего 11, четвертого 12 и пятого 13 п-р-п-транзисторов. Формирователь 2 опорных напряжений состоит из резистора 14, первого 15, второго 16, третьего 17 п-р-п-транзисторов и первого 18 и второго 19 Источников опорного напряжения. Кроме того, на чертеже обозначены элементы 20 памяти (ЭП), разрядные 21 и словарные 22 шины, шина 23 питания, паразитные емкости 24 разрядных шин, управляюш,ие входы 25 и 26 разрядных усилителей 3.

Запоминающее устройство работает следующим образом.

Пусть один разрядный усилитель 3 с входом управления 25 был ранее выбран, а в данный момент времени происходит переходный процесс выбора другого разрядного усилителя 3 с входом управления 25 (т. е. Уюм Vexze ) Напряжение на разрядных шинах 21, ранее выбранного столбца ЭП 20 из-за наличия распределенных емкостей шин 24 остается ниже, чем на разрядных шинах 24 вновь выбранного столбца. При этом происходит заряд емкостей разрядных шин 24 по цепи: шина 23 питания, резистор 8, коллектор-эмиттер транзистора 17, коллектор-эмиттер транзисторов 9 и 10, распределенная емкость 21, общая шина. За счет протекания тока заряда напряжение на базе транзистора 16 уменьшается на величину ДУбт is(t)Rw .

Из схемы устройства видно, что транзисторы 11 и 12 (аналогично как и такие же транзисторы в другом разрядном усилителе 3) вместе с транзистором 16 образуют дифференциальный каскад с источником 7 тока.

Во время снижения напряжения на базе транзистора 16 выполняется условие Уб5(2б та и через транзисторы 11 и 12 протекает дополнительный ток, определяемый источником 7 тока, обеспечивая ускоренный разряд распределенных емкостей 21 разрядных щин 24 вновь выбираемого разрядного усилителя 3 по цепи: разрядная шина 24, коллектор - первый эмиттер транзистора 11, источник 4 тока, общая шина и параллельно разрядная шина 24, коллектор - второй эмиттер транзистора 11, источник 4 тока, общая шина.

5

Цепь разряда второй разрядной шины 24: коллектор - первый эмиттер транзистора 12, источник 5 тока, общая шина и параллельно - коллектор - второй эмиттер

транзистора 12, источник 7 тока, общая шина.

После окончания заряда емкостей ранее выбранного столбца ЭП 20 напряжение на базе транзистора 16 повысится и будет оп0 ределяться выражением

Увпб Ул - V« ,

гдеУ(8 -напряжение первого опорного источника 18. При выполнении условия: VBT« дополнительный ток разряда емкостей разрядных шин вновь выбранного столбца ЭП 20 прекратится, а ток, задаваемый источником 4 тока протекает по цепи: шина питания, коллектор-эмиттер транзистора 16, источник 4 тока, обшая шина.

Для исключения влияния паразитной ем0 кости первой шины опорного напряжения на время существования дополнительного тока разряда емкостей разрядных шин вновь выбираемого столбца ЭП 20. в формирователь опорных напряжений введен дополнительный транзистор 17 с напряжением на базе, определяемым вторым источником 19 опорного напряжения. Это обеспечивает практически постоянное напряжение на первой шине опорного напряжения во время переходного процесса выбора столбца ЭП

Q 20. Цепь, содержащая транзистор 10, вторую шину опорного напряжения, резистор 14, транзисторы 9, 10 и 13 и источник 6 тока, определяет напряжение на разрядных шинах невыбранного столбца, а также обеспечивает снижение напряжения на эмит5 терах транзисторов 9 и 10 до уровня ниже, чем уровни управления выбранным элементом памяти на разрядных шинах при записи и считывании.

Из приведенного описания запоминающего устройства следует, что устройство обеспечивает нормированное увеличение тока разряда распределенных емкостей разрядных шин вновь выбираемого столбца ЭП 20 на время сушествования тока заряда таких же емкостей ранее выбранного столбца

5 ЭП 20.

Использование предлагаемого устройства позволяет проводить быстрый разряд паразитных емкостей разрядных шин нормированным увеличением тока вновь выбираемого столбца ЭП 20, а затем перейти на огра0 ниченный ток столбца, обеспечивающий необходимую для надежного функционирования величину разности напряжений между разрядными щинами при считывании информации.

55

Формула изобретения

Запоминающее устройство, содержащее матричный накопитель, формирователь опорных напряжений, группу разрядных усилителей и первый, второй и третий источники тока, первые выводы которых соединены с общей шиной устройства, а вторые - соответственно с первой, второй и третьей управляющими щинами выборки устройства, формирователь опорных напряжений выполнен на одном п-р-п-транзисторе, база и коллектор которого соединены с щиной питания устройства, а эмиттер - с первой щиной опорного напряжения устройства, каждый разрядный усилитель состоит из первого, второго, третьего, четвертого и пятого п-р-п-транзисторов и резистора, один вывод которого соединен с первой щиной опорного напряжения устройства, а второй вывод - с коллектором пятого и базами первого и второго п-р-п-транзисторов, коллекторы которых соединены с второй щиной опорного напряжения устройства, а эмиттеры - с соответствующими разрядными шинами столбца матричного накопителя того же разряда и соответственно с коллекторами третьего и четвертого п-р-п- транзисторов того же разрядного усилителя, базы которых и база пятого п-р-п-тран- зистора объединены и являются управляющим входом выборки соответствующего разрядного усилителя, а эмиттеры этих транзисторов соединены соответственно с

22

го

первой, второй и третьей управляющими шинами выборки устройства, отличающееся тем, что, с целью повыщения быстродействия, в него введен четвертый источник

тока, третий и четвертый п-р-г-транзис- торы каждого разрядного усилителя выполнены двухэмиттерными, а в формирователь опорных напряжений введены второй и третий п-р-п-транзисторы, резистор и пер0 вый и второй источники опорного напряжения, причем отрицательный вывод первого источника опорного напряжения соединен с базой второго п-р-п-транзистора, а положительный вывод - с одним выводом резистора и коллектором второго п-р-п- транзистора, эмиттер которого соединен с второй щиной опорного напряжения, а база - с положительным выводом второго источника опорного напряжения, отрицательный вывод которого соединен с общей щи0 ной устройства, второй вывод резистора соединен с щиной питания устройства и коллектором второго п-р-н-транзистора в каждом разряде усилителя, эМиттер которого соединен с вторыми эмиттерами третьего и четвертого п-р-п-транзисторов каждого разрядного усилителя и первым выводом четвертого источника тока, второй вывод которого соединен с общей щикой устройства.

5

5

п

J

гг

/

нн

нн

Н

Z3

Й70i i

t-J

7 4 б S/

Составитель В. Лапшинский

Редактор Т. ПарфеноваТехред И. ВересКорректор И. Эрдейи

Заказ 1763/49Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

г 1

1 fff

/ /

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Формирователь сигналов считывания | 1984 |

|

SU1238152A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Формирователь прямоугольных импульсов | 1983 |

|

SU1112540A1 |

| Запоминающее устройство | 1983 |

|

SU1171848A1 |

Изобретение относится к запоминающим устройствам и может быть использовано при создании больших интегральных схем памяти. Цель изобретения - повышение быстродействия за счет нормированного уве- ли чения тока разряда распределенных емкостей разрядных шин матричного накопителя. Запоминающее устройство содержит матричный накопитель, формирователь опорных напряжений, группу разрядных усилителей и первый, второй, третий и четвертый источники тока, причем каждый разрядный усилитель состоит из резистора и первого, второго, третьего, четвертого и пятого п-р-п-транзисторов, а формирователь опорных напряжений - из резистора, первого, второго и третьего п-р-п-транзисторов и первого и второго источников опорного напряжения. 1 ил. со о 00 со 05

| Валиев К | |||

| А., Орликовский А | |||

| А | |||

| Интегральные схемы памяти на биполярных транзисторных структурах | |||

| М.: Радио и связь, 1979, с | |||

| Станок для изготовления из дерева круглых палочек | 1915 |

|

SU207A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Принципиальная электрическая схема. | |||

Авторы

Даты

1987-05-15—Публикация

1985-12-30—Подача