Изобретение относится к вычислительной технике и может найти применение при построении микросхем памяти большой информационной емкости.

Цель изобретения - снижение потребляемой мощности и повышение быстродействия устройства.

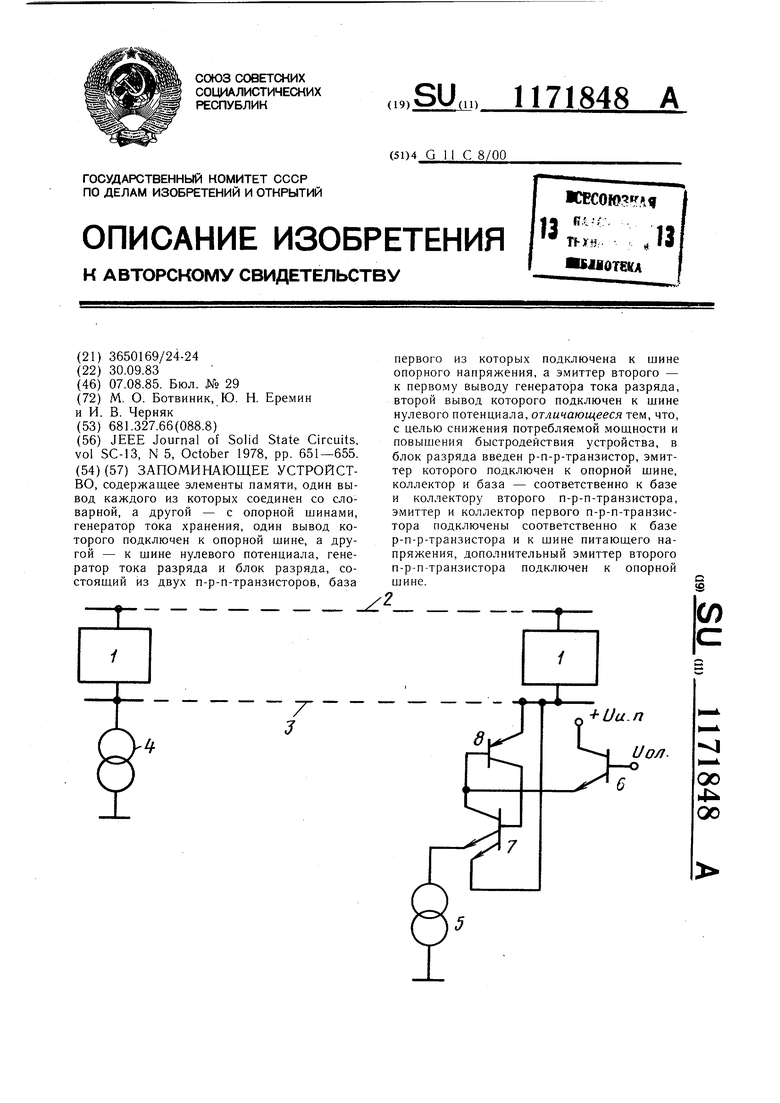

На чертеже изображена электрическая схема запоминающего устройства.

Запоминающее устройство содержит элементы 1 памяти, один вывод каждого из которых соединен со словарной шиной 2, а другой - с опорной шиной 3. Один вывод генератора 4 тока хранения подключен к опорной шине 3, а другой - к шине нулевого потенциала. Генератор 5 тока разряда и блок разряда, который состоит из двух п-р-п-транзисторов б и 7, база транзистора 6 подключена к шине опорного напряжения, а эмиттер транзистора 6 подключен к первому выводу генератора 5 тока разряда, второй вывод которого подключен к щине нулевого потенциала. В блок разряда введен р-п-р-транзистор 8, эмиттер которого подключен к опорной шине 3, коллектор и база - соответственно к базе и коллектору второго п-р-п-транзистора 7, эмиттер и коллектор первого п-р-п-транзистора 6 подключены соответственно к базе р-п-р-транзистора 8 и к шине питающего напряжения, дополнительный эмиттер второго р-п-р-транзистора 7 подключен к опорной шине 3.

Запоминающее устройство работает следующим образом.

При повыщении напряжения на словарной шине 2 выше уровня «невыбранной строки через открытое плечо элемента 1 памяти протекает ток заряда емкости опорной шины 3, что приводит к росту напряжения на ней и быстрому включению р-п-ртранзистора 8 и п-р-п-транзистора 7 за счет наличия цепи положительной обратной связи (база транзистора 8 соединена с коллектором транзистора 7, а коллектор транзистора 7 соединен с базой транзистора 8).

Включение транзисторов 8 и 7, приводит к появлению дополнительного разрядного тока, словарной 2 и опорной 3 шин, определяемого генератором 5 тока разряда. При достижении словарной шиной 2 напряжения,

равного напряжению «невыбранной строки, транзисторы 7 и 8 включаются за счет прекращения тока через переход эмиттер-база р-п-р-транзистора 8, вызываемого превышением напряжения, формируемого на базе

0 р-п-р-транзистора 8 эмиттерным повторителем 6, на базу которого подано постоянное напряжение, равное напряжению на опорной щине «невыбранной строки. Это вызывает прекращение коллекторного тока р-п-ртранзистора 8, и, как следствие, прекращение базового тока и запирание п-р-п-транзистора 7. При этом большая скорость запирания обеспечивается протеканием коллекторного тока транзистора 7, задаваемого эмиттерным повторителем 6. Запирание транзисторов 8 и 7 обеспечивает от0сутствие постоянного расхода мощности схе-, мы разряда, т. е. снижается потребляемая мощность запоминающего устройства.

Для повышения быстродействия по включению разрядной цепи один (или более)

5 дополнительный эмиттер п-р-п-транзистора 7 подключен к эмиттеру п-п-р-транзистора 8, что обеспечивает емкостной ток в базу п-р-п-транзистора 7, при повышении напряжения на опорной шине 3 через емкость обратносмещенного перехода эмиттер-база.

0 Генератор 4 тока хранения обеспечивает протекание постоянного тока через элементы 1 памяти.

Таким образом, предлагаемая схема обеспечивает существование повышенного тока разряда емкости ранее «выбранной строки только в то время, когда напряжение на словарной и опорной шинах выше, чем напряжение на словарной и опорной шинах «невыбранной строки, т. е. только во время переходного процесса, что приводит к снижению потребляемой мощности

0 и повышению быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1171849A1 |

| Запоминающее устройство | 1985 |

|

SU1310896A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Ячейка памяти | 1977 |

|

SU637866A1 |

| Формирователь сигналов считывания | 1984 |

|

SU1238152A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Запоминающий элемент | 1981 |

|

SU978195A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее элементы памяти, один вывод каждого из которых соединен со словарной, а другой - с опорной шинами, генератор тока хранения, один вывод которого подключен к опорной шине, а другой - к шине нулевого потенциала, генератор тока разряда и блок разряда, состоящий из двух п-р-п-транзисторов, база первого из которых подключена к щине опорного напряжения, а эмиттер второго - к первому выводу генератора тока разряда, второй вывод которого подключен к шине нулевого потенциала, отличающееся тем, что, с целью снижения потребляемой мощности и повышения быстродействия устройства, в блок разряда введен р-п-р-транзистор, эмиттер которого подключен к опорной щине, коллектор и база - соответственно к базе и коллектору второго п-р-п-транзистора, эмиттер и коллектор первого п-р-п-транзистора подключены соответственно к базе р-п-р-транзистора и к щине питающего напряжения, дополнительный эмиттер второго п-р-п-транзистора подключен к опорной щине.

| JEEE Journal of Solid State Circuits, vol SC-13, N 5, October 1978, pp | |||

| Приспособление к сороковым весам для перевода их в сотенные | 1923 |

|

SU651A1 |

Авторы

Даты

1985-08-07—Публикация

1983-09-30—Подача