1

И (обретение относится к но.чунровод- никоным напоминающим устройстнам на ипо,1ярных тран:и1сторах.

lie.ibio и (обретении ииляется иовышение малежипсш и бьктродеГн твия элемента на мяти.

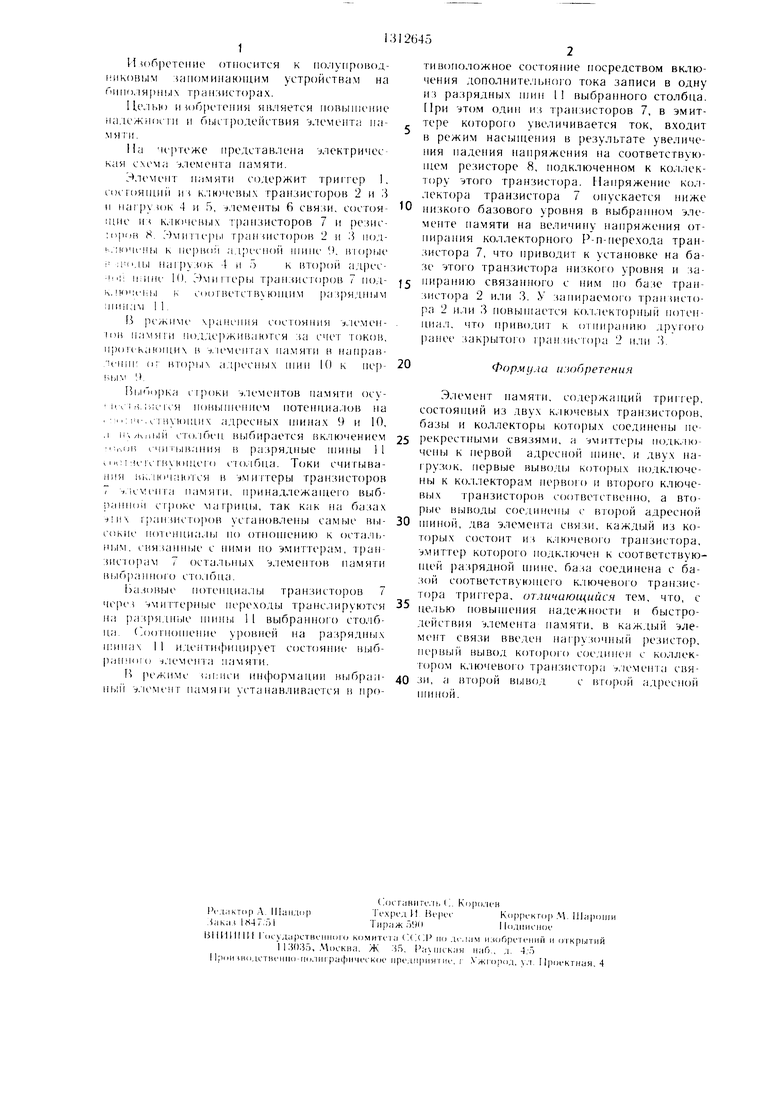

На Н ртеже представлеиа электричес кия схема :)леме11та памяти.

памяти содержит тригт ер 1, соеI(я11ии1 и( к.чючеиых транзиегор(Л) 2 и i и naipyioK 4 и 5, :,цементы 6 , еоетоя- |цие н клк1чевых i )анзиеторов 7 и )езис- 8. , -)uiT H pi,i Т1)ан (неторов 2 и 3 под- .. почты к iiepiioii адре1ЧИ)(| шинс ,). B lojii.ie - ii iMbi нагрузок 4 и 5 к BTOpoii ад|)ес- iiiUHe И). Эмигтеры т)а11зиеторо( 7 под- к, K)i:eh:i,i к соогветств} кмцим разряд1И 1м iiiHiiaM 1 1.

(i чраиеиия состояния :(;1емен- юв ||а 1Я1 и чодде1) за счет TIJKOB, чро1скак)|ци в -).1емеига 11амя 1 И в нанрав- U liiii о: втО|Ч,1х адресных IHHII 10 к HCf)- Ч) .t.

выборка сгроки элементов памяти осу- ич I i, г,;е гея новыничшем иотенниа.юв на i i: 1М , I Hyionuix адрееных тинах 9 и 10, .1 ,ii,iii сто/|бец в|,1бирается включением :,-,ijii гчитывания в разрядные Н1ипы 11 11 н,: I :н с I нукпцего ею.чбца. Токи ечигыва- ния нк,ночаются в : мигтеры транзисторов 7 i.icv iirra памяги, принад. 1ежан1е1 О выб- рапноч с1(1оке магриць, так как на базах 1ранзисторов установлены самые Biii- сокие потечщиалы но ()тионачи1К) к оеталь- ным, с(язан1и |е е ними по : миттерам, 1)ан- зиеюрам 7 остальных :).1емептов намят и Bbi6paHH(jro сто,и )па.

Ьазовые 1отен11,иа;1ы транзиеторов 7 черс -)1Итте|М) переходы транелируются па разрядные шниы 1 1 выбранно() етолб- па. ( оогпо1непие уровнен на разрядных типах II идепти()ипирует состояние выб- pannoici лемеш а памяти.

И реж;нме (амией информации выбран- ni)iii v.ieMcuT памя1И ус танавливаетея в про312645

тивоиоложиое соет(жиие посредством включения дополнительного тока записи в одну из разрядны.х 1 выбранного столбца. При этом одии из т)анзисторов 7, в эмиттере которого увеличивается ток, входит в режим насын1,ения в результате увеличения надения напряжения на соответствующем резисторе 8, подключенном к коллектору этого транзистора. Напряжение Ko. i- лектора транзистора 7 онускается ниже низкого базового уровня в выбранном элементе памяти на величи11у напряжения отпирания коллекторного Р-п-пере.ода транзистора 7, что приводит к установке на базе этого транзиетора низксхо уровня и запиранию связанного с ним по базе транзистора 2 или 3. У запираемо1 о трап(ието- ра 2 или 3 повьпиается ко.члекторны потен- пиал. что приводи к отпирапию другою lanee закрытого i |)анзисто|)а 2 и. ш 3.

Формула и лобретения

3;1емент памяти, содержащий триггер, состоянии из двух ключевг1гх транзисторов, базы и коллекторы кото|)ы.х соедиггены перекрестными связями, а эмитте|м 1 подк,1К)- чеиы к первой адресно тине, и двух нагрузок, первые выводы кото)ьгх подключены к ко. ктекторам первого и второго ключе- вьгх транзисторов соответетвеппо, а вторые соеднпен с второй адресной тиной, два элемента связи, каждый из которых состоит из ключевого транзистора, эмиттер которого подключеп к соответетвую- Н1ей разрядной пине, база соединена е базой е()ответствуюп1е1 о к.чючевого транзистора триггера, отличающийся тем, что, с не.тью повынк ния надежности и быстродействия э,лемента памяти, в каждый элемент связи введен naiрузочиьи резистор, первый вывод KOTopoiо соедипеп с коллек- юром к.тючевого траизистора элеменга связи, а второй выводс вгорой адресной

НП1ПОЙ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Согласующее устройство для ультразвукового пьезопреобразователя | 1986 |

|

SU1392499A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| Универсальное устройство питания с защитой от переполюсования аккумуляторной батареи | 1986 |

|

SU1403050A1 |

Изобретение относится к полупроводниковым запоминающим устройствам на биполярных транзисторах. Цель изобретения - повып1ение надежности и быстродействия элемента па.мяти. Поставленная цель достигается тем, что в эле.менты связи 6 элемента памяти введены нагрузочные резисторы 8 с соответствуюншми связями. Наличие резисторов 8 приводит к тому, что транзисторы 7 при записи работают в режиме насыщения. При этом увеличиваются их базовый ток, а следовательно, и ток, переключающий триггер 1. При считывании транзисторы 7 работают как эмиттерные повторители. повып1ая тем самым достоверность информации, поступаю- П1ей в разрядные П1ипы 11. I ил. (Л оо го Ci 4 01

| Валиев К | |||

| А., Орликовский А | |||

| А | |||

| Полупроводниковые интегральные схемы памяти на биполярны.х транзисторных структурах | |||

| - М,: Советское радио, 1979, с | |||

| Приспособление, заменяющее сигнальную веревку | 1921 |

|

SU168A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Патент ФРГ № 3320732, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-05-23—Публикация

1986-01-02—Подача