ллрепп.к нхолы 17. 1М. И11ф()})маиионныс 1Г() 1Ы I , 21), выходы 1- 24, тактовый ).i 2Г и )Х(л 2() CHciia. ia /юги кч когс; ну- , 1Я, yt TpoiicTfii) огич нечииает чапис. и счи- т()1на11ис данч,1. и блоки I и 2 но алрссч. ({юрм ирусмых мулыип.текеорами 3 и 4. В чавиоимое и от колов, постунакицих с вхо- лов И) на управ.чяюшш вхолы i льтшктек- i-opoii, могут о -уществляться слслующис р(. ал|)(.ч ацин: 11е)елача адре- i.iR с входов 17 и 18 на входы блоков 1 и 2; перестановка sTiix адресов и передача нх iia вхолы б.токов 1 и 2; вылача фнкси1

Изобретение относится к В1 1числите,1ь- iioii техр|ике и может быгь нсно.тьзоваио нри ностроении оперативной намят, в часг- носги для неигральных н снеииали (ирован- иых и|)онессоров.

Це, 1ьк) изобретения яв.тяется расширение o6. iai Tii нримснения сг 1ойсгва la счс1 более полного нспол1)3ования обтАма намя- гн,

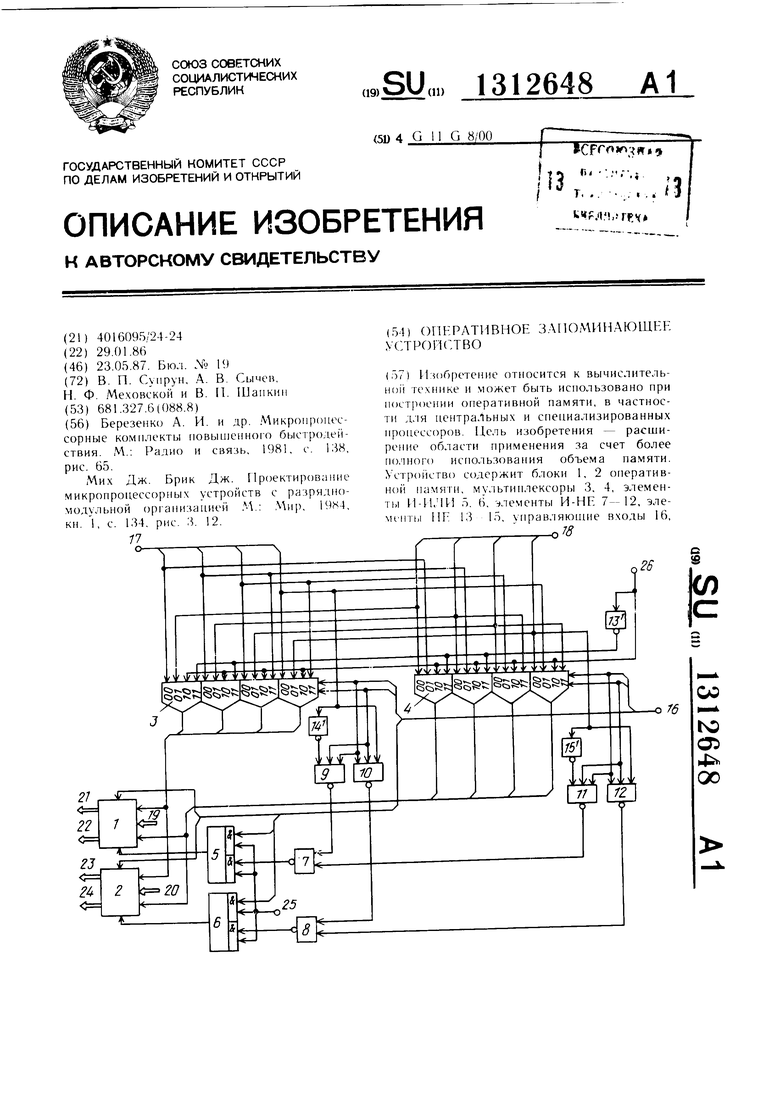

Па чертежа ирелсгав.тена структурная ема ()ие|))го заи()минак)Н1его уст POIK TTUI.

Уст)ойсгво содержит б.токи 1 и 2 оие- )ативн()й намягн, 11е|)вый 3 и второй 4 му.чь- гии.тексоры. элеме1ггы H4IJIH 5 и 6, H-HF: 7 12. элементы НЕ- 13 15. унравляюнще вхолы 16. адреси1 1е входы 17 и 18. инфор- маинонные ихолы 19 и 20. информационные выхол1|| 21 24. такювый вход 25 и вход 2() сн1на,та .тпгичсского нуля.

Блоки I и 2 онеративной намяти |ред- назначены для нриема, хранения и выдачи ин4 ормацни. Выдача ин1)ормации на первую | рунпу HH(j)o))HH,ix выходсл б.то- ка 1 (2) oHepaniBHoii памяти осун1еств.тя- ется под унравле1П1ем кола ал| сса. поступающего на алресных входов блока 1 (2) оне|1ативной намяти, а Eibi- дача И1и|)ормании на вторую руину инфор- MannoHinjix ыхолов б.тока I (2| оператив- Hoi i памяти осуп1ествляется нсхт. унрав.те- нием кода адреса, ностунаюпимо на вторую группу алресных ИХОЛОЕ блока 1 (2) оне- ративной памяти. В1,1лача ин(|1ормапии осу- Н1еств.1яется по сигна.ту, подаваемому на вхол обращения б.тока 1 (2) оне)ативной памяти.

Занис) ннформации. подаваемой на группу информационных входов блока 1 (2) онеративной намяти, осуществляется при подаче сигнала на вход обращения блока 1 (2) онеративной памяти, если на его вход разреп.1ения записи ностунил сигнал с со)ованн()1 о адреса н и Пон ячейки, позво- ,тяк)Н1ая увеличить число адресуемых ячеек с 1к)мо1цью у11|)авляю1цих входов; преобразование кодов адресов на входах 17 и 18 в физические адреса блоков 1 и 2 для унлотнемия информации при записи нено,тных слов. Э.чементы 5 и 6 формируют CHI на.т обранк ния к блокам 1 и 2, сумми- )уя си1 иалы обращения с входа 16 и сиг- на,т|,1 обранк ния, полученные путем логи- 4ecK(jrii Г1реоб)азования младшего адрес- ногч) сигнала на входах 17 и 18 с помощью элементов НЕ 9--12 и 14, 15. 1 ил. 2 табл.

ответствую mei o управляющего входа 16 ycT|)oiici ва, причем адрес ячейки блока 1 |2| п)п этом задается кодом на первой ijvviifie а.треспых входов блока 1 (2) оне- p.iTMBHoii намяти.

ЛАультинлексоры 3 и 4 выполняют сле.4 IOHU1C ())уНКЦИИ.

()суп1ествляют передачу кодов адреса

o с входов 17 и 18 устройства на первую и грунны адресных входов блоков 1 и 2 оперативной намяти, кол на управляющих входах мультиилексоров «00.

Осуществляют перестановку этих адресов, т.е. передачу кодов адресов с входов 17(18) устройства па вторую (первую) группу адресных входов блоков 1 и 2 операiив ной памяти (код на управляющих вхолах мультиплексоров «01), выдачу фиксиро- ваиного адреса нулевой ячейки блоков I

0 и 2 оперативпой памяти путем передачи пулевого потенциала с входа 26 (код на унравляющих входах мультинлсксоров «10) Использование ячейки блоков 1 и 2 оне- )ативной намяти с фиксированным адресом иозво,тяет увеличить число адресуемых ячеек в сложных командах, используя помимо ячеек, адресуемых кодами па входах 17 и 18 устройства, дополнительные ячейки блоков 1 и 2 участвующего в реа- .тизации сложных алгоритмов команд нро0 цессора. Преобразование кодов адресов па входах 17 и 18 устройства в физические адреса ячеек блоков 1 и 2 оперативной на- .мяти происходит для уплотнения расположения в них различных кодов но закону, который ноясняется табл. 1 (код на управ5 ляющих входах мультиплексоров «11), Нри этом на первых и вторых выходах мультиплексоров 3 и 4 присутствуют константы «II, а па третьих и четвертых выходах соответственно соде1)жимое второго и третьего разрядов входов 17 и 18 устройства.

5

1312648.

34

Состояние младшего четвертого разрядадолжен работать при обращении. Табл. 2

адреса на входах 17 и 18 определяет, ка-иллюстрирует пример заполнения объема

кой из блоков 1 и 2 оперативной памятипамяти предлагаемого устройства.

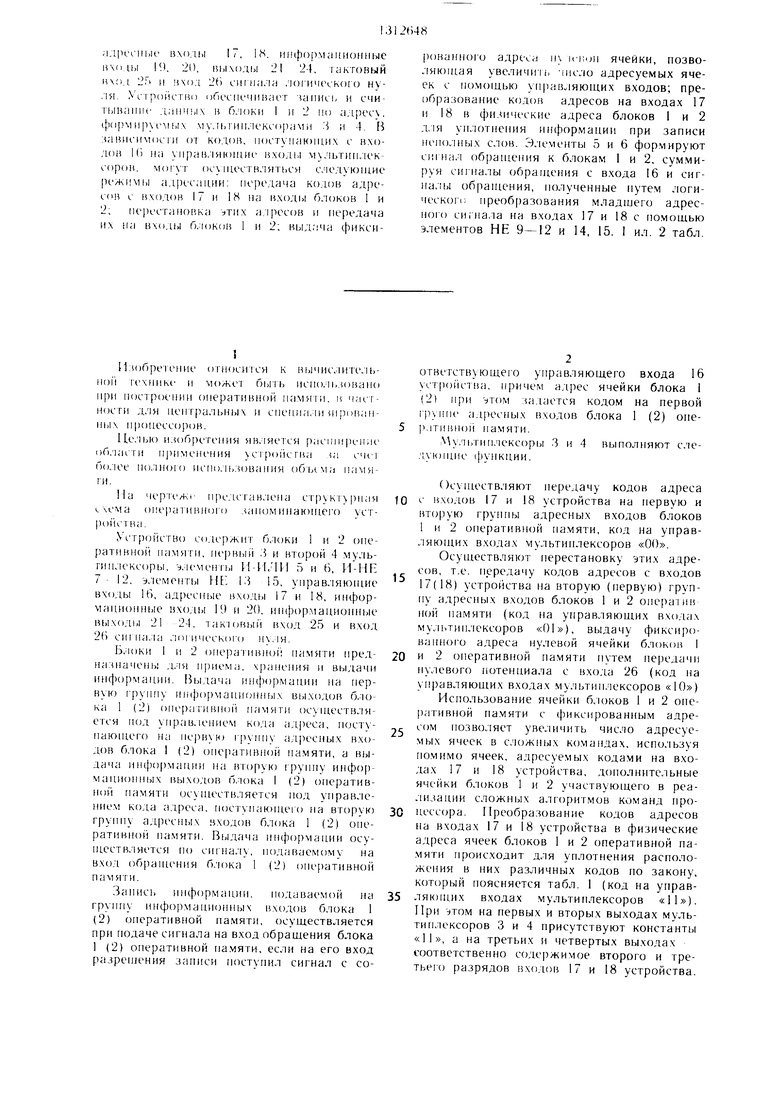

Таблица 1

1р 2р Зр 4р 1р 2р Зр 4р 1р 2р Зр 4р 1р 2р Зр 4р

Элементы И-И ЛИ 5 и 6 предназначены для формирования сигналов обра1це}|ия к блокам 1 и 2 оперативной памяти соответственно в моменты подачи тактового сигнала на вход 25 устройства. Формирование сигналов обращения на выходах элементов И-ИЛИ 5 и 6 при наличии на управляюп1,их входах мультиплексоров 3 и 4 «00, «01 или «10 осуществляется при подаче cni-- налов обращения на входы элементов И- ИЛИ 5 и (или) 6 с соответствуюнхих управляющих входов 16 устройства. При подаче преобразованных адресов при коде «II на управляющих входах мультиплексоров 3 и 4 сигналы, разрещаюн;ие передачу сигналов с входа 25 устройства на входы обращения блоков 1 и 2 оперативной памяти, формируются элементами И-HF. 9- 12. объединяются элементами И-НЕ 7 и 8 и подаются на входы элементов И-ИЛИ 5 и 6.

Элементы И-НЕ 7 и 8 предназначены для объединения и согласования по полярности сигналоЕ, вырабатываемых элементами И-НЕ 9- 12 при настройке мультиплексоров 3 и 4 на передачу информации при управляющем коде «11 и разреп1аю1пих выработку сигналов обрап1.ения к блокам 1 и 2 оперативной памяти в моменты подачи тактовых сигналов на вход 25 устройства.

Элементы И-НЕ 9 и И (Ю и 12) предназначены для формирования сигнала раз- рещения обращения к блоку 1(12) оперативной памяти в режиме преобразования

0

5

0

5

адресов устройства (кода «11 на управляющих входах мультиплексоров 3 и 4). При этом элемент И-НЕ 9(11) вырабатывает указапный сигнал, если четвертый младщий разряд кода на входе 17(18) устройства имеет нулевое значение (высокий сигнал на выходе элемента НЕ 14(15), а элемент И-НЕ 10(12) вырабатывает сигнал, если четвертый младший разряд кода на входе 17(18) устройства имеет единичное значение (табл. Г).

Элемент НЕ 14(15) предназначен для подачи единичного сигнала на соответствующий вход элемента И-НЕ 9(11) при нулевом значении четвертого младшего разряда кода на входах 17(18) устройства.

Элемент НЕ 13 предназначен для формирования единичного потенциала на четвертых информационных входах мультиплексоров 3 и 4.

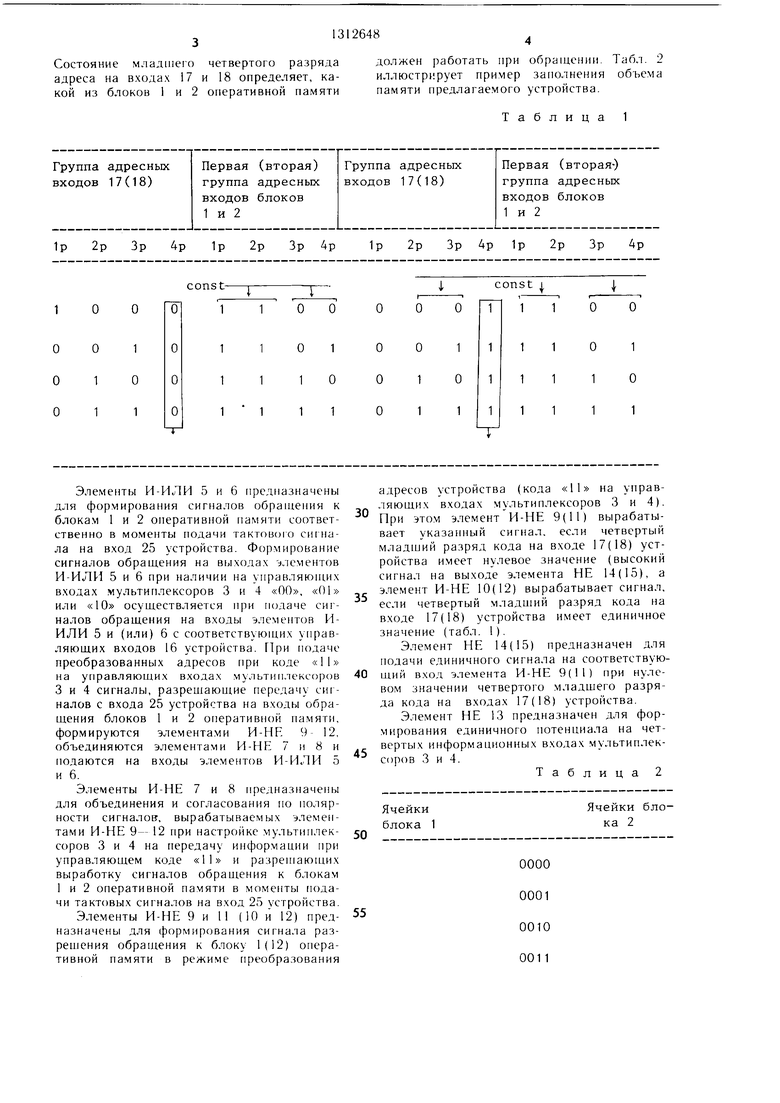

Таблица 2

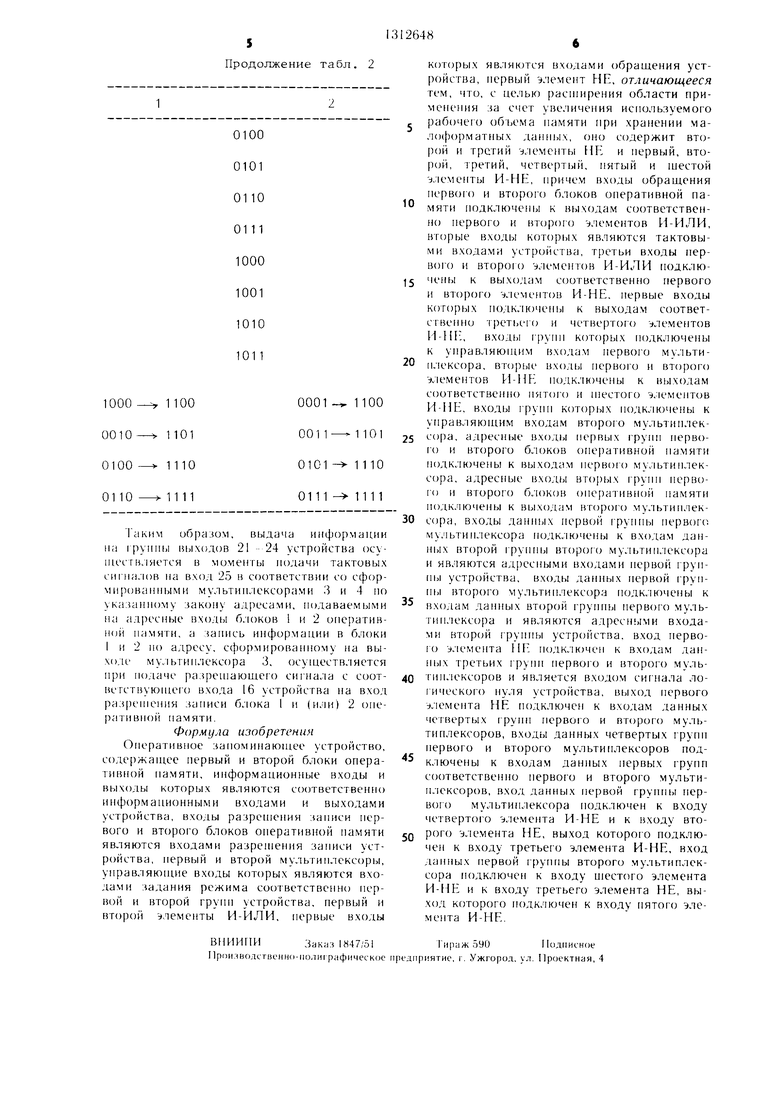

Продолжение табл. 2

0100 0101 0110 01 11 1000 1001 1010 101 1

Таким образом, выдача информации ia груши, выходов 21 24 устройства осу- пичтндиотся в моменты подачи тактовых си1 на. 1()в на вход 25 н соответствии со сфор- )ванными мультинлексорами 3 и 4 но указанному закону адресами, подаваемыми на адресные вх() б. юков 1 и 2 оперативной памяти, а запись информации в блоки I и 2 но адресу, сфс рмированному на выходе мультиплексора 3, осуществляется нрн нодаче разреншющег о сигнала с соот- вегствуклнег о входа 16 устройства на вход раз|)е1нения записи б.юка I и (и.пи) 2 оне- |)ативной памяти.

Формула изобретения

Оперативное запоминающее устройство, содержан1ее первый и второй блоки опера- гивной памяти, информационные входы и выходы которых являются соответственно информационными входами и выходами устройства, входы разрешения заниси первого и второго блоков оперативной памяти являются входами разрешення заниси устройства, иервый и второй мультинлексоры, управляющие входы которых являются входами задания режима соответственно первой и второй грунн устройства, нервый и второй элементы И-ИЛИ, первые входы

ВНИИПИЗака: 1й47;51Тираж 590Подписное

Прои,1волствеин()-Г1олиг рафнческое предприятие, г. Ужгород, ул. Проектная, 4

0

5

0

5

0

5

0

которых являются входами обращения устройства, иервый : лемеит НЕ, отличающееся тем, что, с целью расширения области при- менення за счет увеличения используемого рабочего объема памяти при хранении ма- ло((к)рматных данных, оно содержит BTCJ- рой и третий элементы НЕ и нервый, второй, третий, четвертый, пятый и шестой улеме1{ты И-НЕ, причем входы обращения первого и второго блоков оперативной памяти подключены к выходам соответственно первого и второго элементов Н-ИЛИ, вторые входы которых являются тактовыми входами ycTpoi iCTua, третьи входы первого и второю элементов И-ИЛИ подключены к выходам с(ютветственно первого и второго ч,;1ементов И-НЕ, первые входы которых подключены к выходам соответ- сгвепно т|)етьего и четвертог о элементов ., входы групп которых подключены к у11равляюн1им входам первого му,:1ьти- ii. icKCopa, вторые вход1)1 перво1 о и второго элементов И-НР нодк.чючены к ()дам соответственно нитого и niecToro э.к ментов И-НЬ входы групп которых подключены к управляющим входам второго мультиплексора, адресные входы первых грунп нерво- гч) и второго блоков оперативной памяти нодключепы к выходам первого мультиплексора, адресные входы вторых групп первого и второго б.чоков онератнвной памятн подключены к выходам второг о мультинлек- сора, входы данных первой группы первого му, 1ьтиплексора нсх жлючены к входам данных второй грунгП) BToporcj му:1ьтип,лекеора и яв.пяются ад)есными входами нервой грун- Ш)| устройства, входы данных нервой I pyn- 1П,1 второго мультиплексора подключены к входам данных второй грунны первого мультиплексора и являются адресными входами второй грунпы устройства, вход нерво- ю элемента НЕ: подключен к входам данных третьих г рунн первого и второго мультиплексоров и является входом сигнала ло- 1ического нуля устройства, в)1ход первого элемента НЕ подключен к входам данных чегвертых грунп первого и второго мультиплексоров, входы данных четвертых I pynn первого и второго мультиплексоров подключены к входам данных первых групп соответственно первого и второго мульти- H. ieKcopoB, вход данных нервой грунны первого мультигглексора ггодключен к входу четвертого элемента И-НЕ и к входу второго элемента НЕ, выход которого нодклю- чегг к входу третьего элемента И-НЕ, вход даггных ггервой г-)упг1ы второго мультиплексора ггодключегг к входу нгестого элемента и к входу третьего элемента НЕ, выход которого нодклгочен к входу ггятого элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для модификации команд | 1974 |

|

SU542995A1 |

| Устройство для обнаружения ошибок в блоках памяти программ | 1982 |

|

SU1278982A1 |

| Устройство для цифровой записи-воспроизведения речевых сообщений | 1985 |

|

SU1312641A1 |

| Устройство для передачи информации с обратной связью | 1986 |

|

SU1322356A1 |

| Мультиплексный канал с динамическим распределением памяти | 1973 |

|

SU526877A1 |

| Мультимикропрограммное устройство для контроля и управления | 1984 |

|

SU1249513A1 |

| Ритмокардиоскоп | 1985 |

|

SU1304801A1 |

| Устройство сопряжения процессора с памятью | 1986 |

|

SU1322296A1 |

| Устройство формирования теста для контроля тракта передачи данных | 1975 |

|

SU595734A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Березеико А | |||

| И | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| М.; Радио и свянь, 1981, с | |||

| Прибор для определения всасывающей силы почвы | 1921 |

|

SU138A1 |

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| ЛАих Дж | |||

| Брик Дж | |||

| Проектирование микронроцессорных устройств с разрядно- модульной организацией М.: ., 1984, кн | |||

| l, с | |||

| Халат для профессиональных целей | 1918 |

|

SU134A1 |

| рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Спускная труба при плотине | 0 |

|

SU77A1 |

Авторы

Даты

1987-05-23—Публикация

1986-01-29—Подача