Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах, для сопряжения центрального процессора, основной памяти и магистрали с асинхронным интерфейсом, например типа «обш.ая шина.

Целью изобретения является расширение области применения устройства.

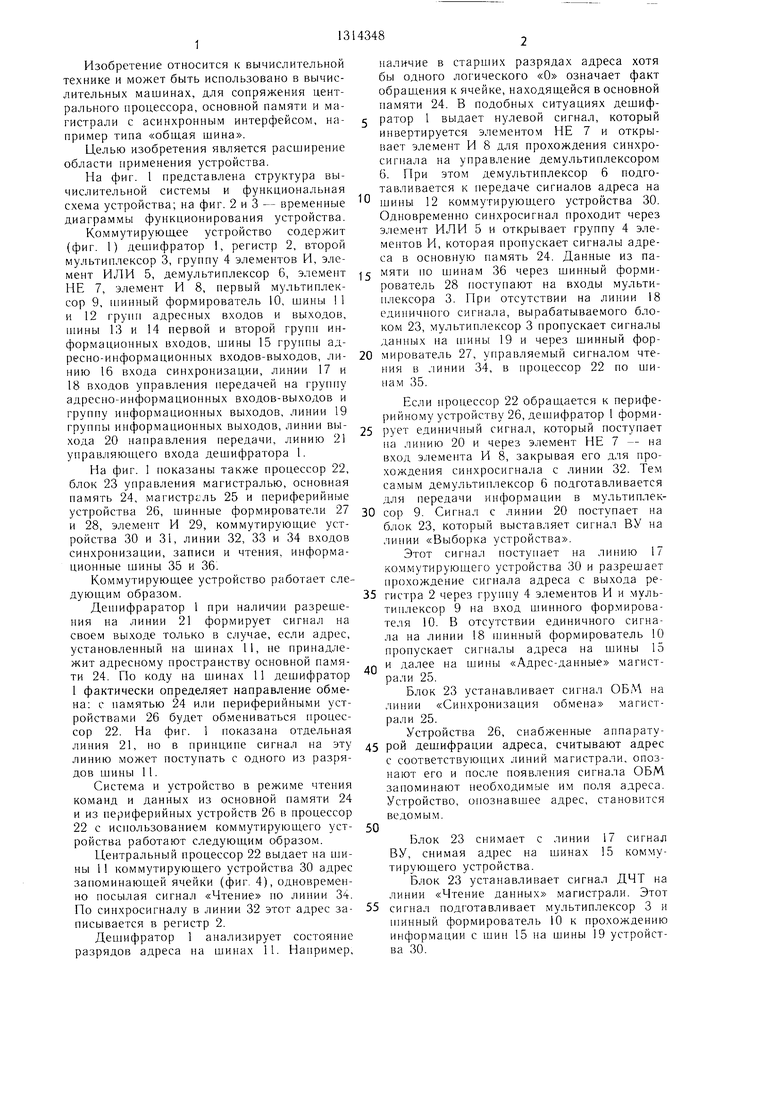

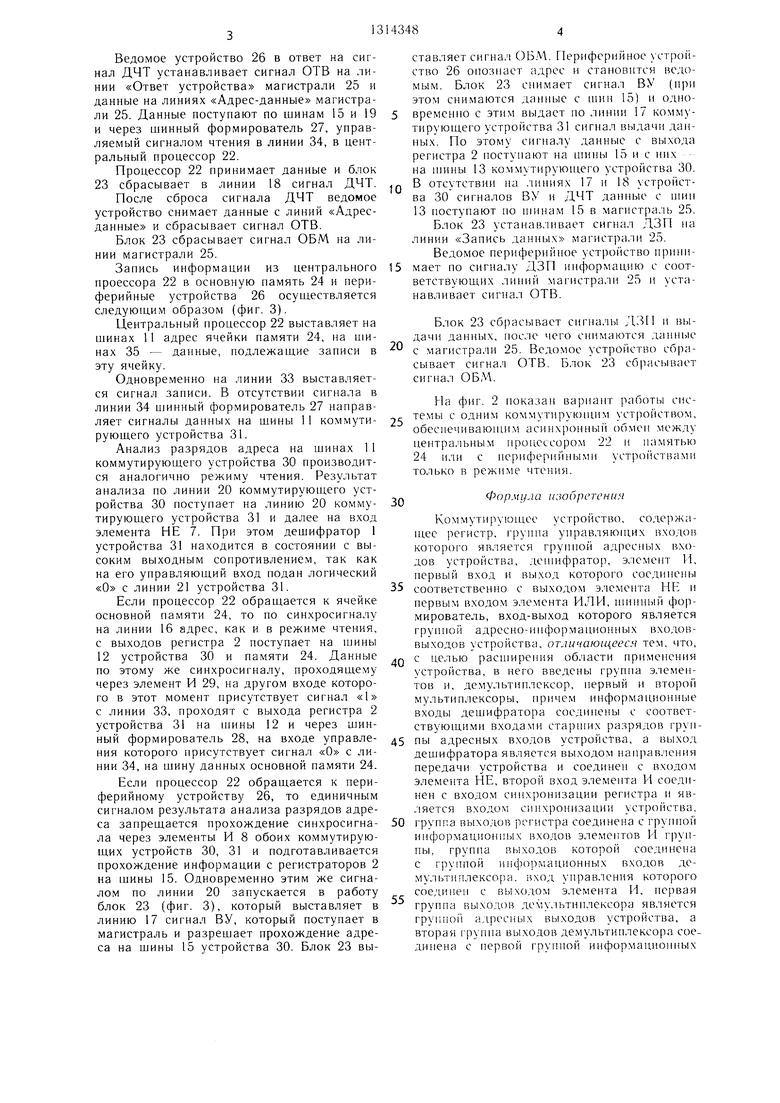

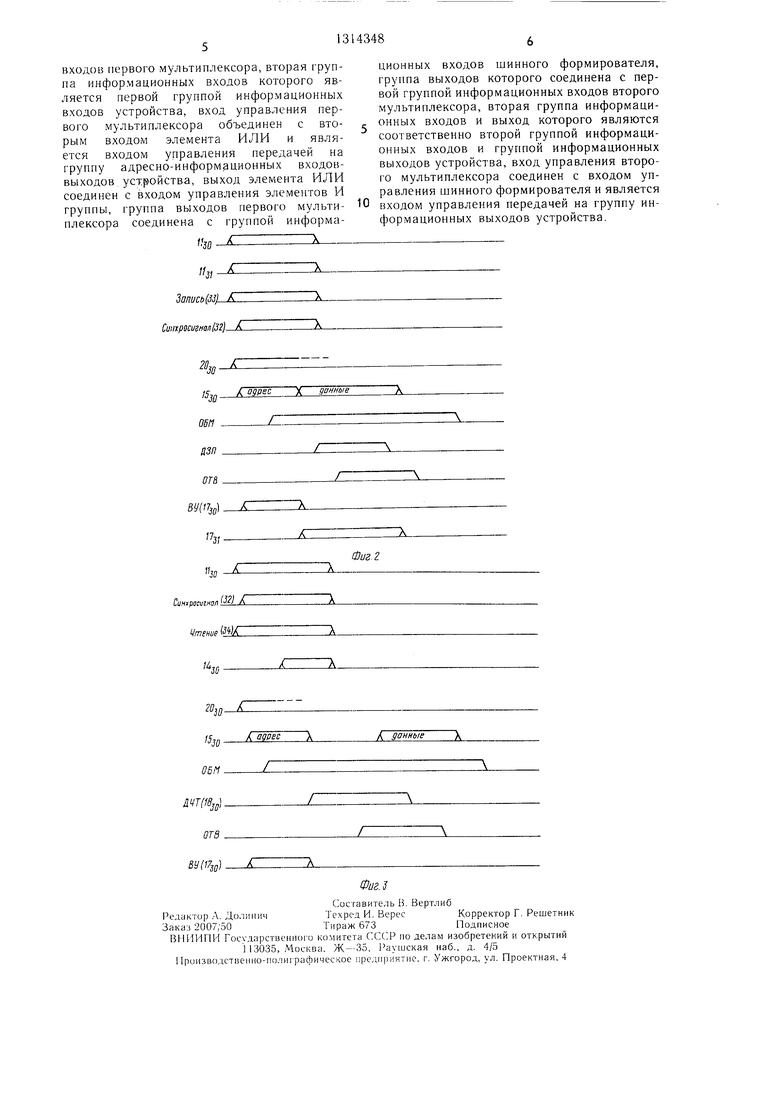

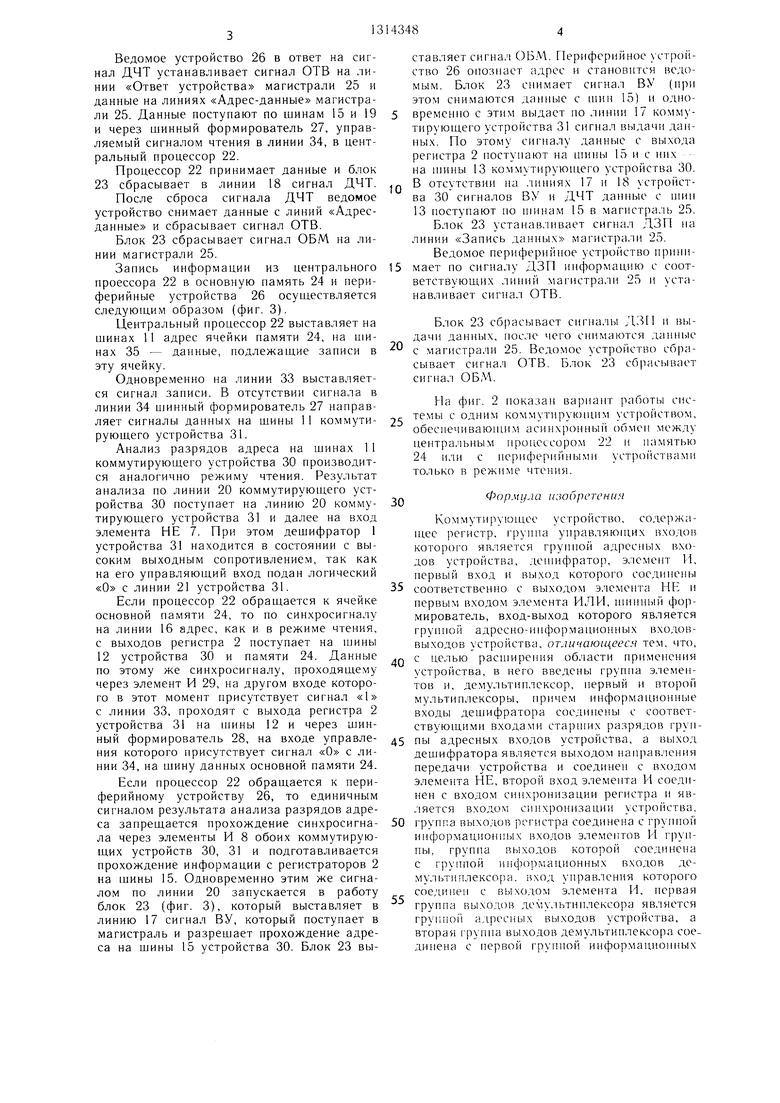

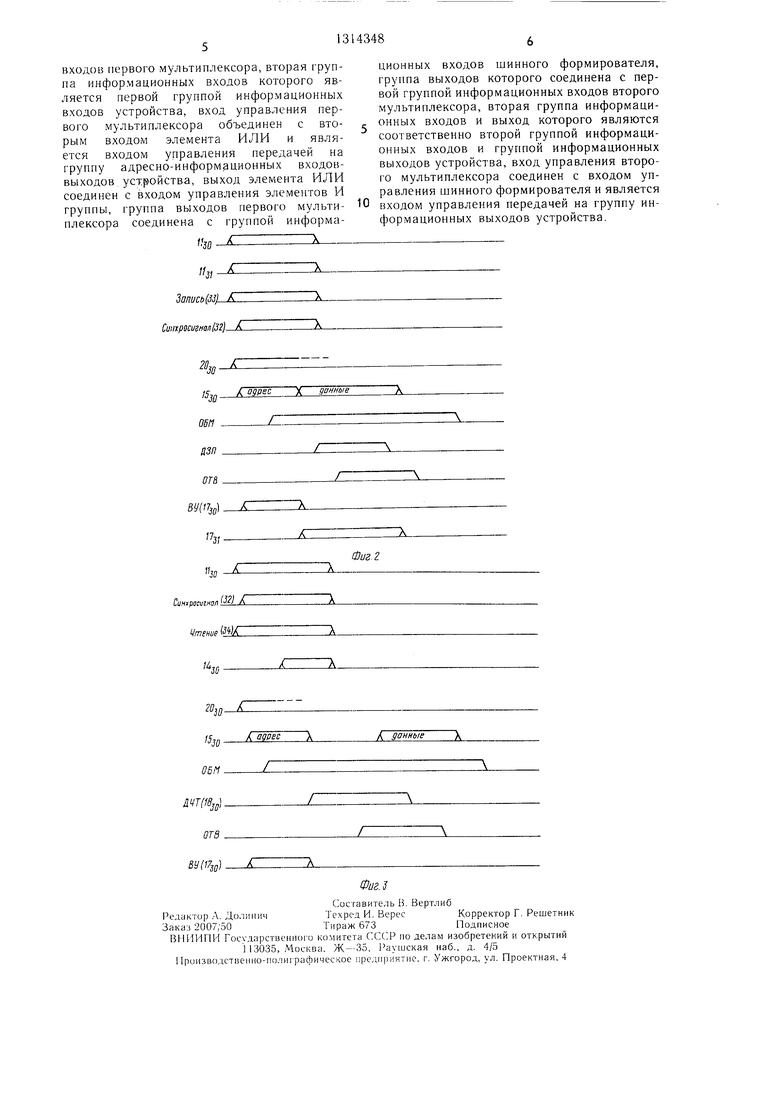

На фиг. 1 представлена структура вычислительной системы и функциональная схема устройства; на фиг. 2 и 3 - временные диаграммы функционирования устройства. Коммутируюш,ее устройство содержит (фиг. 1) деишфратор 1, регистр 2, второй мультиплексор 3, группу 4 элементов И, элемент ИЛИ 5, демультиплексор 6, элемент НЕ 7, элемент И 8, первый мультиплексор 9, П1ИННЫЙ формирователь 10, шины 1 1 и 12 грунп адресных входов и выходов, П1инь 13 и 14 первой и второй групп информационных входов, шины 15 группы адресно-информационных входов-выходов, линию 16 входа синхронизации, линии 17 и 18 входов управления передачей на группу адресно-информационных в ходов-вы ходов и группу информационных выходов, линии 19 группы информационных выходов, линии выхода 20 направления передачи, линию 21 управляющего входа дешифратора 1.

На фиг. 1 показаны также процессор 22, блок 23 управления магистралью, основная память 24, магистраль 25 и периферийные устройства 26, шинные формирователи 27 и 28, элемент И 29, коммутируюшие устройства 30 и 31, линии 32, 33 и 34 входов синхронизации, записи и чтения, информационные шины 35 и 36

Коммутирующее устройство работает сле- дуюшим образом.

Дешифраратор 1 при наличии разрешения на линии 21 формирует сигнал на своем выходе только в случае, если адрес, установленный на шинах 11, не принадлежит адресному пространству основной памяти 24. По коду на шинах 11 дешифратор 1 фактически определяет направление обмена: с памятью 24 или периферийными устройствами 26 будет обмениваться процессор 22. На фиг. 1 показана отдельная линия 21, но в принципе сигнал на эту линию может поступать с одного из разрядов шины 11.

Система и устройство в режиме чтения команд и данных из основной памяти 24 и из периферийных устройств 26 в процессор 22 с использованием коммутирующего устройства работают следующим образом.

Центральный процессор 22 выдает на шины 11 коммутирующего устройства 30 адрес запоминающей ячейки (фи1-. 4), одновременно посылая сигнал «Чтение по линии 34. Цо синхросигналу в линии 32 этот адрес записывается в регистр 2.

Дешифратор 1 анализирует состояние разрядов адреса на тинах 11. Например,

наличие в старших разрядах адреса хотя бы одного логического «О означает факт обращения к ячейке, находящейся в основной памяти 24. В подобных ситуациях дешифратор 1 выдает нулевой сигнал, который инвертируется элементом НЕ 7 и открывает элемент И 8 для прохождения синхросигнала на управление демультиплексором 6. Нри этом демультиплексор 6 подготавливается к передаче сигналов адреса на

шины 12 коммутирующего устройства 30. Одновременно синхросигнал проходит через элемент ИЛИ 5 и открывает группу 4 элементов И, которая пропускает сигналы адреса в основную память 24. Данные из па мяти по шинам 36 через шинный формирователь 28 поступают на входы мультиплексора 3. Цри отсутствии на линии 18 единичного сигнала, вырабатываемого блоком 23, мультиплексор 3 пропускает сигналы данных на шины 19 и через шинный фор0 мирователь 27, управляемый сигналом чтения в .1ИНИИ 34, в процессор 22 по шинам 35.

Если процессор 22 обращается к периферийному устройству 26, дешифратор 1 форми5 рует единичный сигнал, который поступает на линию 20 и через элемент НЕ 7 - на вход элемента И 8, закрывая его для прохождения синхросигнала с линии 32. Тем самым демультиплексор 6 подготавливается для передачи информации в мультиплек0 сор 9. Сигнал с линии 20 поступает на блок 23, который выставляет сигнал ВУ на линии «Выборка устройства.

Этот сигнал поступает на линию 17 коммутируюшего устройства 30 и разрешает прохождение сигнала адреса с выхода ре5 гистра 2 через rpyiuiy 4 элементов И и мультиплексор 9 на вход шинного формирователя 10. В отсутствии единичного сигнала на линии 18 шинный формирователь 10 пропускает сигналы адреса на шины 15

Р и далее на шины «Адрес-данные магистрали 25.

Блок 23 устанавливает сигнал ОБМ на .линии «Синхронизация обмена магистрали 25.

Устройства 26, снабженные аппарату5 рой дешифрации адреса, считывают адрес с соответствующих линий магистрали, опознают его и после появления сигнала ОБМ запоминают необходимые им поля адреса. Устройство, опознавшее адрес, становится ведомым.

0

Блок 23 снимает с линии 17 сигна,л ВУ, снимая адрес на шинах 15 коммутируюшего устройства.

1элок 23 устанавливает сигнал ДЧТ на линии «Чтение данных магистрали. Этот

5 сигнал подготавливает мультиплексор 3 и ншнный формирователь 10 к прохождению информации с шин 15 на шины 19 устройства 30.

Ведомое устройство 26 в ответ на сигнал ДЧТ устанавливает сигнал ОТВ на линии «Ответ устройства магистрали 25 и данные на линиях «Адрес-данные магистрали 25. Данные поступают по шинам 15 и 19 и через шинный формирователь 27, управляемый сигналом чтения в линии 34, в центральный процессор 22.

Процессор 22 принимает данные и блок 23 сбрасывает в линии 18 сигнал ДЧТ.

После сброса сигнала ДЧТ ведомое устройство снимает данные с линий «Адрес- данные и сбрасывает сигнал ОТВ.

Блок 23 сбрасывает сигнал ОБМ на линии магистрали 25.

Запись информации из центрального проессора 22 в основную память 24 и периферийные устройства 26 осуществляется следующим образом (фиг. 3).

Центральный процессор 22 выставляет на щинах 11 адрес ячейки памяти 24, на тинах 35 - данные, подлежащие записи в эту ячейку.

Одновременно на линии 33 выставляется сигнал записи. В отсутствии сигнала в линии 34 ц инный формирователь 27 направляет сигналы данных на щины 11 коммутирующего устройства 31.

Анализ разрядов адреса на щинах 1 1 коммутирующего устройства 30 производится аналогично режиму чтения. Результат анализа по линии 20 коммутируюпхего устройства 30 поступает на линию 20 коммутирующего устройства 31 и далее на элемента ПЕ 7. При этом дешифратор 1 устройства 31 находится в состоянии с высоким выходным сопротивлением, так как на его управляющий вход подан логический «О с линии 21 устройства 31.

Если процессор 22 обращается к ячейке основной памяти 24, то по синхросигналу на линии 16 адрес, как и в режиме чтения, с выходов регистра 2 поступает на пJины 12 устройства 30 и памяти 24. Данные по этому же синхросигналу, проходящему через элемент И 29, на другом входе которого в этот момент присутствует сигнал «1 с линии 33, проходят с выхода регистра 2 устройства 31 на пжны 12 и через щин- ный формирователь 28, на входе управления которого присутствует сигнал «О с линии 34, на шину данных основной памяти 24.

Если процессор 22 обращается к периферийному устройству 26, то единичным сигналом результата анализа разрядов адреса запрещается прохождение синхросигнала через элементы И 8 обоих коммутирующих устройств 30, 31 и подготавливается прохождение информации с регистраторов 2 на шины 15. Одновременно этим же сигналом по линии 20 запускается в работу блок 23 (фиг. 3), который выставляет в линию 17 сигнал ВУ, который поступает в магистраль и разрешает прохождение адреса на щины 15 устройства 30. Блок 23 выставляет сигнал ОБЛ . Периферийное устройство 26 опознает адрес и становится ведомым. Блок 23 снимает сигнал ВУ (при этом снимаются данные с тин 15) и одновременно с этим выдает по линии 17 коммутирующего устройства 31 сигнал выдачи данных. По этому сигналу данные с выхода регистра 2 поступают на щины 15 и с них на П1ИНЫ 13 коммутирующего устройства 30.

В отсутствии на линиях 17 и 18 устройства 30 сигналов ВУ и ДЧТ дан1п 1е с тин 13 поступают по Н1пнам 15 в магистраль 25. Блок 23 устанавливает сигнал ДЗП на линии «Запись данных магистра.пи 25.

Ведомое периферийное устро(1ство принимает по сигналу Л,ЗГ информацию с соответствующих линий магистрали 25 и устанавливает сигнал ОТВ.

Блок 23 сбрасывает сигналы ДЗП и выдачи данных, после чего снимаются да1ПП)1е с магистрали 25. Ведомое устройство сбрасывает сигнал ОТВ. Блок 23 сбрасывает сигнал ОБМ.

На фиг. 2 показан вариант работы сис- темы с одним коммутирующим устройством, обеспечивающим асинхронный обмен между центральным процессором 22 и памятью 24 НЛП с периферийнымн устройствами только в режиме чтения.

30

Формула изобретения

5

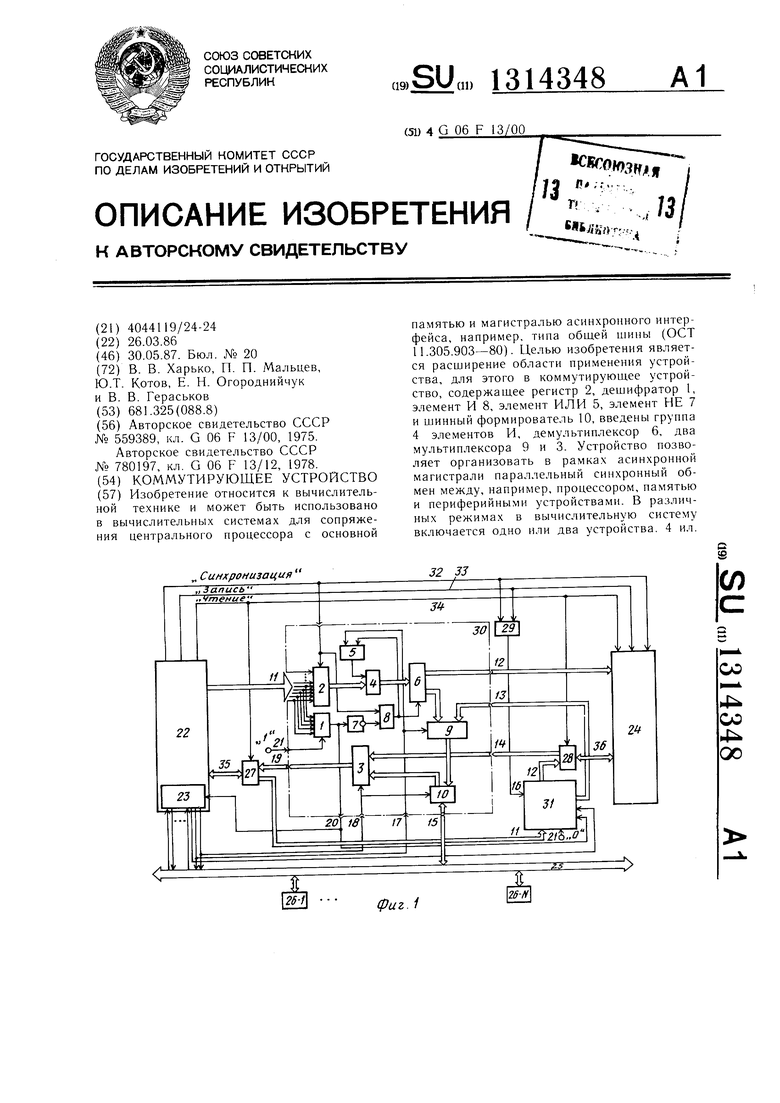

Коммутирующее устройство, содержащее регистр, группа управляюнщх входов которого является группой адрес 1ых входов устройства, дешифратор, элемент 11, первый вход и выход которого соединены

5 соответственно с выходом элемента НЕ и первым входом элемента ИЛИ, шинный формирователь, вход-выход которого является группой адресно-информационных входов- выходов устройства, отличающееся тем. что,

д с целью расширении области применения устройства, в него введены группа элементов и, демультиплексор, первый п второй мультиплексоры, причем информационные входы дешифратора соединены с соответствующими входами старн1их разрядов I pyn5 пы адресных входов устройства, а выход дешифратора является выходом направления передачи устройства и соединен с входом элемента НЕ, второй вход элемента И соединен с входом синхронизации регистра и является входом снихро1шзацин устройства,

0 группа выходов регистра соединена с группой ипформацион1 ых входов элементов И группы, группа выходов которой соединена с грушюй информационных входов де- мультиилексора. вход управления которого соединен с выходом элемента И, первая группа выходов демультиплексора является rpynnoi t адресных выходов устройства, а вторая 1 руппа выходов демультиплексора сое- дипена с первой группой информациопных

входов первого мультиплексора, вторая группа информационных входов которого является первой группой информационных входов устройства, вход управления первого мультиплексора объединен с вторым входом элемента ИЛИ и является входом управления передачей на группу адресно-информационных входов- выходов устройства, выход элемента ИЛИ соединен с входом управления элементов И группы, группа выходов первого мультиплексора соединена с группой информаr/jfl

nniirh(3ij X

Синхросигнал/3)

%15JQ °SPec ( gmmis

OS ft язп

ОТ&

ВУ(ПЗО}

jfl Синхросигнал X

L/тенае (

IS:

JOX адрес

ционных входов шинного формирователя, группа выходов которого соединена с первой группой информационных входов второго мультиплексора, вторая группа информационных входов и выход которого являются соответственно второй группой информационных входов и группой информационных выходов устройства, вход управления второго мультиплексора соединен с входом управления шинного формирователя и является входом управления передачей на группу информационных выходов устройства.

Ih

Фиг. 2

Л данные

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Устройство для обмена информацией | 1985 |

|

SU1278872A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для ввода-вывода информации | 1988 |

|

SU1587520A1 |

| Запоминающее устройство | 1987 |

|

SU1472910A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения центрального процессора с основной памятью и магистралью асинхронного интерфейса, например, типа общей шины (ОСТ 11.305.903-80). Целью изобретения является расширение области применения устройства, для этого в коммутирующее устройство, содержащее регистр 2, дешифратор 1, элемент И 8, элемент ИЛИ 5, элемент НЕ 7 и щинный формирователь 10, введены группа 4 элементов И, демультиплексор 6, два мультиплексора 9 и 3. Устройство позволяет организовать в рамках асинхронной магистрали параллельный синхронный обмен между, например, процессором, памятью и периферийными устройствами. В различных режимах в вычислительную систему включается одно или два устройства. 4 ил. „ Синхронизация 32 33 (Л со 00 оо фиг. i

| Коммутирующее устройство | 1975 |

|

SU559389A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутатор | 1978 |

|

SU780197A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-30—Публикация

1986-03-26—Подача