Содержимое счетчиков 1-2 сравниваются схемой 4 срав нения. При каждом превышении содержимого счетчика 1 над содержимым счетчика 2 на выходе схемы 4 сравнения возникает сигнал, по которому к содержимому первого счетчика 3 добавляется единица, а счетчик 1 устанавливается в состояние единица. Таким образом, в счетчике 3 накапливается результат деления . После окончания вьщачи кода де

1

Изобретение относится к вычислительной технике и может быть использовано для деления чисел, заданных число-импульсным кодом.

Цель изобретения - повышение точ- ности.

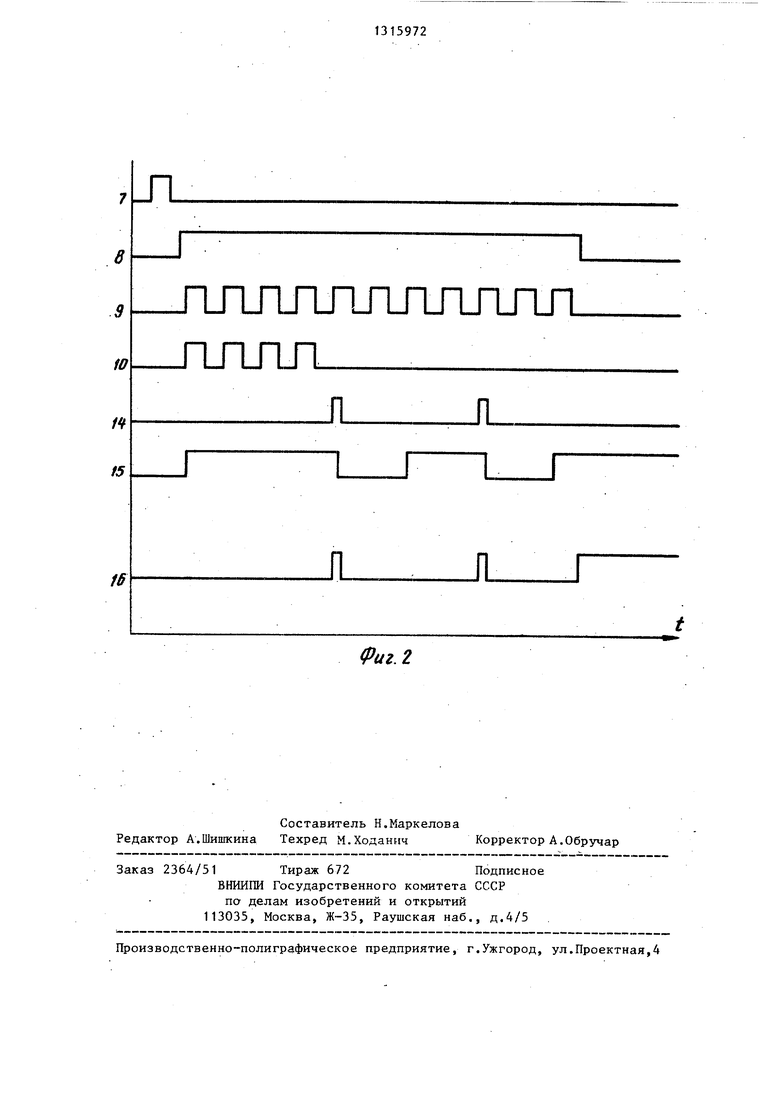

На фиг. 1 представлена функхщо- нальная схема устройства для деления; на фиг. 2 - временные диаграммы пояснякяцие работу устройства.

Предлагаемое устройство содержит три счетчика 1-3, схему 4 сравнения, дополнительную схему 5 сравнения, коммутатор 6, вход 7 сброса, вход 8 сопровождения делимого, входы 9 и 10 делимого и делителя, выход 11 результата, вход 12 логической единицы, вход 13 логического нуля, выход 14 схемы сравнения, выход 15 дополнительной схемы сравнения, выход 16 коммутатора.

Устройство работает следующим образом.

Перед началом работы иа вход сбро са устройства (фиг.1) подается сигнал Сброс,- который поступает на входы установки в нуль счетчиков 1-3. Тем самым устройство приводится в исходное состояние.

При вычислении частного на входы делимого и делителя соответственно поступают синхронно m импульсов кода делимого и п импульсов кода делителя (фиг.2). Одновременно на вход 8 уст- ройства поступает сигнал логической единицы. Импульсы кода делимого поступают на счетный вход счетчика 1, а импульсы кода делителя - на счет

ный вход счетчика 2. Счетчики 1 и 2

лимого в счетчике 1 находится значение остатка, которое сравнивается с половиной значения делителя. Сравнение производится схемой 5 сравнения. При превышении остатком половины делителя к результату, находящемуся в счетчике 3, прибавляется единица. Тем самым производится округление результата до целого, в результате чего абсолютная погрешность частного не превышает 0,5. 2 ил.

to

15

5

Jiy

-5

0

срабатьшают по фронту импульсов, по- ступаняцих на их счетные входы.

Схема 4 сравнивает содержимое счетчиков 1 и 2. При поступлении первых п импульсов кода делимого и кода делителя состояния счетчиков 1 и 2 одинаковы. На выходе схемы 4 сравнения присутствует сигнал логического нуля. После поступления п импульсов кода делителя и кода делимого счетчики 1 и 2 находятся в состоянии п. В дальнейшем на счетный вход счетчика 2 импульсы не подаются и он все время остается в состоянии п. При поступлении (п+1)-го импульса кода делимого содержимое счетчика 1 становится больше содержимого счетчика 2. На выходе схемы 4 сравнения возникает сигнал логической единицы, поступающий на вход коммутатора 6 и на вход разрешения записи счетчика 1, которьй тем самым устанавливается в состояние Единица. Это происходит потому, что на вход первого разряда счетчика 1 подан потенциал логической единицы, а на входы остальных разрядов - потенциал логического нуля (фиг. 1).

Сигнал с выхода Больше схемы 4 сравнения проходит через коммутатор и поступает на счетньй вход счетчика 3, увеличивая содержимое последнего на единицу.

После окончания переходных процессов в счетчике 1, при установке его по установочному входу в состояние Единица, на выходе схемы 4 сравнения сигнал логической единицы снимается, поскольку п 1.

313

Далее на счетный вход счетчика 1 продолжают поступать импульсы кода делимого. При каждом превышении содержимого счетчика 1 над содержимым счетчика 2 происходит возврат счетчика 1 в состояние Единица и увеличение содержимого счетчика 3 на единицу.

После поступления т-го импульса кода делимого содержимое счетчика 1 представляет собой

р m - kn.

число импульсов кода дели- }5 мого;

число импульсов кода делителя;

число импульсов, поступивших на счетный вход первого 20 счетчика.

р п. Частное можно

п

как

2. k.-2-, пп

число d лежит в пределах

п п 1

О d 1. Если d, - - , 30

п 2

Т.е. р --2

к полученному результату деления, т.е. к содержимому счетчика 3,добавляется единица. Если 35

п же р -г- t единица к содержимому

счетчика 3 не добавляется.

На вход второго числа схемь 5 сравнения подано значение половины содержимого счетчика 2. Схема .5 сравнения, таким образом, производит сравнение содержимого счетчика 1 с половиной содержимого счетчика 2.

При поступлении импульсов кода делимого выходной сигнал схемы 5 сравнения не учитьшается, так как он не проходит через коммутатор 5.

После окончания поступления импульсов кода делимого потенциал ло- гической единицы, поступающий на вход 8 устройства, снимается. Тепер если содержимое счетчика 1 окажется больше половины содержимого счетчи}5

20

25

30

35

40

45

50

59724

ка 2, на выходе схемы 5 сравнения будет присутствовать потенциал логической единицы. Тем самым к содержимому счетчика 3 добавляется едини- , ца. Если же после окончания поступления импульсов кода делимого содержимое счетчика 1 окажется равным или меньшим половины содержимого счетчика 2, на выходе схемы 5 сравнения 10 будет присутствовать потенциал логи- ческо го нуля.

Формула изобретения Устройство для деления, содержащее три счетчика и схему сравнения, причем входы делимого и делителя устройства соединены со счетными входами соответственно первого и второго счетчиков, выходы которых .соединены с входами первого и второго чисел схемы сравнения, выход которой соединен с входом разрешения записи первого счетчг1ка, информационный вход младшего разряда которого соединен с входом логической единицы устройства, вход логического нуля которого соединен с информационными входами N-1 старших разрядов первого счетчика, выход третьего счетчика является выходом результата устройства, вход сброса устройства соединен с входами сброса первого, второго и третьего счетчиков, отличающееся тем, что, с целью повышения точности, в него введены дополнительная схема сравнения и коммутатор, при этом выход первого счетчика соединен с входом первого числа дополнительной схемы сравнения, вход i-ro разряда второго числа которой (где i 1,2,...,N-1) соединен с выходом (i+1)-ro разряда второго счетчика, вход логического нуля устройства соединен с входом N-ro разряда второго числа дополнительной схемы сравнения, выход которой соединен с первым информационным входом коммутатора, второй информационный вход которой соединен с выходом схемы сравнения, вход сопровождения делимого устройства .соединен с управля- кщим входом коммутатора, выход которого соединен со счетным входом третьего счетчика.

Ш1ЛЛЛТП11 Г1ГШЛ

ппгш

лп.

LГ

f6

ПП

LГ

fpuz.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления | 1988 |

|

SU1532921A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Преобразователь отношения двух частот в код | 1976 |

|

SU660231A1 |

| Устройство для деления | 1980 |

|

SU928344A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

Изобретение относится к области вычислительной техники и может быть использовано для деления чисел, за- .данных число-импульсным кодом. Изобретение позволяет повысить точность вычисления за счет введения операции округления результата, введения дополнительной схемы 5 сравнения и коммутатора 6 в устройство, содержащее три счетчика 1-3 и схему 4 сравнения. i сл

| Устройство для деления | 1977 |

|

SU615477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1982 |

|

SU1049906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-23—Подача