Изобретение относится к вычислительной технике и может быть использовано при построении памяти высоконадежных вы- чис.1ительных систем с пониженным энергопотреблением.

Цель изобретения - повышение надежности устройства.

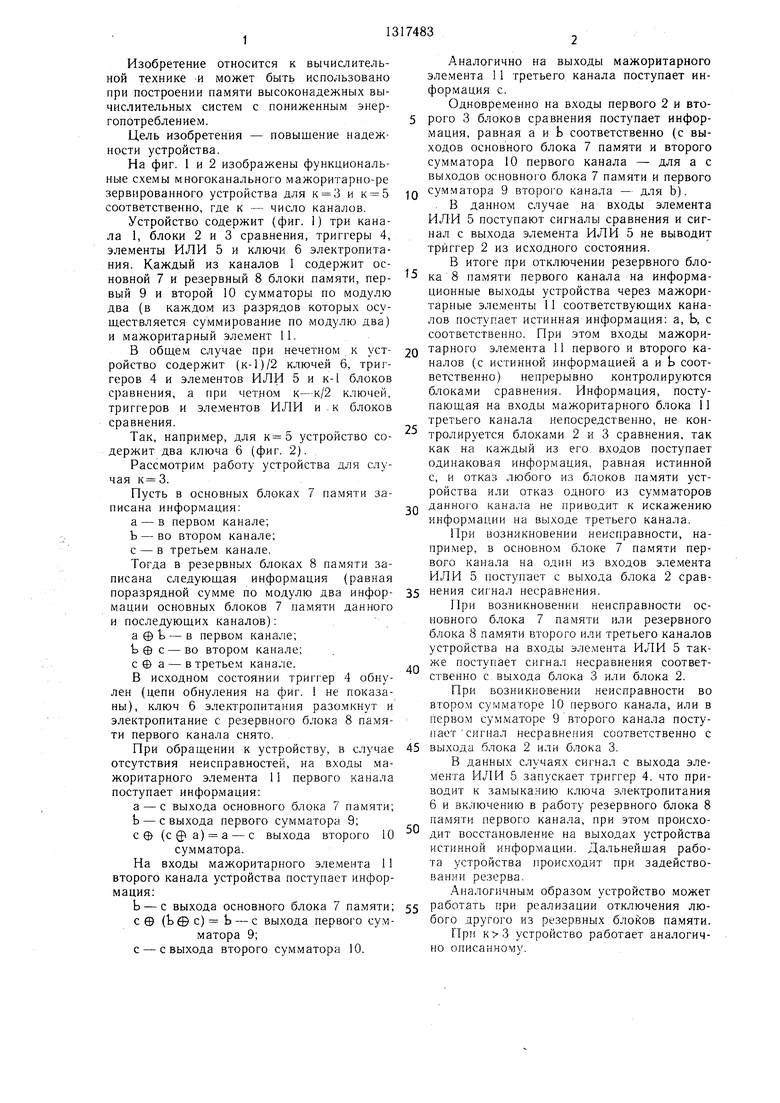

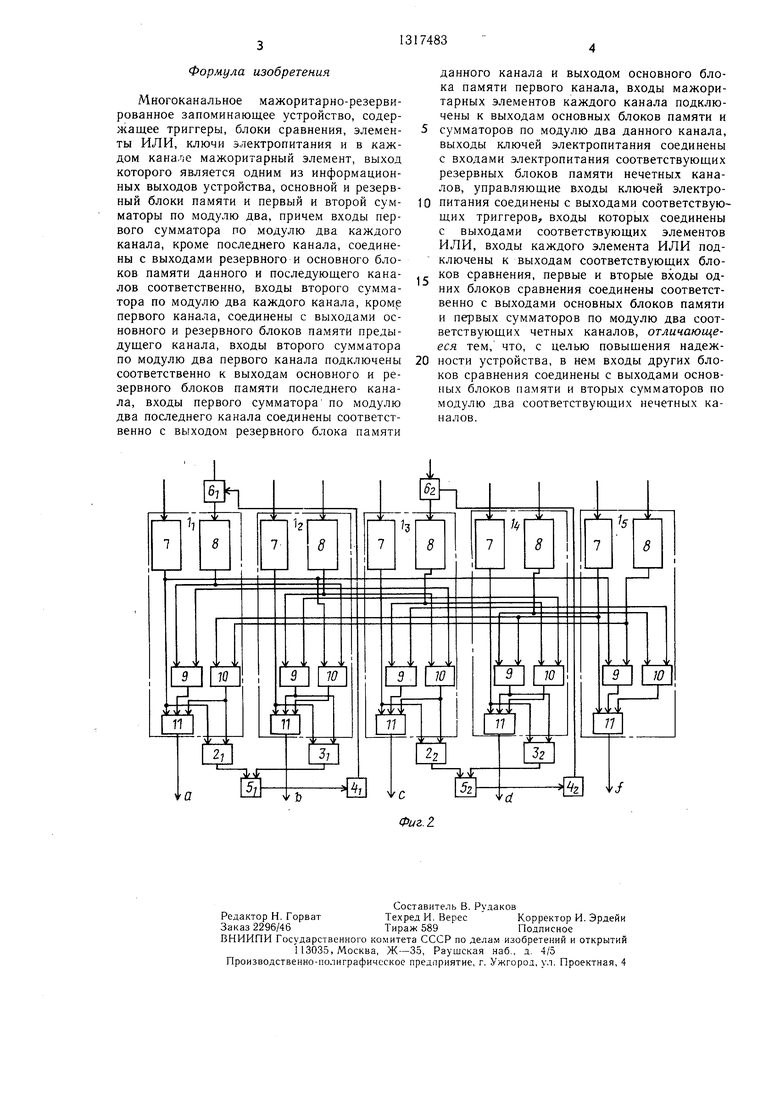

На фиг. 1 и 2 изображены функциональные схемы многоканального мажоритарно-ре зервированного устройства для к 3 и к 5 соответственно, где к - число каналов.

Устройство содержит (фиг. 1) три канала 1, блоки 2 и 3 сравнения, триггеры 4, элементы ИЛИ 5 и ключи 6 электропитания. Каждый из каналов 1 содержит основной 7 и резервный 8 блоки памяти, первый 9 и второй 10 сумматоры по модулю два (в каждом из разрядов которых осуществляется суммирование по модулю два) и мажоритарный элемент 11.

В общем случае при нечетном к устройство содержит (к-1)/2 ключей 6, триггеров 4 и элементов ИЛИ 5 и к-1 блоков с)авнения, а при четном к-к/2 ключей, триггеров и эле.ментов ИЛИ и ,к блоков сравнения.

Так, например, для устройство содержит два ключа 6 (фиг. 2).

Рассмотрим работу устройства для случая к 3.

Пусть в основных блоках 7 памяти записана информация:

а - в первом канале;

Ъ - во втором канале;

с - в третьем канале.

Тогда в резервных блоках 8 памяти записана следующая информация (равная поразрядной сумме по модулю два информации основных блоков 7 памяти данного и последующих каналов):

а ф t - в первом канале;

Ъ ф с - во втором канале;

с ф а - в третьем канале.

В исходном состоянии триггер 4 обнулен (цепи обнуления на фиг. не показаны), ключ 6 электропитания разо.мкнут и электропитание с резервного блока 8 памяти первого канала снято.

При обращении к устройству, в случае отсутствия неисправностей, на входы мажоритарного элемента 11 первого канала поступает информация:

а - с выхода основного блока 7 памяти;

Ь - с выхода первого сумматора 9;

сф (сфа) а - с выхода второго 10 сумматора.

На входы мажоритарного элемента 11 второго канала устройства поступает информация;

Ь - с выхода основного блока 7 памяти;

с ф (Ьф с) Ь - с выхода первого сумматора 9;

с - с выхода второго сумматора 10.

Аналогично на выходы мажоритарного эле.мента 11 третьего канала поступает информация с.

Одновременно на входы первого 2 и второго 3 блоков сравнения поступает информация, равная а и Ь соответственно (с выходов основного блока 7 памяти и второго сумматора 10 первого канала - для а с выходов основного блока 7 памяти и первого

Q сумматора 9 второго канала - для Ь).

В данном случае на входы элемента ИЛИ 5 поступают сигналы сравнения и сигнал с выхода элемента ИЛИ 5 не выводит триггер 2 из исходного состояния.

В итоге при отключении резервного бло5 ка 8 памяти первого канала на информационные выходы устройства через мажоритарные элементы 11 соответствующих каналов поступает истинная информация: а, Ь, с соответственно. При этом входы мажори0 тарного элемента 11 первого и второго каналов (с истинной инфор.мацией а и Ь соответственно) непрерывно контролируются блоками сравнения. Информация, поступающая на входы мажоритарного блока 11 третьего канала непосредственно, не кон тролируется блоками 2 и 3 сравнения, так как на каждый из его входов поступает одинаковая информация, равная истинной с, и отказ любого из блоков памяти устройства или отказ одного из сумматоров

Q данного кана.ча не приводит к искажению инфор.мации на выходе третьего канала.

При возникновении неисправности, например, в основном блоке 7 памяти первого канала на один из входов э.чемента ИЛИ 5 поступает с выхода блока 2 срав5 нения сигнал несравнения.

При возникновении неисправности основного блока 7 памяти или резервного блока 8 памяти второго или третьего каналов устройства на входы элемента ИЛИ 5 также поступает сигнал несравнения соответственно с выхода блока 3 или блока 2.

При возникновении неисправности во втором сумматоре 10 первого канала, или в первом сум.маторе 9 второго канала поступает сигнал несравне.чия соответственно с

5 выхода блока 2 или блока 3.

В данных случаях сигнал с выхода элемента ИЛИ 5 запускает триггер 4, что приводит к замыканию ключа электропитания 6 и включению в работу резервного блока 8 памяти первого канала, при этом происхо дит восстановление на выходах устройства истинной информации. Дальнейшая работа устройства происходит при задейство- BaHi iH резерва.

Аналогичным образом устройство может

5 работать при реализации отключения любого другого из резервных блоков памяти. При устройство работает аналогично onHcaHHOMv.

Формула изобретения

Многоканальное мажоритарно-резервированное запоминающее устройство, содержащее триггеры, блоки сравнения, элементы ИЛИ, ключи электропитания и в каждом кана/ie мажоритарный элемент, выход которого является одним из информационных выходов устройства, основной и резервный блоки памяти и первый и второй сумматоры по модулю два, причем входы первого сумматора по модулю два каждого канала, кроме последнего канала, соединены с выходами резервного и основного блоков памяти данного и последующего каналов соответственно, входы второго сумматора по модулю два каждого канала, кром первого канала, соединены с выходами ос - новного и резервного блоков памяти предыдущего канала, входы второго сумматора по модулю два первого канала подключены соответственно к выходам основного и резервного блоков памяти последнего канала, входы первого сумматора по модулю два последнего канала соединены соответственно с выходом резервного блока памяти

данного канала и выходом основного блока памяти первого канала, входы мажоритарных элементов каждого канала подключены к выходам основных блоков памяти и 5 сумматоров по модулю два данного канала, выходы ключей электропитания соединены с входами электропитания соответствующих резервных блоков памяти нечетных каналов, управляющие входы ключей электро0 питания соединены с выходами соответствующих триггеров, входы которых соединены с выходами соответствующих элементов ИЛИ, входы каждого элемента ИЛИ подключены к выходам соответствующих бло ков сравнения, первые и вторые входы одних блоков сравнения соединены соответственно с выходами основных блоков памяти и первых сумматоров по модулю два соответствующих четных каналов, отличающееся тем, что, с целью повыщения надеж0 ности устройства, в нем входы других блоков сравнения соединены с выходами основных блоков памяти и вторых сумматоров по модулю два соответствующих нечетных каналов.

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1989 |

|

SU1711237A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1354250A1 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1984 |

|

SU1234885A2 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1983 |

|

SU1182581A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ (3 ВАРИАНТА) | 2014 |

|

RU2580791C2 |

| Трехканальное мажоритарно-резервированное импульсное устройство | 1974 |

|

SU598278A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении памяти высоконадежных вычислительных систем с пониженным энергопотреблением. Цель изобретения - повышение надежности устройства. Устройство содержит триггеры 4, блоки 2, 3 сравнения, элементы ИЛИ 5, ключи 6 электропитания и в каждом канале - мажоритарный элемент 11, основной 7 и резервный 8 блоки памяти и два сумматора 9, 10 по модулю два. В устройстве исключена выдача недостоверной информации при отказе любого из сумматоров по модулю два. 2 ил. rf-i r-f-f(Л п оз 4 сх со

| Резервированное запоминающее устройство | 1977 |

|

SU710076A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Авторское свидетельство СССР № 1292516, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-15—Публикация

1985-04-23—Подача