.3

Изобретение относится к вычислительной технике и может быть использовано при построении памяти вычислительных систем повьш1енной надежности при наличии ограничений на энергопотребление.

Цель изобретения - повышение надежности устройства.

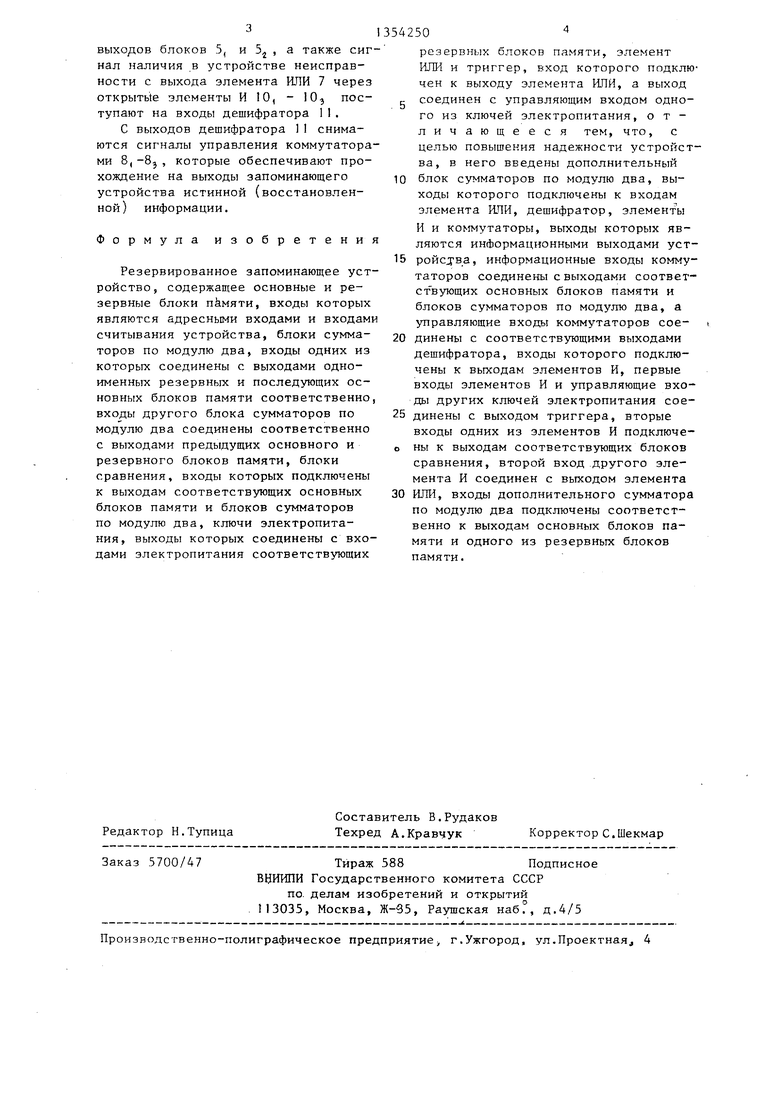

На чертеже приведена структурная схема резервированного запоминающего устройства (для трех основных и трех резервных блоков памяти).

Устройство содержит первый 1 и второй 1 ключи электропитания, первый 2,, второй 2 и третий 2, основные блоки памяти, первый 3, ;второй 3 и третий 3 резервные блоки памяти, первый 4, , второй 4,; и тре- .тнй 45 блоки, сумматоров по модулю два, блоки 5 и 5 сравнения дополнительный блок 6 сумматоров по модулю два, элемент ИЛИ 7, коммутаторы 8( - 8з, триггер 9, элементы И 10 и дешифратор 11 (цепи адреса, управления и импульсного питания не показаны).

В первом 3, и втором 3 резервных блоках содержится информация равная поразрядной сумме по модулю два информации одноименных ячеек первого 2, и второго 2, второго 2 и третьего 2, основных блоков памяти соответственно. В третьем 3, ре., зервном блоке памяти содержится информация, равная поразрядной сумме по модулю два информации одноименны ячеек основных 2 2, блоков памя ти.

Устройство работает следующим образом.

Обращение по адресу происходит одновременно ко всем блокам 2 и 3 памяти. При полностью исправном состоянии устройства ключи 1| и Ig находятся в разомкнутом состоянии, в результате чего резервные блоки 3, и 3j памяти обесточены, т.е. находятся в холодном резерве,- Информация, считанная при одновременном о ё раще- нии, из основных блоков 2| т 25 пам ти через соответствующие коммутатор 8, т В5 поступает на информационные выходы устройства. Одновременно информация, считанная из основных 2 2 п резервного 3, блоков памяти, поступает на соответствующие входы блока 6, с выходов которого, при отсутствии неисправностей в блоках памяти, снимается нуленая информация, которая Поступает на входы элемента ИЛИ 7, с которого снимается сигнал испра1эности, который не пере- водит триггер 9 в другое устойчивое состояние. При этом с выхода триггера 9 снимается управляющий сигнал,

удерживающий клю -и; /,

J в преж

нем (разомкнутом; состоянии и запрещающий прохощение сигналов с выхочере-з элементы И 10, - 10 на входы дешифратора 11. В результате с выходов дешифратора 11 снимаются управляющие сигналы, удерживающие коммутаторы 8| - 8 Б прежнем состоянии.

При наличии неисправности в одном из блоков 2, т 2,. или 3 памяти, приводящей к ошибке любой кратности,

с выходов блсжа 6 на входы элемента ИЛИ 7 поступает нулевая информация (Е искаженных разрядах появляются единичные сигналы), в результате чего с выхода элемента ИЛИ 7 на вход

триггера 9 поступает сигнал неисправности. Сигнал неисгравности переводит триггер 9 в устойчивое состояние и поступг.ет на вход третьего элемента И 1Oj.

Сигнал с выхода триггера 9 поступает на входы элементов 1 О - 10 и ia управлягош;ие входы ключей 1 , и 1 , что пр водит к питающего напряжения на первый , и второй 3 резервные блоки памяти и задействованию в работ всех блоков памяти запоминающего устройс;тва. При этом с выходов блов:ов 4( -- 4, на входы соответствующих коммутаторов 8,-83

поступает информация равная поразрядной сумме по модулю два информации первого резервного 3, и второго основного 2 , второго резервного 3 и третьего основио1 0 2„, второго

J

резервного 3 и второго основного 2 блоков памяти соответственно Данная информация совпадает при отсутствии в устройстве неисправности с информацией соответствующих основных блоков памяти 2,-2 и, следовательно, может быть использована как резервная при парировании неисправности одного из основных блоков 2 ,-2 памяти.

1-1нформация с выходов блоков 4 и

4j поступает также на один из входов соответствующих блоков 5, и 5. Результаты сравнения информации с

выхо/ioB блоков 5, и 5 , а также сиг нал наличия в устройстве неисправности с выхода элемента ИЛИ 7 через открытые элементы И 10, - 10 поступают на входы дешифратора 11,

С выходов дешифратора 11 снимаются сигналы управления коммутаторами 8,-8j, которые обеспечивают прохождение на выходы запоминающего устройства истинной (восстановленной) информации.

Формула изобретени

Резервированное запоминающее устройство, содержащее основные и резервные блоки пймяти, входы которых являются адресными входами и входам считывания устройства, блоки сумматоров по модулю два, входы одних из которых соединены с выходами одноименных резервных и последующих основных блоков памяти соответственно входы другого блока сумматоров по модулю два соединены соответственно с выходами предыдущих основного и резервного блоков памяти, блоки сравнения, входы которых подключены к выходам соответствующих основных блоков памяти и блоков сумматоров по модулю два, ключи электропитания, выходы которых соединены с входами электропитания соответствующих

Редактор Н.Тупица Заказ 5700/47

Составитель В.Рудаков Техред А.Кравчук

Корректор

Тираж 588Подписное

ВЦИИПИ Государственного комитета СССР

по. делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб°, д.4/5

Производственно-полиграфическое предприятие г.Ужгород, ул.Проектнаяj 4

54250

резервных блоков памяти, элемент ИЛИ и триггер, вход которого подключен к выходу элемента ИЛИ, а выход g соединен с управляющим входом одного из ключей электропитания, отличающееся тем, что, с целью повышения надежности устройства, в него введены дополнительный 10 блок сумматоров по модулю два, выходы которого подключены к входам элемента Ш1И, дешифратор, элементы И и коммутаторы, выходы которых являются информационными выходами уст- 15 ройсд ва, информационные входы коммутаторов соединены с выходами соответ- ст вующих основных блоков памяти и блоков сумматоров по модулю два, а управляющие входы коммутаторов сое- 20 динены с соответствующими выходами дешифратора, входы которого подключены к выходам элементов И, первые входы элементов И и управляющие входы других ключей электропитания сое- 25 динены с выходом триггера, вторые

входы одних из элементов И подключе- о ны к выходам соответствующих блоков сравнения, второй вход другого элемента И соединен с выходом элемента 30 ИЛИ, входы дополнительного сумматора по модулю два подключены соответственно к выходам основных блоков памяти и одного из резервных блоков памяти.

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1985 |

|

SU1317483A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1510012A1 |

| Устройство для обнаружения неисправностей цифровых систем | 1979 |

|

SU949659A2 |

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1984 |

|

SU1234885A2 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении памяти быстродействующих вычислительных систем повышенной надежности при наличии ограничений на энергопотребление. Цель изобретения - повышение надежности устройства. Устройство содержит кгйочи I электропитания,основные 2 и резервные 3 блоки памяти, блоки 4 и 6 сумматоров по модулю два, блоки 5 сравнения, элемент i-ШИ 7, коммутаторы В, триггер 9, элементы И 10 и дешифратор П. 1 ил. со СП 4 tsD СП О

| Резервированное запоминающее устройство | 1982 |

|

SU1037347A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1985 |

|

SU1317483A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-23—Публикация

1985-08-13—Подача