;0

СП

СХ)

.сд сд

314

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с коррекцией ошибок.

Цель изобретения - повышение быстродействия устройства путем совмещенного выполнения последовательных операций считывания информации.

j На фиг, 1 представлена функцио-

Iнальная схема ЗУ с коррекцией ошибок

I на фиг. 2 - функциональная схема

I блока управления.

Устройство содержит регистр 1 адреса, информационные входы которого являются адресными входами устройства, накопитель 2, сумматор 3 по модулю два, распределитель 4 импульсов, регистр 5 информации, блок 6 коррекции, формирователь 7 кода оши- бок, элементы И 8, регистр 9 данных и блок 10 управления.

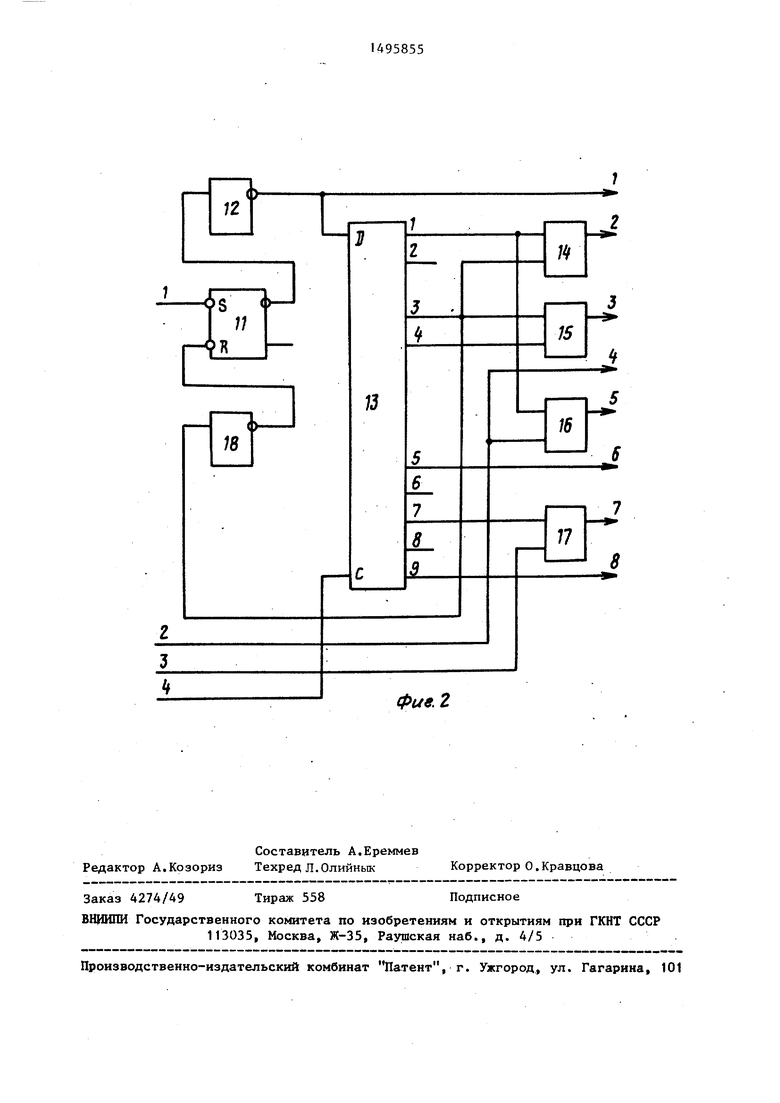

Блок 10 управления (фиг. 2) содержит триггер 11, первый инвертор |12, регистр 13 сдвига, элемент ИЛИ J14, первый 15, второй 16 и третий :17 элементы И, второй инвертор 18.

; Устройство работает следующим об- I разом.

I Код адреса поступает на информаци- |онные входы регистра 1 адреса, после :чего на вход обращения устройства подступает уровнем логического О (в- ;дальнейшем - уровень О) импульсный сигнал обращения к устройству. Сигнал обращения устанавливает инверсный выход триггера 11 блока 10 управления в состояние логического О, Сигнал уровня О с инверсного выхо- да триггера 11 приводит к появлению на выходе первого инвертора 12 уровня логического 1 (в дальнейшем - уровня/). Сигнал с выхода инвертора 12 поступает на информационный вход регистра 13 сдвига и через первый выход блока 10 управления на вход записи регистра 1 адреса. По возрастающему фронту на входе записи регистра 1 адреса производится запис поступившего кода адреса. С выходов регистра 1 адреса записанный код адреса поступает на адресные входы накопителя 2.

Очередной фронт прямоугольного импульса непрерывной последовательности, условно принимаемый за первый импульс, поступает через четвертый вход блока 10 управления на тактовый

0

5 0

5

0

5 0 д д

5

вход регистра 13 сдвига и приводит к появлению уровня 1 на первом выходе регистра 13 сдвига ввиду наличия Уровня 1 на его информационном входе. Уровень 1 с первого выхода регистра 13 сдвига, поступая на первый вход элемента ИЛИ I4, приводит к появлению на его выходе уровня 1, который через второй выход блока 10 управления поступает на вход выборки накопителя 2 и разрешает выборку информации по коду адреса, который присутствует на адресных входах накопителя 2.

Одновременно уровень 1 с первого выхода регистра 13 сдвига поступает на первый вход второго элемента И 16 и, в случае наличия на его втором входе уровне 1, поступающего .через второй вход блока 10 управления с входа режима устройства (что соответствует разрешению имитации ошибки), приводит к появлению на выходе первого элемента И 16 уровня который через пятый выход блока 10 управления, поступая на счетный вход распределителя 4 импульсов, приводит к формированию уровня | на одном из очередных выходов распределителя 4 импульсов, так как для данного случая уровень 1 с второго входа второго элемента И 16 через четвертый выход блока 10 управления поступает на вход сброса распределителя 4 импульсов и тем самым разрешает его работу.

Поступающий на вход синхронизации устройства второй импульс приводит к появлению уровня 1 на втором выходе регистра 13 сдвига и-сохраняет - уровень 1 на его первом выходе. Второй выход регистра 13 сдвига не используется. Наличие неиспользуемого второго выхода регистра 13 сдвига необходимо для увеличения времени выборки информации из накопителя 2, Поступающий на выход синхронизации устройства третий импульс приводит к появлению уровня 1 на третьем выходе регистра 13 сдвига и сохраняет уровни 1 на его первом и втором выходах. С третьего выхода регистра 13 сдвига уровень 1 поступает на второй вход элемента ИЛИ I4 и обеспечивает сохранение на его выходе уровня 1. Одновременно уровень 1 с третьего выхода регистра 13 сдвига поступает на первый вход

первого элемента И 15 и ввиду наличия на его втором входе уровня О, поступающего с четвертого выхода регистра 13 сдвига, не приводит ft изменению состояния его выхода. Одновременно уровень 1 с третьего выхода регистра 13 сдвига поступает на вход второго инвертора 18 и присчитывания накопителя 2 и разрегплет выдачу выбранной инф - рмации на вмхо- ды накопителя 2, откуда она поступает на первые входы сумматоров 3 но модулю два, на вторых входах присутствуют уровни О (для случая отсутствия разрешения имитации ошибки) или на одном из вторых входов кото

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1317484A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1354248A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249591A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1554030A1 |

| Резервированное оперативное запоминающее устройство | 1987 |

|

SU1471225A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с коррекцией ошибок. Цель изобретения - повышение быстродействия устройства путем совмещенного выполнения последовательных операций считывания информации. Устройство содержит регистр 1 адреса, накопитель 2, сумматоры 3 по модулю два, распределитель 4 импульсов, регистр 5 информации, блок 6 коррекции, формирователь 7 кода ошибок, элементы И 8, регистр 9 данных и блок 10 управления. В устройство введен дополнительный регистр, входы которого подключены к информационным выходам накопителя, а выходы - к блокам обнаружения и коррекции ошибок. Запись считанной из накопителя информации в регистр позволяет совместить во времени обнаружения и исправление ошибок, и считывание новой информации из накопителя. 1 з.п. ф-лы, 2 ил.

водит, к появлению на его выходе уров- Q рых присутствует уровень 1 (для ня О, который, поступая на сбрасы20

25

Случая разрешения имитации ошибки). В первом случае на выходах сумматоров 3 по модулю два появляется информация, не содержащая принудительно введенной ошибки, а во втором случае - и принудительно введенной ошибки в одной из соответствующих разрядов, в зависимости от того, на каком из сумматоров 3 по модулю два присутствует уровень 1, поступающий с одного из выходов распределителя 4 импульсов. Р нформация С выхо- |дов сумматоров 3 по модулю два поступает на информационные входы регистра 5 информации.

Поступающий на вход синхронизации устройства пятый импульс приводит к появлению уровня 1 на пятом выходе регистра 13 сдвига, приводит к появформирование на выхо- зо лению уровня О на его втором выходе и сохраняет уровни 1 на его третьем и четвертом выходах, С пятого выхода регистра 13 сдвига уровень 1 через шестой выход блока 10 управления отступает на вход записи регистра 5 информации и производит своим фронтом запись в него информации, поступившей на его информационные входы. Информация с первой и второй групп выходов регистра 5 информации поступает на входы формирователя 7 кода ошибок, где она анализируется на предмет наличия ошибок и где. формируется, в случае наличия ошибок, д5 код ошибок, который поступает на вторые входы элементов И 8. Рабочая информация с первой группы выходов регистра 5 информации поступает также на первую группу входов блока 6 коррекции.

Поступающий на вход синхронизации устройства шестой импульс приводит к появлению уровня 1 на шестом выходе регистра 13 сдвига и уровня О на его третьем выходе и сохраняет уровни 1 на его четвертом и пятом выходах. С третьего выхода регистра 13 сдвига уровень О поступает на второй вход элемента ИЛИ 14 и привающий вход триггера 11, приводит к появлению на его инверсном выходе уровня 1. Сигнал с инверсного выхода триггера 11, поступая на вход )5 первого инвертора 12, приводит к появлению на выходе первого инвертора 12 уровня .О, который поступает на информационный вход регистра I3 сдвига. Во время присутствия уровня О на сбрасывающем входе триггера 11 на его инверсном выходе будет присутствовать уровень 1 независимо от того, какой уровень присутствует на установочном входе триггера 11, Этим и обеспечивается защита от приема преждевременных (до окончания присутствия уровня О на сбрасываю- щеы входе триггера 11) обращений и обеспечивается

дах регистра 13 сдвига импульсов, длительность которых равна длительности трех импульсов, поступающих на вход синхронизации устройства.

Поступающий на вход синхронизации устройства -четвертый импульс приводит к появлению уровня 1 на четвертом выходе регистра 13 и уровня О на его первом выходе, так как на его информационном входе присутствует уровень О, и сохраняет уровни 1 на его втором и третьем выходах. С первого выхода регистра 13 сдвига уровень О поступает на первый вход второго элемента И 16, и при условии наличия уровня I на его втором входе, что соответствует разрешению имитации ошибки, приводит к появлению уровня О на его выходе, что соответствует окончанию счетного импульса, поступающего на распределитель 4 импульсов. С четвертого выхода регистра 13. сдвига уровень 1 поступает на второй вход первого элемента И 15 и ввиду наличия на его первом входе уровня 1 приводит к появлению на его выходе уровня 1, который через третий выход блока 10 управления поступает на вход разрешения

35

40

50

55

20

)5

25

)5

зо д5

35

зо д5

40

зо д5

50

водит к появлению на его выходе уровня О, так как на ei o первом входе уже присутствует уровень О. Появление на выходе элемента ШМ 14 уров :Ня О соответствует окончанию вы- |борки информации с накопителя 2. С третьего выхода регистра 13 сдвига уровень О одновременно поступает на первый вход первого элемента И 15 приводит к появлению на его выходе уровня О, что соответствует окон- шнию выдачи на выход информации с накопителя 2. С третьего выхода регистра 13 сдвига уровень О одновременно поступает на вход второго инвертора 18 и приводит к появлению на его выходе уровня 1, который, поступая на сбрасывающий вход триггера 11, разрешает переключение триггера 11 при поступлении на его установочный вход уровня О, который может поступать во время шестого импульса при совмещенном режиме работы или после окончания полного цикла работы устройства при обычном режиме работы. Наличие свободного шестого выхода регистра 13 сдвига необходимо для увеличения времени (обработки информации формирователем |7 кода ошибок.

I Поступающий на вход синхрониза- Ьдии устройства седьмой импульс при- Ьодит к появлению уровня 1 на седь мом выходе регистра 13 сдвига и Уровня О на его четвертом выходе :И сохраняет уровни 1 на его пятом и шестом выходах, С седьмого выхода регистра 13 сдвига уровень 1 поступает на первый вход третьего элемента И 17 и в случае наличия на его втором входе уровня 1, поступающего через третий вход бло14а 10 управления с входа режима работы устройства, что соответствует разрешению коррекции ошибок, приводит к появлению на выходе третьего элемента И 17 уровня , которьй через седьмой выход блока 10 управления поступает на первые входы элементов И 8 и разрешает прохождение кода ошибки на вторую группу входов блока 6 коррекций, который производит, при необходимости, коррекцию информации, поступившей на первую группу его- входов.

Поступающий на вход синхронизаци устройства восьмой импульс приводит к появлению уровня 1 на восьмом

5

0

5

0

5

0

5

0

5

выходе регистра 13 сдвига и уровня О на его пятом выходе и сохраняет уровни 1 на его шестом и седьмом выходах. Наличие свободного восьмого выхода регистра 13 сдвига необходимо для увеличения времени коррекции ошибок блоком 6 коррекции.

Поступаюрщй на вход синхронизации устройства девятый импульс приводит к появлению уровня 1 на девятом выходе регистра 13 сдвига и уровня О на его шестом выходе и сохраняет уровни 1 на его седьмом и восьмом выходах. С девятого выхода регистра 13 сдвига уровень 1 поступает через восьмо й выход блока 10 управления на вход записи- регистра 9 данных и производит запись своим фронтом информации, поступившей на его информационные входы. Записанная в регистр 9 данных информация через информационные выходы устройства поступает на входы других устройств вычислительной машины для ее последующей записи.

Поступающий на вход синхронизации устройства десятый импульс приводит к появлению уровня О на седьмом выходе регистра 13 сдвига и сохраняет уровни 1 на его восьмом и девятом выходах. С седьмого выхода регистра 13 сдвига уровень О, поступая на первый вход третьет о элемента И 17, приводит к появлению на его выходе уровня О, который, поступая на вторые входы элементов И 8, запрещает дальнейшее поступление кода ошибки на вторую группу входов блока 6 коррекции.

Поступающий на вход сийхрониза- цин устройства одиннадцатый импульс приводит к появлению уровня О на восьмом выходе регистра 13 сдвига и сохраняет уровень 1 на его девятом выходе. Это необходимо для увеличения времени записи информации другими .устройствами вычислительной машины. Увеличение данного времени повьш1ает достоверность записи информации путем исключения ошибок, вызванных переходными процессами при передаче ее от одного устройства к другому.

Поступающий на вход синхронизации устройства двенадцатый импульс приводит к появлению уровня О на девятом выходе регистра 13 сдвига, что

соответствует окончанию полного цикл работы устройства.

При поступлении очередного сиг- нала обращения устройство работает ансшогичным образом, В случае отсутствия обращений к устройству и поступления на вход синхронизации устройства последующих импульсов блок 10 управления сохраняет исходное сое- тояние, при котором обеспечивается возможность приема сигналов обращени к устройству,

В совмещенном режиме предлагаемое ЗУ с коррекцией ощибок при поступле- НИИ первого сигнала обращения к устройству в течение времени поступлени первых шеСти синхронизирующих импульсов работает аналогично обычному режиму работы. Во время шестого импуль са благодаря общей синхронизации процессора и устройства поступают новые код адреса и сигнал обращения, который обеспечивает переключение триггера 11, запись кода адреса в регистр 1 адреса и подачу в течение последующих трех синхронизирующих импульсов уровня 1 на информационный вход регистра 13 сдвига. После этого поступивший седьмой импульс приводит к появлению уровня 1 на седьмом и одновременно на первом выходах регистра 13 сдвига, приводит к появлению уровня О на его четвертом выходе и сохраняет уровни 1 на его пятом и шестом выходах. Появление уровня 1 на первом выходе регистра 13 сдвига соответствует выдаче блоком 10 управления нового второго импульса на вход выборки накопителя 2, в то же самое время появление уровня 1 на седьмом выходе регистра 13 сдвига обеспечивает прохождение, в случае наличия разрешения коррекции ошибки, кода ошибок на вторую груп- пу входов блока 8 коррекции.

Поступающий восьмой импульс приводит к появлению уровня t на восьмом и на втором выходах регистра 13 сдвига и уровня О на его пя- том выходе и сохраняет уровни 1 на его первом, шестом и седьмом выходах. Это соответствует продолжению процесса выборки новой информации в накопителе 2 и одновременно обеспечивает коррекцию при необходимое - ти информации блоком 8 коррекции.

Поступающий девятый импульс приводит к появлению уровня I на

|Q

15 20 5 0 д д

.

35

5

третьем и девятом выходах регистра 13 сдвига и уровня О на его шестом выходе и сохраняет уровни 1 на его первом, втором, седьмом и восьмом выходах. Это соответствует продолжению процесса выборки информации в накопителе 2, обеспечивает формирование уровня О на информационном входе регистра 13 сдвига и одновременно обеспечивает запись ранее выбранной информации в регистр 9 данных.

Поступающий десятый импульс приводит К появлению уровня 1 на четвертом выходе регистра I3 сдвига и уровня О на его первом и седьмом выходах и сохраняет уровни 1 на его втором, третьем, восьмом и девятом выходах. Это обеспечивает формирование сигнала -разрещения считывания информации с накопителя 2 и одновременно обеспечивает передачу ранее считанной информации к другим устройствам вычислительной машины.

Поступающий одиннадцатый импульс приводит к появлению уровня 1 на пятом выходе регистра 13 сдвига и уровня О на его втором и восьмом выходах и сохраняет уровни 1 на его третьем, четвертом и девятом выходах. Это обеспечивает запись считанной с накопителя 2 информации в регистр 5 информации и одновременно обеспечивает продолжение процесса передачи ранее считанной информации к другим устройствам для ее записи.

Поступающий двенадцатый импульс приводит к появлению уровня 1 на шестом выходе регистра 13 сдвига и уровня О на третьем и девятом выходах и сохраняет уровни 1 на его четвертом и пятом выходах. Это дает возможность приема нового сигнала обращения, т,е. блок 10 управления находится в том состоянии, в котором он был после поступления шестого импульса.

При поступлении нового кода адреса и нового сигнала обращения блок 10 управления повторяет свою работу аналогично, начиная с седьмого по дв енадцатый импульс, при этом код адреса может быть произвольным.

Формула изобретен и я

1, Запоминающее устройство с коррекцией ошибок, содержащее регистр

адреса, информационные входы которого являются адресными входами устройства, накопитель, адресные входы которого подключены к выходам регист ра адреса, формирователь кода ошибок, распределитель импульсов, группу сумматоров по модулю два, группу элементов И, блок коррекции, регистр данных, выходы которого являются ни- формационными выходами устройства, блок управления, первый, второй, третий.входы обращения, первый и второй входы задания режима которого являются одноименными входами устрой- ства, первый выход блока управления подключен к входу записи регистра,адреса, первые и вторые входы сумматоров по модулю два подключены соответственно к выходам накопителя и выходам распределителя импульсов, выходы формирователя кода ошибок подключены к вторым входам элементов И, выходы которых подключены к вторым входам блока коррекции, информа- ционные входы регистра данных подключены к выходам блока коррекции, отличающееся тем, что, с целью повышения быстродействия устройства, в него введен регистр информации, информационные входы которого подключены к выходам сумматоров по модулю два, первые выходы регистра информации подключены к первы входам блока коррекции и первым вхо- дам формирователя кода ошибок, вторые входы которого подключены к вторым выходам регистра информации, выходы с второго по восьмой блока управления подключены соответственно к входам выборки и разрешения считывания накопителя, входу сброса и счетному входу распределителя импульсов, входу записи регистра информации, соединенным между собой первым входам элементов И и входу записи регистра данных, вход синхронизации блока управления является одноименным входом устройства.

2, Устройство по п. 1, отличающееся тем, что блок управления содержит триггер, первый и второй инверторы, первый, второй и третий элементы И, элемент ИЛИ,регистр сдвига, информационный вход которого подключен к выходу первого инвертора и первому выходу блока управления, вход первого инвертора подключен к инверсному выхЬду триггера, установочный вход и вход сброса Которого подключены соответственно к входу обращения блока управления и выходу второго инвертора, тактовый вход регистра сдвига подключен к входу синхронизации блока управления, первый выход регистра сдвига подключен к первым входам второго элемента И и элемента ИЛИ, выход которого является вторым выходом блока управления, второй вход элемента ИЛИ подключен к третьему выходу регистра сдвига, входу второго инвертора и первому входу первого элемента И, выход которого является третьим выходом блока управления, второй вход первого элемента И подключен к-четвертому выходу регистра сдвига, второй вход второго элемента И подключе к второму входу задания режима и четвертому выходу блока управления, выход второго элемента И является пятым выходом блока управления, пятый и девятый выходы регистра сдвига являются соответственно шестым и восьмым выходами блока управления первый и второй входы третьего элемента И соединены соответственно с седьмым выходом регистра сдвига и первым входом задания режима блока управления.

| Шигин А.Т., Дерюгин А.А | |||

| Цифровые вычислительные машины | |||

| М.: Энергия, 1976, с | |||

| Мусоросжигательная печь | 1923 |

|

SU495A1 |

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1317484A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-11—Подача