Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующей постоянной памяти вычислительных машин.

Цель изобретения - повышение быстродействия устройства.

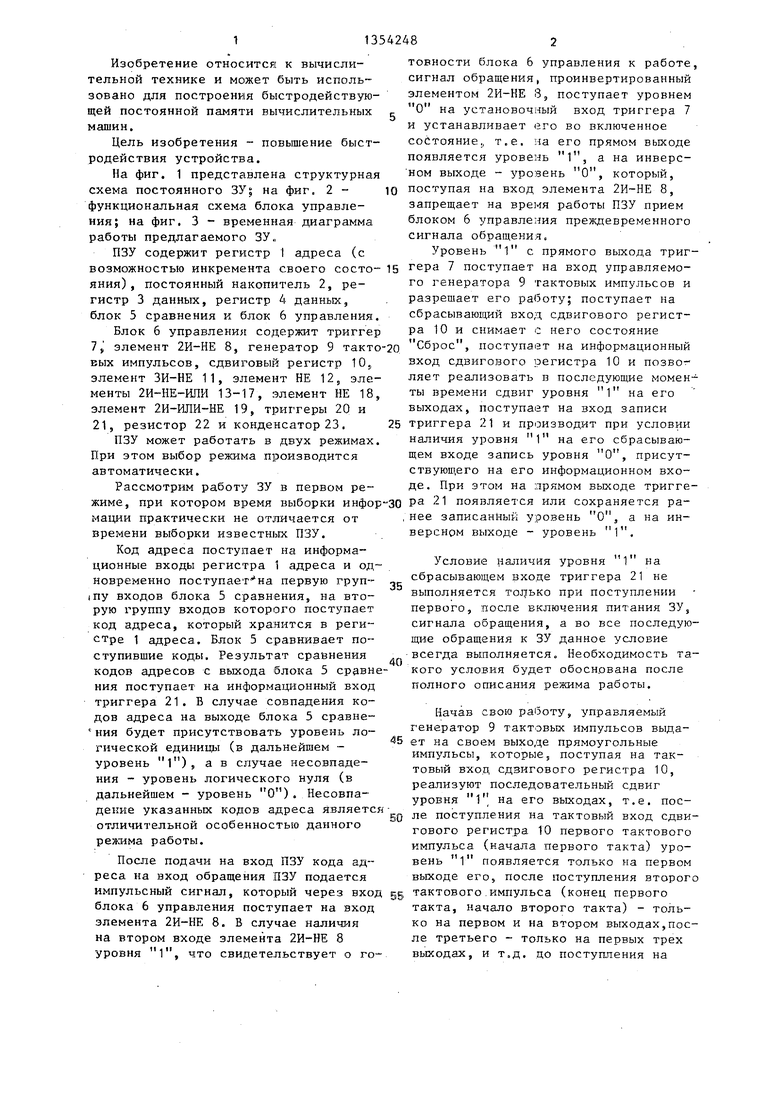

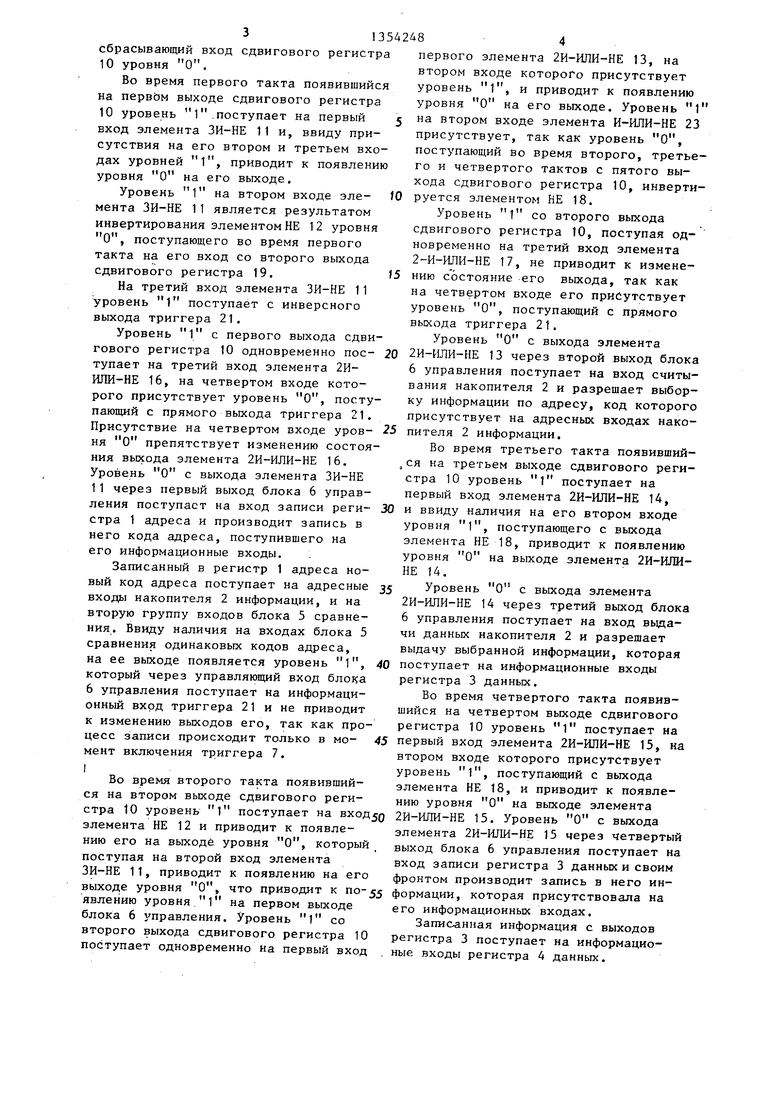

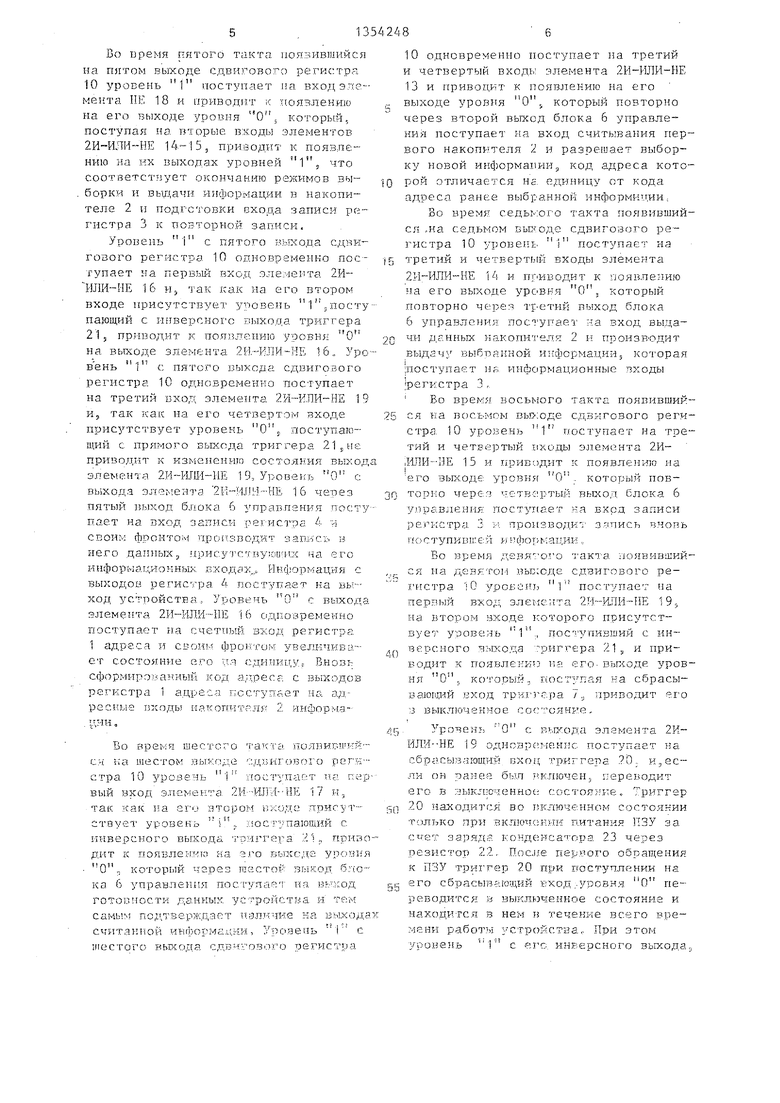

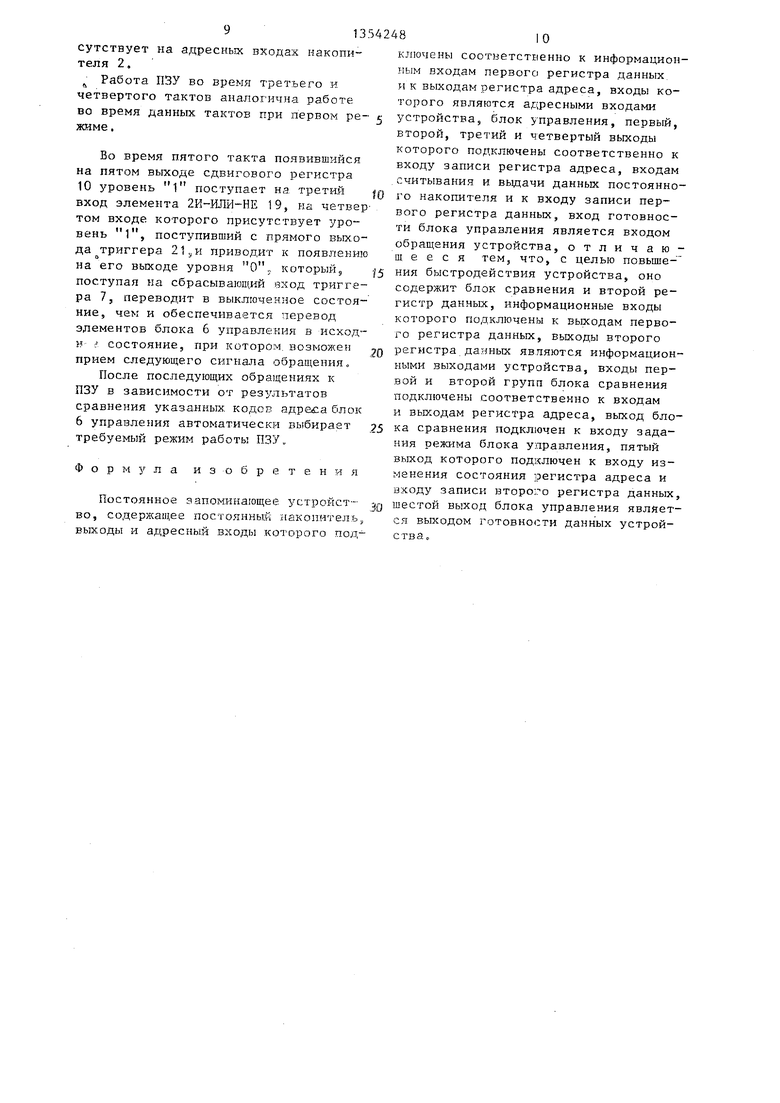

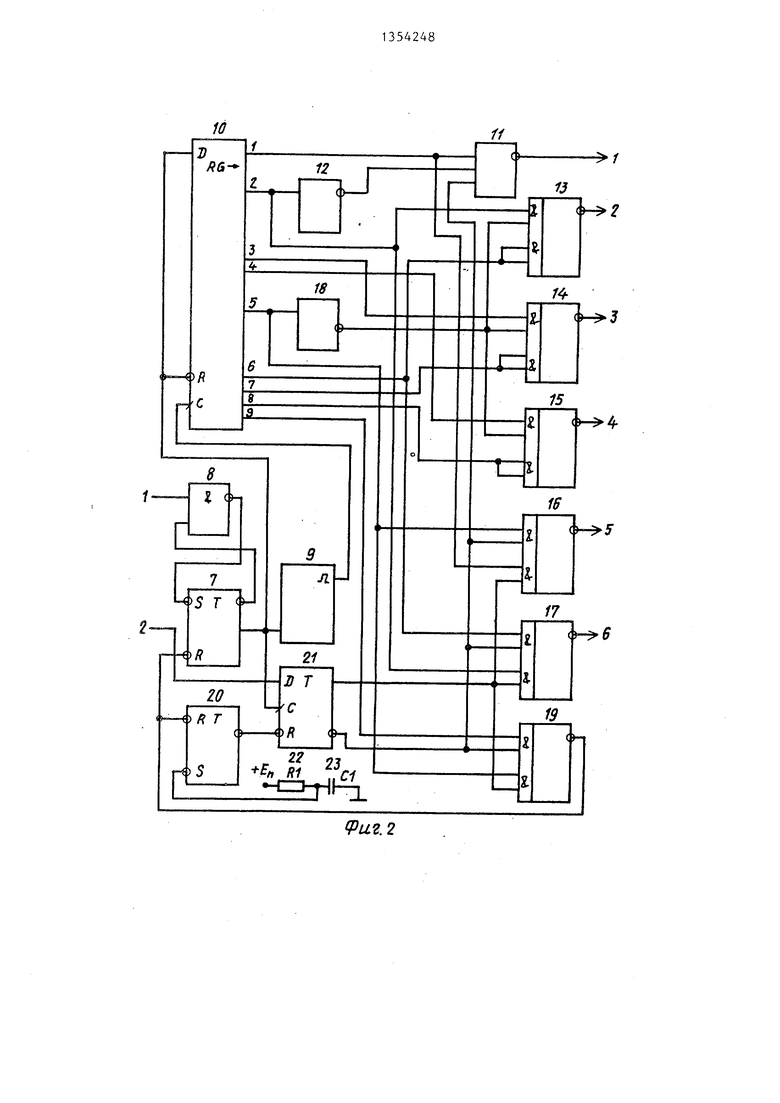

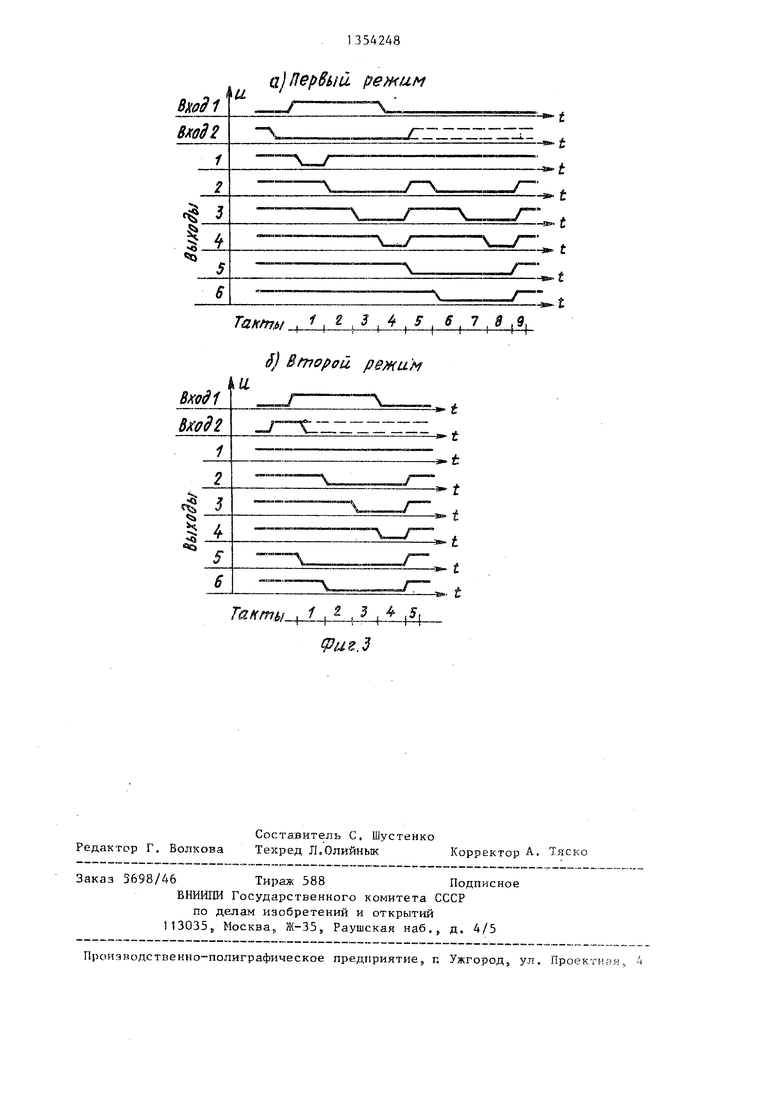

На фиг, 1 представлена структурная схема постоянного ЗУ§ на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временная диаграмма работы предлагаемого ЗУ.

ПЗУ содержит регистр 1 адреса (с

товности блока 6 управления к работе, сигнал обращения, проинвертированный элементом 2И-НЕ 8, поступает уровнем О на установочный вход триггера 7 и устанавливает его во включенное состояние., т.е. на его прямом выходе появляется уровень 1, а на инверс ном выходе уровень О, который, 10 поступая на вход элемента 2И-НЕ 8, запрещает на время работы ПЗУ прием блоком 6 управления преждевременного сигнала обращения.

Уровень 1 с прямого выхода триг- возможностыо инкремента своего состо- 15 гера 7 поступает на вход управляемо- яния), постоянный накопитель 2, ре- го генератора 9 тактовых импульсов и гистр 3 данных, регистр 4 данньк, , разрешает его работу; поступает на блок 5 сравнения и блок 6 управления. Блок 6 управления содержит триггер

сбрасывающий вход сдвигового регистра 10 и снимает с него состояние

7, элемент 2И-НЕ 8, генератор 9 такто-20. Сброс, поступает на информационный вых импульсов, сдвиговый регистр 10, элемент ЗИ-НЕ 11, элемент НЕ 12, элементы 2И-НЕ-ИПИ 13-17, элемент НЕ 18, элемент 2И-ИЛИ-НЕ 19, триггеры 20 и 21, резистор 22 и конденсатор 23.

ПЗУ может работать в двух режимах. При этом выбор режима производится автоматически.

Рассмотрим работу ЗУ в первом ревход сдвигового регистра 10 и позвог ляет реализовать в последующие моменты времени сдвиг уровня 1 на его выходах, поступает на вход записи 25 триггера 21 и производит при условии наличия уровня 1 на его сбрасывающем входе запись уровня О, присутствующего на его информационном входе. При этом на прямом выходе триггежиме, при котором время выборки инфор-30 Р 21 появляется или сохраняется ра,нее записанный уровень О, а на инмации практически не отличается от времени выборки известных ПЗУ.

Код адреса поступает на информационные входы регистра 1 адреса и од новременно поступает на первую груп- |Пу входов блока 5 сравнения, на вторую группу входов которого поступает код адреса, который хранится в регистре 1 адреса. Блок 5 сравнивает поступившие коды. Результат сравнения кодов адресов с выхода блока 5 сравнения поступает на информационный вход триггера 21. В случае совпадения кодов адреса на выходе блока 5 сравне- ния будет присутствовать уровень логической единищз (в дальнейшем - уровень 1), а в случае несовпадения - уровень логического нуля (в дальнейшем - уровень О). Несовпадение указанных кодов адреса является отличительной особенностью данного режима работы.

После подачи на вход ПЗУ кода адреса на вход обращения ПЗУ подается импульсный сигнал, который через вход блока 6 управления поступает на вход элемента 2И-НЕ 8, В случае наличия на втором входе элемента 2И-НЕ 8 уровня 1, что свидетельствует о го35

40

верснрм выходе - уровень 1.

Условие наличия уровня 1 на сбрасывающем входе триггера 21 не выполняется при поступлении первого, после включения питания ЗУ, сигнал.а обращения, а во все последующие обращения к ЗУ данное условие -всегда выполняется. Необходимость такого условия будет обоснована после полного описания режима работы.

Начав СБОЮ работу, управляемый генератор 9 тактовьсх импульсов выда45 ет на своем выходе прямоугольные импульсы, которые, поступая на тактовый вход сдвигового регистра 10, реализуют последовательный сдвиг уровня 1 на его выходах, т.е. пос50 ле поступления на тактовый вход сдвигового регистра 10 первого тактового импульса (качала первого такта) уровень 1 появляется только на первом выходе его, после поступления второго

gg тактового.импульса (конец первого такта, начало второго такта) - только на первом и на втором выходах,после третьего - только на первых трех выходах, и т.д. до поступления на

товности блока 6 управления к работе, сигнал обращения, проинвертированный элементом 2И-НЕ 8, поступает уровнем О на установочный вход триггера 7 и устанавливает его во включенное состояние., т.е. на его прямом выходе появляется уровень 1, а на инверсУровень 1 с прямого выхода триг- гера 7 поступает на вход управляемо- го генератора 9 тактовых импульсов и разрешает его работу; поступает на

сбрасывающий вход сдвигового регистра 10 и снимает с него состояние

Сброс, поступает на информационный

вход сдвигового регистра 10 и позвог ляет реализовать в последующие моменты времени сдвиг уровня 1 на его выходах, поступает на вход записи триггера 21 и производит при условии наличия уровня 1 на его сбрасывающем входе запись уровня О, присутствующего на его информационном входе. При этом на прямом выходе тригге

ерснрм выходе - уровень 1.

Условие наличия уровня 1 на сбрасывающем входе триггера 21 не выполняется при поступлении первого, после включения питания ЗУ, сигнал.а обращения, а во все последующие обращения к ЗУ данное условие всегда выполняется. Необходимость такого условия будет обоснована после полного описания режима работы.

Начав СБОЮ работу, управляемый енератор 9 тактовьсх импульсов выдат на своем выходе прямоугольные импульсы, которые, поступая на тактовый вход сдвигового регистра 10, реализуют последовательный сдвиг уровня 1 на его выходах, т.е. после поступления на тактовый вход сдвигового регистра 10 первого тактового импульса (качала первого такта) уровень 1 появляется только на первом выходе его, после поступления второго

тактового.импульса (конец первого такта, начало второго такта) - только на первом и на втором выходах,после третьего - только на первых трех выходах, и т.д. до поступления на

сбрасывающий вход сдвигового регистра 10 уровня О,

Во время первого такта появившийся на первом выходе сдвигового регистра 10 уровень 1 .поступает на первый вход элемента ЗИ-НЕ 11 и, ввиду присутствия на его втором и третьем входах уровней 1, приводит к появлению уровня О на его выходе.

Уровень 1 на втором входе элемента ЗИ-НЕ 11 является результатом инвертирования элементом НЕ 12 уровня О, поступающего во время первого такта на его вход со второго выхода сдвигового регистра 19.

На третий вход элемента ЗИ-НЕ 11 уровень 1 поступает с инверсного выхода триггера 21.

Уровень 1 с первого выхода сдвигового регистра 10 одновременно пос- 20 2И-МЛИ-НЕ 13 через второй выход блока тупает на третий вход элемента 2И- ИПИ-НЕ 16, на четвертом входе которого присутствует уровень О, поступающий с прямого выхода триггера 21.

6 управления поступает на вход считывания накопителя 2 и разрешает выборку информации по адресу, код которого присутствует на адресных входах нако30

Присутствие на четвертом входе уров- 25 пителя 2 информации, ня О препятствует изменению состояния выхода элемента 2И-ИЛИ-НЕ 16. Уровень О с выхода элемента ЗИ-НЕ 11 через первый выход блока 6 управления поступает на вход записи регистра 1 адреса и производит запись в него кода адреса, поступившего на его информационные входы.

Записанный в регистр 1 адреса новый код адреса поступает на адресные входы накопителя 2 информации, и на вторую группу входов блока 5 сравнения. Ввиду наличия на входах блока 5 сравнения одинаковых кодов адреса, на ее выходе появляется уровень 1, который через управляющий вход блока 6 управления поступает на информационный вход триггера 21 и не приводит к изменению выходов его, так как процесс записи происходит только в момент включения триггера 7.

Во время третьего ся на третьем выходе стра 10 уровень 1 п первый вход элемента и ввиду наличия на ег уровня 1, поступающ элемента НЕ 18, приво уровня О на выходе НЕ 14.

Уровень О с выхо 2И-ИЛИ-НЕ 14 через тр 6 управления поступае чи данных накопителя выдачу выбранной инфо поступает на информац регистра 3 данных.

Во время четвертог шийся на четвертом вы регистра 10 уровень 45 первый вход элемента втором входе которого уровень 1, поступаю элемента НЕ 18, и при нию уровня О на вых

35

40

Во время второго такта появившийся на втором выходе сдвигового региВо время четвертого такта появившийся на четвертом выходе сдвигового регистра 10 уровень 1 поступает на 45 первый вход элемента 2И-ИЛИ-НЕ 15, на втором входе которого присутствует уровень 1, поступающий с выхода элемента НЕ 18, и приводит к появлению уровня О на выходе элемента

стра 10 уровень 1 поступает на вход50 2И-ИЛИ-НЕ 15. Уровень О с выхода элемента НЕ 12 и приводит к появле- элемента 2И-ИЛИ-НЕ 15 через четвертый нию его на выходе уровня О, который выход блока 6 управления поступает на

поступая на второй вход элемента ЗИ-НЕ 11, приводит к появлению на его выходе уровня О, что приводит к явлению уровня.1 на первом выходе блока 6 управления. Уровень 1 со второго выхода сдвигового регистра 10 поступает одновременно на первый вход

по-5

первого элемента 2И-ИЛИ-НЕ 13, на втором входе которого присутствует уровень 1, и приводит к появлению уровня О на его выходе. Уровень 1

на втором входе элемента И-ИЛИ-НЕ 23 присутствует, так как уровень О, поступающий во время второго, третьего и четвертого тактов с пятого выхода сдвигового регистра 10, инвертируется элементом НЕ 18.

Уровень 1 со второго выхода сдвигового регистра 10, поступая одновременно на третий вход элемента 2-И-ИЛИ-НЕ 17, не приводит к изменению состояние его выхода, так как на четвертом входе его присутствует уровень О, поступающий с прямого выхода триггера 21.

Уровень О с выхода элемента

2И-МЛИ-НЕ 13 через второй выход блока

6 управления поступает на вход считывания накопителя 2 и разрешает выборку информации по адресу, код которого присутствует на адресных входах нако

пителя 2 информации,

Во время третьего такта появившийся на третьем выходе сдвигового регистра 10 уровень 1 поступает на первый вход элемента 2И-ИЛИ-НЕ 14, и ввиду наличия на его втором входе уровня 1, поступающего с выхода элемента НЕ 18, приводит к появлению уровня О на выходе элемента 2И-ИЛИ- НЕ 14.

Уровень О с выхода элемента 2И-ИЛИ-НЕ 14 через третий выход блока 6 управления поступает на вход выдачи данных накопителя 2 и разрешает выдачу выбранной информации, которая поступает на информационные входы регистра 3 данных.

Во время четвертого такта появившийся на четвертом выходе сдвигового регистра 10 уровень 1 поступает на первый вход элемента 2И-ИЛИ-НЕ 15, на втором входе которого присутствует уровень 1, поступающий с выхода элемента НЕ 18, и приводит к появлению уровня О на выходе элемента

2И-ИЛИ-НЕ 15. Уровень О с выхода элемента 2И-ИЛИ-НЕ 15 через четвертый выход блока 6 управления поступает на

вход записи регистра 3 данных и своим фронтом производит запись в него ин- формации, которая присутствовала на его информационных входах.

Записанная информация с выходов регистра 3 поступает на информацио- ные входы регистра 4 данных.

Во время пятого такта аоязившийся на пятом выходе сдвигового регистра 10 уровень 1 поступает па вход элемента НЕ 18 и приводит к лоязлению на его выходе уровня О, который, поступая на вторые входы элементов 14-15, приводит к появлению на их выходах уровней I, что соответствует окончанию режимов выборки и выдачи информации в накопителе 2 и подготовки входа записи рг;- гнстра 3 sc повторной записи.

Уровень 1 с пятого выхода сдвигового регистра 10 опновременко поступает на первый вход, эле.ч ев та 2И- 16 и, j -ак к а. к на его втором входе присутствует утювень 1 ;Посту пающий с инверсног о вьлхода триггера 21. приводит к появлению уровнл О на выходе элемента 2И/-ИЛИ-НЕ 16, Уро вень 1 с пятого выхода сдвигового регистра 10 одновременно пост-упает на третий вход элемента 2И -ИЛИ НЕ 19 и, так как на его четвертом входе присутствует уровень 0 поступающий с прямого триггера 21jHe приводит к изменению состояния выход элемента 2И-ИЛИ-ИЕ 19, Уровень О с выхода элег-,ента 2l- i-);li)H-НЬ 16 чевез пятый выход блока 6 управленгш поступает на вход записи регистра 4 и

своим фронтом Vlpo ЗBOДИT заПКСь в

него данных, ирису ствуюип-тх ча его информационных входах.. Информация с выходов регистра 4 поступает ка вьг-- ход устройства, Уровень О с выхода

элемента 2И-ИЛИНЕ 16 одповременно

поступает на счетный вход регистра 1 адреса и своим фронтом увеличивает состояние его пя единицу Вновь сформиро1:;аниый код адреса с выходов регистра 1 адреса поступает на ад- pGCsibie входь накопителя 2 ИНШОРМЗ- ,ции.

Вез время шестого такта ПОЯВИБШИЙ™ ся на шестом выкоде :1д1;игово1 о регистра 10 уровень г пост; пает иа первый вход элемента 2И--ШГИ- НЕ 1/ li, так как па его втором входе ярисут™ стоует уровень Г% поступаютий с инверсного выхода Григгега 21 ,, приводит к появле1- :и1; на его выходе уровня который через гаасток выход бгго- ка 6 управления постулае г- на вь ход готовности данных ус- -ройства и тем самы подтверждает наличие на выхода сч1-гганной информации. Уровень 1 с iiiecToro .оца. сдвчготз тго регистра

10 одновременно поступает ia третий и четвертый входы элемента 2И ИЛИ-НЕ 13 и приводит к появлению на его выходе уровня О,, который повторно через второй выход блока 6 управления поступает на вход считывания первого накопителя 2 и разрешает выборку новой информапРП-Тд код адреса которой отличается HS. единицу от кода адреса ранее выбранной информиции,

Во время седьмого такта появившийся ,на седьмом вьп оде сдвигового регистра 10 уровенЕ 1 поступает на третий и четвертый входы элемента 2И-ИЛИ-НЕ 14 и пГ Иводит к появлению па его выходе уровня О, который повторно через блока 6 зтравления поступает на вход выдачи ДЕННЫХ накопителя 2 и производит выдачу выбранной информации, которая ;поступает HS инфсфмационные входы

Fs

Во время Bocbbioro такта появившийся на восьмом вь&;оде сдвигового регистра 10 уровень Г поступает на третий и четвертый входы элемента 2И- ,11ПИ-БЕ 15 и приводит к появлению на его выходе уровн,я О . который повторно черв четв-С1ртый в(, Код. блока 6 управления постуггает ка вхрд записи рег1-;стра 3 и производи ; запись вновь поступив1 е:й и;шю рма1;,1«и,

Во время девях ого такта ио51вивший- ся на девятом вьп:оде сдвигового ре Г

поступает на

первый вход

вует уровень 1 ., пос упившии с инверсного выхода триггера 21, и при- водЗ Гг к появлении па его- вьгходе уровня О 5 который,; поступая ка сбрасы- вход TpHi j Cpa 7„ приводит его 3 выключенное сос ояние.

V

.;р о-ве HI;

элемента 2Pi-

ИЛИ--НЕ 19 одноврс менпс поступает на сбра.сывающий БХОД триггепа 20- и, если он ранее бы-л ш-лючен, переводит его в 3HKj iC4eHHot; состоя :ие. Триггер 20 находится во 1п--гл1оче:нном состоянии тсхпько при зк.пючкглтк питания ПЗУ за сггет заряда конденсатора 23 через резистор 22. noc.i.te обращения к ПЗУ TpHiTep 20 при поступлении на его сбрасывающий вход,-уровня О переводится в выкльэченкое состояние и находится в нем в течение всего времени работь устройства,- При этом ypoBestb 1 с ег о инверсного выхода

поступая на сбрасывающий вход триггера 21; разрешает запись в него информации., присутствующей на информационном входе. Использование триггера 20 исключает выдачу неверной информации при первом обращении к ПЗУ, в случае если поступивший код адреса совпадает с произвольным кодом, который установился в регистре 1 адреса

после включения питания и по которомуШ рого присутствует уровень 1, посту-., отсутствовала выборка информации из пивший с прямого выхода триггера 21,

О

накопителя 2.

Переход трр ггера 7 в выключенное состояние соответствует запрещению

и приводит к появлению уровня на выходе элемента 2И-ИЛИ-НЕ 16, Уровень О с выхода элемента

работы управляемого генератора 9 так-15 2И-1-ШИ-НЕ 16 через пятый выход блока

6 управления поступает на вход записи регистра 4 и своим фронтом производит запись в него информации, ранее выбранной из накопителя 2 и записанной

20 в регистр 3 информации. Информация с выходов регистра 4 информации поступает на выходы устройства.

Уровень О с выхода элемента 2И-ИЛИ-НЕ 16 одновременно поступает

25 на счетный вход регистра 1 и своим ;, фронтом производит увеличение состояния на его единицу. Вновь сформированный код адреса с выходом регистра 1 адреса поступает на адресные входы накопителя 2.

товых импульсов, сбросу сдвигового регистра 10, на выходах которого появятся уровни О, т.е. все элементы блока 6 управления установятся в исходное состояние, при котором возможен прием следующего сигнала обращения .

При последующих обращениях к ЗУ в случае . несовпадения поступившего кода адреса с кодом адреса, хранимом регистром 1 адреса, ПЗУ работает вьпиеописанным образом.

Рассмотрим работу ЗУ во втором режиме с уменьшенным временем выборки.

Отличительной особенностью данного режима работы является совпадение поступившего код адреса с кодом ад-, реса, хранимым регистром 1 адреса, при этом на выходе блока 5 сравнения и соответственно на информационном выходе триггера 21 присутствует уровень 1.

При данном режиме первоначальная работа блока 6 управления отличается от описанного ранее режима только в том, что в триггер 21 записывается присутствуюшд1й на его информационном входе уровень 1, т.е. на прямом выходе триггера 1 сравнения появляется уровень , а на инверсном выходе - уровень О. А последующая работа отличается тем, что уровни О на выходах блока 6 управления появляются в другой последовательности, и тем, что работа ЗУ заканчивается в начале пятого такта,

Во время первого такта появившийся на первом выходе сдвигового регистра 10 уровень 1, поступая на первый вход элемента ЗИ-КЕ 11, на третьем входе которого присутствует уровень поступающий с инверсного выхода

30

О

Во время второго такта появившийся на втором выходе сдвигового регистра 10 уровень 1 поступает на третий

35 вход элемента 2И-1-ШИ-НЕ 17, на четвертом входе которого присутствует уровень 1, поступивший с прямого выхода триггера 21, и приводит к появлению на его выходе уровня О, торый через шестой выход блока 6 управления поступает на выход готовности данных устройства и тем самым подтверждает наличие данных. Уровень 1 с шестого выхода сдвигового ре гистра 10 одновременно поступает на первый вход элемента 2И-ИЛИ-НЕ 13 и, так как на его втором входе присутствует уровень 1, приводит к появлению уровня О на его выходе. Уровень 1 на втором входе элемента 2И-ИЛИ-НЕ 13 присутствует ввиду инверсии элементом НЕ 18 уровня О, поступившего с пятого выхода сдвигового регистра 10, Уровень О с выхо да первого элемента 2И-1-ШИ-НЕ 13 через второй вьп од блока 6 управления посту1тае,т на вход считывания вход накопителя 2 к разрешает выборку ин- . формации по адресу5 код соторого при

50

триггера

не приводит к изменению

состояния его выхода. Этим обеспечивается отсутствие режима записи в регистр 1 адреса поступившего кода адреса ввиду равенства его с ранее хранимым кодом адреса.

Уровень 1 с первого выхода сдвигового регистра 10 одновременно поступает на третий вход элемента 2И- ИЛИ-НЕ 16, на четвертом входе кото О

и приводит к появлению уровня на выходе элемента 2И-ИЛИ-НЕ 16, Уровень О с выхода элемента

25

30

Во время второго такта появившийся на втором выходе сдвигового регистра 10 уровень 1 поступает на третий

вход элемента 2И-1-ШИ-НЕ 17, на четвертом входе которого присутствует уровень 1, поступивший с прямого выхода триггера 21, и приводит к появлению на его выходе уровня О, который через шестой выход блока 6 управления поступает на выход готовности данных устройства и тем самым подтверждает наличие данных. Уровень 1 с шестого выхода сдвигового регистра 10 одновременно поступает на первый вход элемента 2И-ИЛИ-НЕ 13 и, так как на его втором входе присутствует уровень 1, приводит к появлению уровня О на его выходе. Уровень 1 на втором входе элемента 2И-ИЛИ-НЕ 13 присутствует ввиду инверсии элементом НЕ 18 уровня О, поступившего с пятого выхода сдвигового регистра 10, Уровень О с выхода первого элемента 2И-1-ШИ-НЕ 13 чеез второй вьп од блока 6 управления посту1тае,т на вход считывания вход накопителя 2 к разрешает выборку ин- ормации по адресу5 код соторого при

913

сутствует на адресных входах накопителя 2,

Работа ПЗУ во время третьего и четвертого тактов аналогична работе во время данных тактов при первом режиме.

Во время пятого такта появившийся на пятом выходе сдвигового регистра 10 уровень 1 поступает на третий вход элемента 2И-ИЛИ-НЕ 19, на четвертом входе которого присутствует уровень 1, поступивший с прямого вько- да триггера приводит к появлению на его выходе уровня который, поступая на сбрасывающий аход триггера 7, переводит в выключенное состояние, чем и обеспечивается перевод элементов блока 6 управления в исход- и f состояние, при котором, возможен прием следующего сигнала обращения.

После последующих обращениях к ПЗУ в зависимости от результатов сравнения указанкьж кодов блок 6 управления автоматически выбирает требуемый режим работы ПЗУ.

Ф о р м 3 л а изобретения

Постоянное запоминающее з стройст- во, содержащее постоянный накопитель выходы и адресный входы которого под810

клгочены соответственно к информационным входам первого регистра данных, и к выходам регистра адреса, входы которого являются адресными входами

устройства, блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к входу записи регистра адреса, входам считывания и вьздачи данных постоянного накопителя и к входу записи первого регистра данньсх, вход готовности блока управления является входом

обращения устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок сравнения и второй регистр данных, информационные входы которого подключены к выходам первого регистра данных, выходы второго

регистра данных являются информационными выходами устройства, входы пер- .вой и второй групп блока сравнения подключены соответственно к входам и выходам регистра адреса, выход блока сравнения подключен к входу задания режима блока управления, пятый выход которого подключен к входу изменения состояния регистра адреса и входу записи второго регистра данных,

шестой выход блока управления является выходом готовности данных устройства

10

ii

fPu2.2

ие.З

Редактор Г. Волкова

Составитель С, Шустенко

Техред Л.Олийнык Корректор А. Тяско

Заказ 3698/46 Тираж 588Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1130355 Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, п Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1317484A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1495855A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для проверки исправности многопроводных кабелей | 1987 |

|

SU1638673A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1140180A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующей постоянной памяти вычислительных машин. Цель изобретения - повышение быстродействия постоянного запоминающего устройства (ПЗУ), Устройство содержит регистр 1 адреса с возможно - стью инкремента своего состояния, постоянный накопитель 2, регистры данных 3 и 4, блоки сравнения 5 и управления 6. ПЗУ может работать в режиме, при котором время выборки информации практически не отличается от времени выборки известных ПЗУ, а также в режиме с уменьшенным временем выборки. 3 ил. Ьэ ifcri ф5

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Полупроводниковые запоминающие устройства и их применение, /Под ред | |||

| А.Ю | |||

| Гордонова | |||

| М.: Радио и связь, 1981, с | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| рис | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-11-23—Публикация

1986-07-14—Подача