Изобретение относится к запоминающим устройствам и может быть использовано в качестве цифровой задержки для перестановки отсчетов последовательности сигналов.

Целью изобретения .является упрощение устройства.

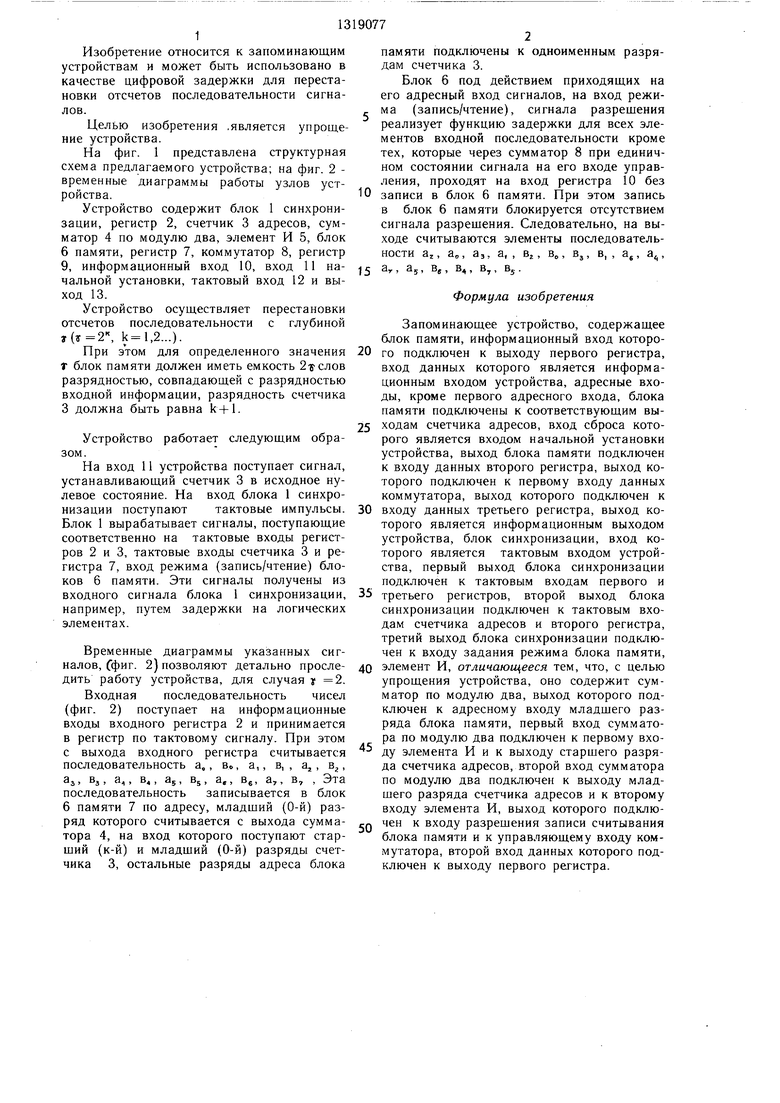

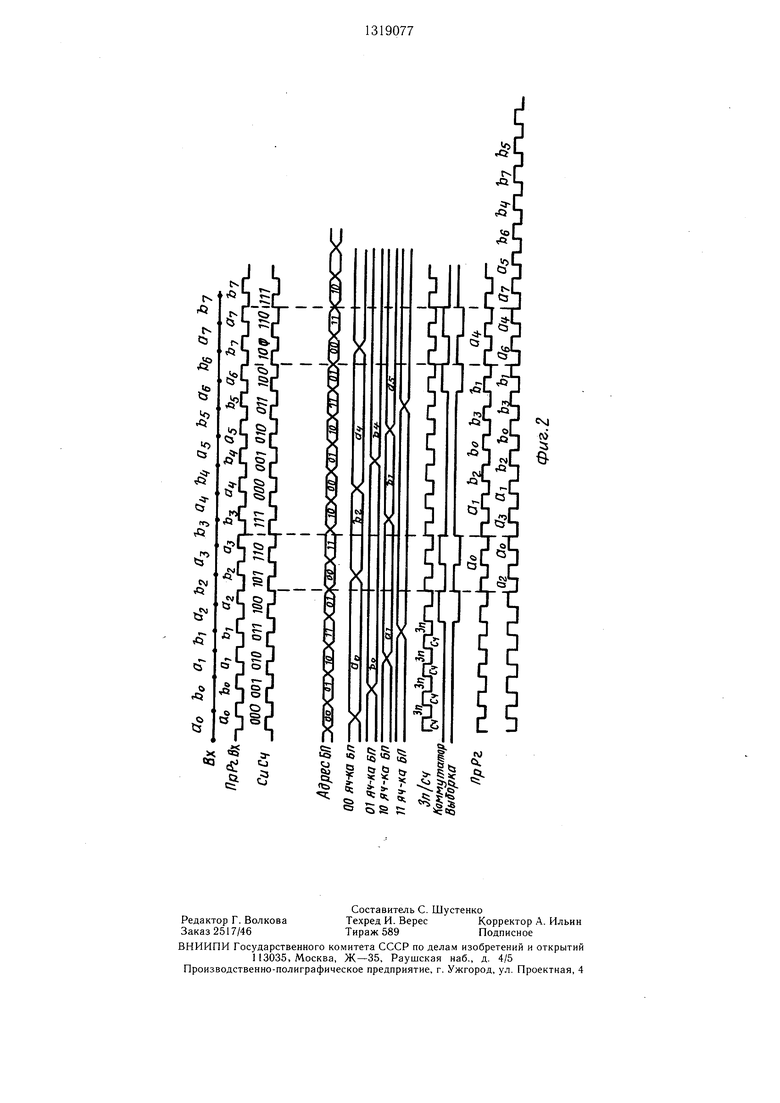

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы узлов устройства.

Устройство содержит блок 1 синхронизации, регистр 2, счетчик 3 адресов, сумматор 4 по модулю два, элемент И 5, блок 6 памяти, регистр 7, коммутатор 8, регистр 9, информационный вход 10, вход 11 начальной установки, тактовый вход 12 и выход 13.

Устройство осуществляет перестановки отсчетов последовательности с глубиной ,(, ,2...).

При этом для определенного значения Т блок памяти должен иметь емкость 2т слов разрядностью, совпадающей с разрядностью входной информации, разрядность счетчика 3 должна быть равна k+1.

Устройство работает следующим образом.

На вход 11 устройства поступает сигнал, устанавливающий счетчик 3 в исходное нулевое состояние. На вход блока 1 синхронизации поступают тактовые импульсы. Блок 1 вырабатывает сигналы, поступающие соответственно на тактовые входы регистров 2 и 3, тактовые входы счетчика 3 и регистра 7, вход режима (запись/чтение) блоков 6 памяти. Эти сигналы получены из входного сигнала блока 1 синхронизации, например, путем задержки на логических элементах.

Временные диаграммы указанных сигналов, (фиг. 2) позволяют детально проследить работу устройства, для случая у 2.

Входная последовательность чисел (фиг. 2) поступает на информационные входы входного регистра 2 и принимается в регистр по тактовому сигналу. При этом с выхода входного регистра считывается последовательность а,, Во, а,, в,, а, в, aj, Bj, а,, в,, as, в, а,, Sg, а,, в, , Эта последовательность записывается в блок 6 памяти 7 по адресу, младший (0-й) разряд которого считывается с выхода сумматора 4, на вход которого поступают старший (к-й) и младший (0-й) разряды счетчика 3, остальные разряды адреса блока

памяти подключены к одноименным разрядам счетчика 3.

Блок 6 под действием приходящих на его адресный вход сигналов, на вход режима (запись/чтение), сигнала разрещения реализует функцию задержки для всех элементов входной последовательности кроме тех, которые через сумматор 8 при единичном состоянии сигнала на его входе управления, проходят на вход регистра 10 без записи в блок 6 памяти. При этом запись в блок 6 памяти блокируется отсутствием сигнала разрешения. Следовательно, на выходе считываются элементы последователь

ности аг, Зг I а 5, Bj

а,, , в.

а, , , в

в,, в„

в, , а.

Формула изобретения

0

Запоминающее устройство, содержащее блок памяти, информационный вход которого подключен к выходу первого регистра, вход данных которого является информационным входом устройства, адресные входы, кроме первого адресного входа, блока памяти подключены к соответствующим вы5 ходам счетчика адресов, вход сброса которого является входом начальной установки устройства, выход блока памяти подключен к входу данных второго регистра, выход которого подключен к первому входу данных коммутатора, выход которого подключен к

0 входу данных третьего регистра, выход которого является информационным выходом устройства, блок синхронизации, вход которого является тактовым входом устройства, первый выход блока синхронизации подключен к тактовым входам первого и

5 третьего регистров, второй выход блока синхронизации подключен к тактовым входам счетчика адресов и второго регистра, третий выход блока синхронизации подключен к входу задания режима блока памяти,

0 элемент И, отличающееся тем, что, с целью упрощения устройства, оно содержит сумматор по модулю два, выход которого подключен к адресному входу младщего разряда блока памяти, первый вход сумматора по модулю два подключен к первому вхо ду элемента И и к выходу старшего разряда счетчика адресов, второй вход сумматора по модулю два подключен к выходу младщего разряда счетчика адресов и к второму входу элемента И, выход которого подклюg чен к входу разрешения записи считывания блока памяти и к управляющему входу коммутатора, второй вход данных которого подключен к выходу первого регистра.

N|

A

Ь51

C5

5

S,

o

S|

«T 1

§1

ca

t.

О

О

Л

§i

l§

С

«g

jjJ C

Э- Co

d

СЧ4 W

:5 Q

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для сопряжения абонентов с ЦВМ | 1985 |

|

SU1278863A1 |

| Блок буферной памяти для терминального устройства | 1987 |

|

SU1418812A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано для организации задержки и перестановки данных. Цель изобретения - упрощение устройства. Устройство содержит блок 1 синхронизации, регистр 2, счетчик 3 адресов, сумматор 4 по модулю два, элемент И 5, блок 6 памяти, регистр 7, коммутатор 8, регистр 9, информационный вход 10, вход 11 начальной установки, тактовый вход 12 и выход 13. При поступлении последовательности данных на вход 10 они записываются в регистр 2, а затем в блок 6 по адресам старщих разрядов которых формируются соответствующие разряды счетчика 3. Младший разряд адреса равен сумме по модулю два значений старшего и младшего разрядов счетчика 3 (формируется сумматором 4). В соответствии с временной диаграммой импульсов, формируемых блоком 1, осуществляется считывание данных из блока 6 в регистр 7. Коммутатор 8 в соответствии с управляющим сигналом, формируемым на выходе элемента 5, на вход которого поступают значения старшего и инверсного младшего разряда счетчика 3, пропускает данные либо с выхода регистра 2, либо с выхода регистра 7. На выходе-регистра 7, в который записываются данные с выхода коммутатора 8, формируется задержанная последовательность переставленных соответствующим образом данных. 2 ил. (О (Л 0 со г о Фиг.1

| ЭУПВ для формирования длинных задержек | |||

| Электроника, 1985, № 7, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Запоминающее устройство | 1984 |

|

SU1233212A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-31—Подача