Изобретение относится к вычислительной технике и может быть применено при разработке запоминающих устройств для упорядоченного хранения и выдачи информации.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения режимов выборочного считывания.

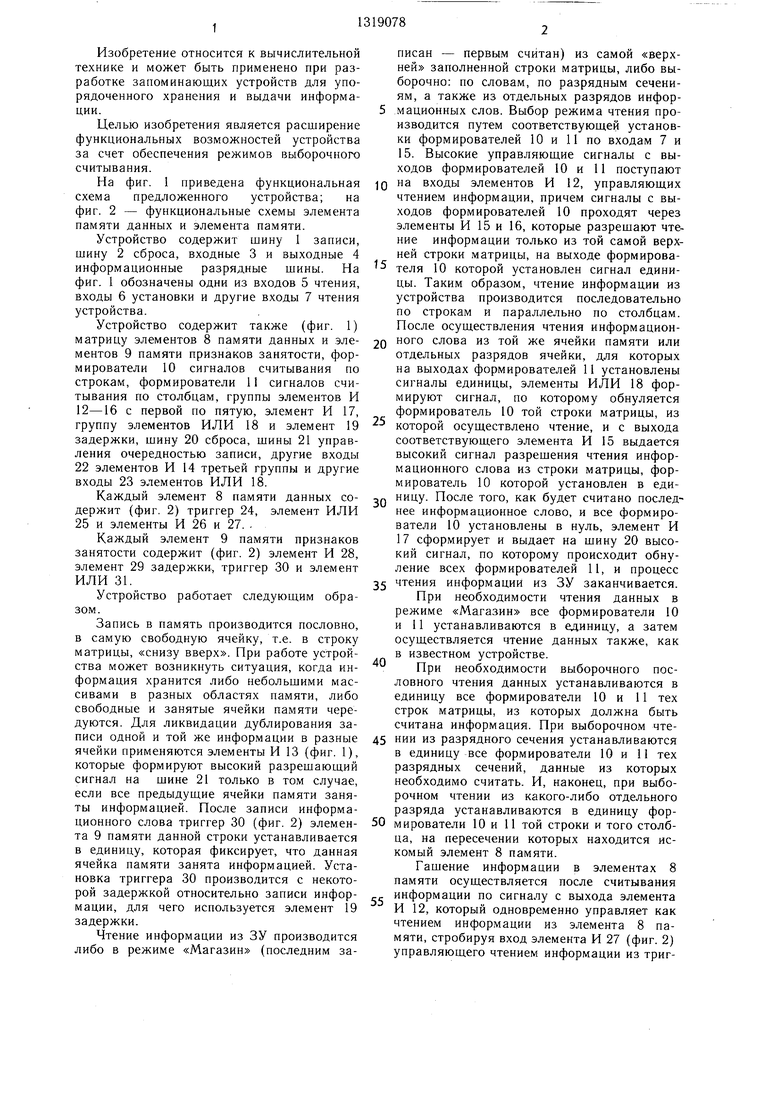

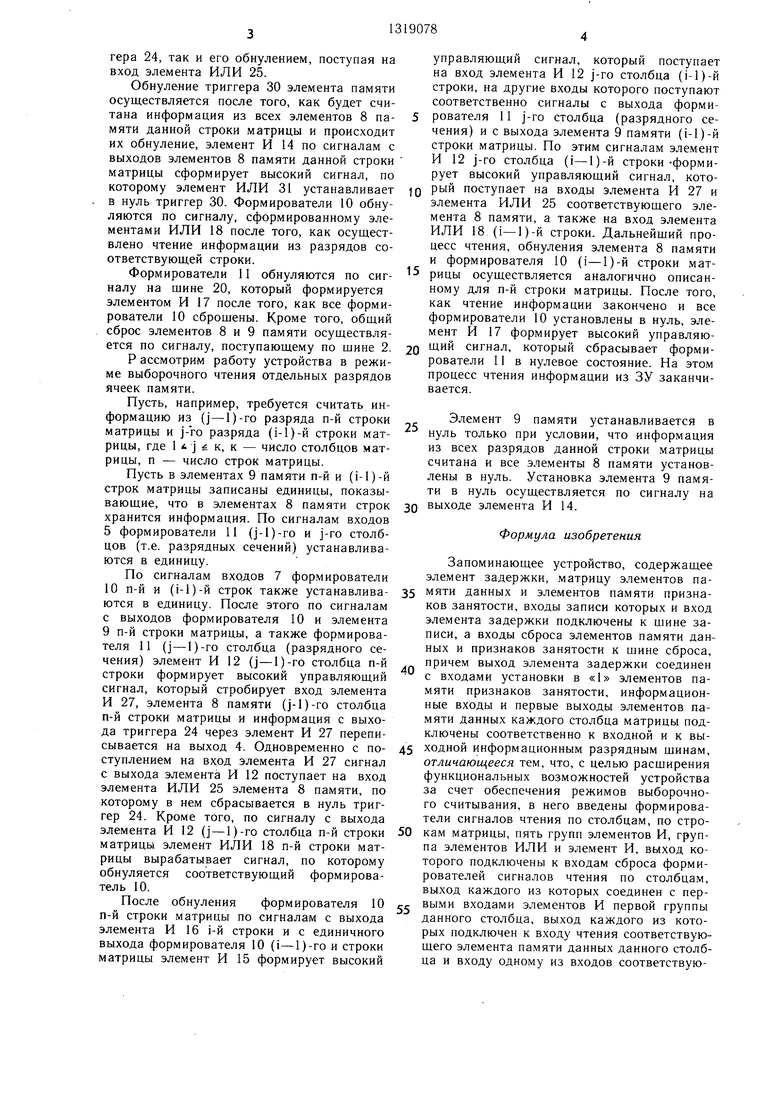

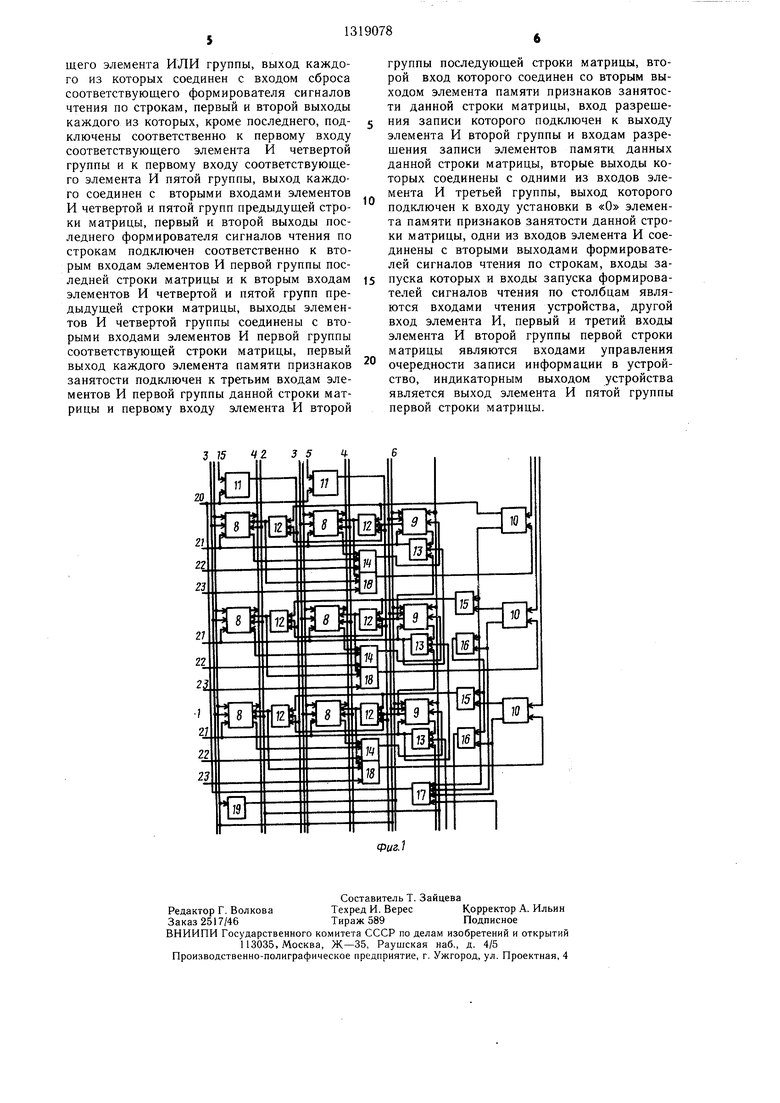

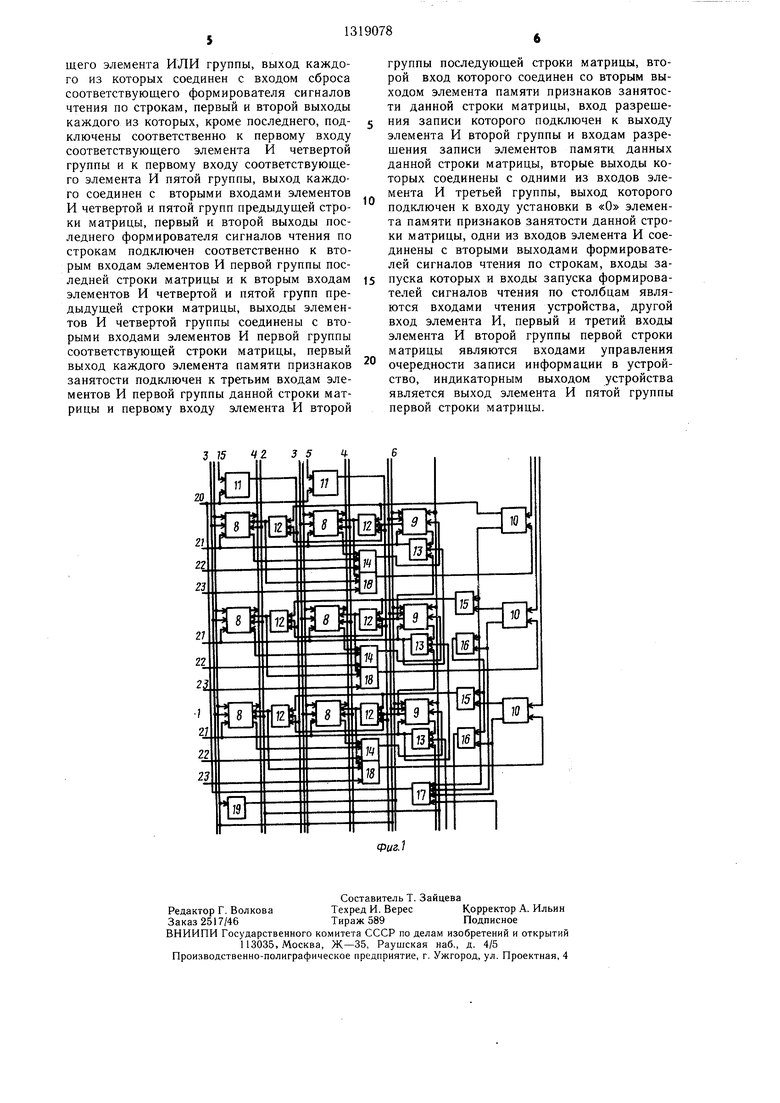

На фиг. i приведена функциональная схема предложенного устройства; на фиг. 2 - функциональные схемы элемента памяти данных и элемента памяти.

Устройство содержит шину 1 записи, шину 2 сброса, входные 3 и выходные 4 информационные разрядные шины. На фиг. 1 обозначены одни из входов 5 чтения, входы 6 установки и другие входы 7 чтения устройства.

Устройство содержит также (фиг. 1) матрицу элементов 8 памяти данных и элементов 9 памяти признаков занятости, формирователи 10 сигналов считывания по строкам, формирователи 11 сигналов считывания по столбцам, группы элементов И 12-16 с первой по пятую, элемент И 17, группу элементов ИЛИ 18 и элемент 19 задержки, шину 20 сброса, шины 21 управления очередностью записи, другие входы 22 элементов И 14 третьей группы и другие входы 23 элементов ИЛИ 18.

Каждый элемент 8 памяти данных содержит (фиг. 2) триггер 24, элемент ИЛИ 25 и элементы И 26 и 27. .

Каждый элемент 9 памяти признаков занятости содержит (фиг. 2) элемент И 28, элемент 29 задержки, триггер 30 и элемент ИЛИ 31.

Устройство работает следующим образом.

Запись в память производится пословно, в самую свободную ячейку, т.е. в строку матрицы, «снизу вверх. При работе устройства может возникнуть ситуация, когда информация хранится либо небольшими массивами в разных областях памяти, либо свободные и занятые ячейки памяти чередуются. Для ликвидации дублирования записи одной и той же информации в разные ячейки применяются элементы И 13 (фиг. 1), которые формируют высокий разрешающий сигнал на шине 21 только в том случае, если все предыдущие ячейки памяти заняты информацией. После записи информационного слова триггер 30 (фиг. 2) элемента 9 памяти данной строки устанавливается в единицу, которая фиксирует, что данная ячейка памяти занята информацией. Установка триггера 30 производится с некоторой задержкой относительно записи информации, для чего используется элемент 19 задержки.

Чтение информации из ЗУ производится либо в режиме «Магазин (последним записан - первым считан) из самой «верхней заполненной строки матрицы, либо выборочно: по словам, по разрядным сечениям, а также из отдельных разрядов информационных слов. Выбор режима чтения производится путем соответствующей установки формирователей 10 и 11 по входам 7 и 15. Высокие управляющие сигналы с выходов формирователей 10 и 11 поступают

Q на входы элементов И 12, управляющих чтением информации, причем сигналы с выходов формирователей 10 проходят через элементы И 15 и 16, которые разрешают чтение информации только из той самой верхней строки матрицы, на выходе формирова теля 10 которой установлен сигнал единицы. Таким образом, чтение информации из устройства производится последовательно по строкам и параллельно по столбцам. После осуществления чтения информацион0

5

ного слова из той же ячейки памяти или отдельных разрядов ячейки, для которых на выходах формирователей 11 установлены сигналы единицы, элементы ИЛИ 18 формируют сигнал, по которому обнуляется формирователь 10 той строки матрицы, из

0

которой осуществлено чтение, и с выхода соответствующего элемента И 15 выдается высокий сигнал разрещения чтения информационного слова из строки матрицы, формирователь 10 которой установлен в еди„ ницу. После того, как будет считано последнее информационное слово, и все формирователи 10 установлены в нуль, элемент И 17 сформирует и выдает на шину 20 высокий сигнал, по которому происходит обнуление всех формирователей 11, и процесс

5 чтения информации из ЗУ заканчивается. При необходимости чтения данных в режиме «Магазин все формирователи 10 и 11 устанавливаются в единицу, а затем осуществляется чтение данных также, как в известном устройстве.

При необходимости выборочного пословного чтения данных устанавливаются в единицу все формирователи 10 и 11 тех строк матрицы, из которых должна быть считана информация. При выборочном чте5 НИИ из разрядного сечения устанавливаются в единицу все формирователи 10 и 11 тех разрядных сечений, данные из которых необходимо считать. И, наконец, при выборочном чтении из какого-либо отдельного разряда устанавливаются в единицу фор0 мирователи 10 и 11 той строки и того столбца, на пересечении которых находится искомый элемент 8 памяти.

Гашение информации в элементах 8 памяти осуществляется после считывания

г информации по сигналу с выхода элемента И 12, который одновременно управляет как чтением информации из элемента 8 памяти, стробируя вход элемента И 27 (фиг. 2) управляющего чтением информации из триггера 24, так и его обнулением, поступая на вход элемента ИЛИ 25.

Обнуление триггера 30 элемента памяти осуществляется после того, как будет считана информация из всех элементов 8 памяти данной строки матрицы и происходит их обнуление, элемент И 14 по сигналам с выходов элементов 8 памяти данной строки матрицы сформирует высокий сигнал, по которому элемент ИЛИ 31 устанавливает в нуль триггер 30. Формирователи 10 обнуляются по сигналу, сформированному элементами ИЛИ 18 после того, как осуществлено чтение информации из разрядов соответствующей строки.

Формирователи 11 обнуляются по сигналу на щине 20, который формируется элементом И 17 после того, как все формирователи 10 сброщены. Кроме того, общий сброс элементов 8 и 9 памяти осуществляется по сигналу, поступающему по шине 2.

Р ассмотрим работу устройства в режиме выборочного чтения отдельных разрядов ячеек памяти.

Пусть, например, требуется считать информацию из (J-1)-го разряда п-й строки матрицы и j-Vo разряда (1-1)-й строки матрицы, где 1 1 j к, к - число столбцов матрицы, п - число строк матрицы.

Пусть в элементах 9 памяти п-й и (-1)-й строк матрицы записаны единицы, показывающие, что в элементах 8 памяти строк хранится информация. По сигналам входов 5 формирователи И (j-l)-ro и j-ro столбцов (т.е. разрядных сечений) устанавливаются а единицу.

По сигналам входов 7 формирователи 10 п-й и (-1)-й строк также устанавливаются в единицу. После этого по сигналам с выходов формирователя 10 и элемента 9 п-й строки матрицы, а также формирователя И (J-1)-го столбца (разрядного сечения) элемент И 12 (j-1)-го столбца п-й строки формирует высокий управляющий сигнал, который стробирует вход элемента И 27, элемента 8 памяти (j-l)-ro столбца п-й строки матрицы и информация с выхода триггера 24 через элемент И 27 переписывается на выход 4. Одновременно с поступлением на вх;од элемента И 27 сигнал с выхода элемента И 12 поступает на вход элемента ИЛИ 25 элемента 8 памяти, по которому в нем сбрасывается в нуль триггер 24. Кроме того, по сигналу с выхода элемента И 12 (j-1)-го столбца п-й строки матрицы элемент ИЛИ 18 п-й строки матрицы вырабатывает сигнал, по которому обнуляется соответствующий формирователь 10.

После обнуления формирователя 10 п-й строки матрицы по сигналам с выхода элемента И 16 i-й строки и с единичного выхода формирователя 10 (i-1)-го и строки матрицы элемент И 15 формирует высокий

управляющий сигнал, который поступает на вход элемента И 12 j-ro столбца (1-1)-й строки, на другие входы которого поступают соответственно сигналы с выхода форми5 рователя 11 j-ro столбца (разрядного сечения) и с выхода элемента 9 памяти (1-1)-й строки матрицы. По этим сигналам элемент И 12 j-ro столбца (i-1)-й строки-формирует высокий управляющий сигнал, котоQ рый поступает на входы элемента И 27 и элемента ИЛИ 25 соответствующего элемента 8 памяти, а также на вход элемента ИЛИ 18 (i-1)-й строки. Дальнейщий процесс чтения, обнуления элемента 8 памяти и формирователя 10 (i-1)-й строки мат5 рицы осуществляется аналогично описанному для п-й строки матрицы. После того, как чтение информации закончено и все формирователи 10 установлены в нуль, элемент И 17 формирует высокий управляю0 щий сигнал, который сбрасывает формирователи 11 в нулевое состояние. На этом процесс чтения информации из ЗУ заканчивается.

Элемент 9 памяти устанавливается в нуль только при условии, что информация из всех разрядов данной строки матрицы считана и все элементы 8 памяти установлены в нуль. Установка элемента 9 памяти в нуль осуществляется по сигналу на 0 выходе элемента И 14.

Формула изобретения

Запоминающее устройство, содержащее элемент задержки, матрицу элементов па5 мяти данных и элементов памяти признаков занятости, входы записи которых и вход элемента задержки подключены к щине записи, а входы сброса элементов памяти данных и признаков занятости к щине сброса, причем выход элемента задержки соединен с входами установки в «1 элементов памяти признаков занятости, информационные входы и первые выходы элементов памяти данных каждого столбца матрицы подключены соответственно к входной и к вы5 ходной информационным разрядным шинам, отличающееся тем, что, с целью расщирения функциональных возможностей устройства за счет обеспечения режимов выборочного считывания, в него введены формирователи сигналов чтения по столбцам, по стро0 кам матрицы, пять групп элементов И, группа элементов ИЛИ и элемент И, выход которого подключены к входам сброса формирователей сигналов чтения по столбцам, выход каждого из которых соединен с перг выми входами элементов И первой группы данного столбца, выход каждого из которых подключен к входу чтения соответствующего элемента памяти данных данного столбца и входу одному из входов соответствую0

щего элемента ИЛИ группы, выход каждого из которых соединен с входом сброса соответствующего формирователя сигналов чтения по строкам, первый и второй выходы каждого из которых, кроме последнего, подключены соответственно к первому входу соответствующего элемента И четвертой группы и к первому входу соответствующего элемента И пятой группы, выход каждого соединен с вторыми входами элементов И четвертой и пятой групп предыдущей строки матрицы, первый и второй выходы последнего формирователя сигналов чтения по строкам подключен соответственно к вторым входам элементов И первой группы последней строки матрицы и к вторым входам элементов И четвертой и пятой групп предыдущей строки матрицы, выходы элементов И четвертой группы соединены с вторыми входами элементов И первой группы соответствующей строки матрицы, первый выход каждого элемента памяти признаков занятости подключен к третьим входам элементов И первой группы данной строки матрицы и первому входу элемента И второй

группы последующей строки матрицы, второй вход которого соединен со вторым выходом элемента памяти признаков занятости данной строки матрицы, вход разреще- ния записи которого подключен к выходу элемента И второй группы и входам разре- щения записи элементов памяти, данных данной строки матрицы, вторые выходы которых соединены с одними из входов элед мента И третьей группы, выход которого подключен к входу установки в «О элемента памяти признаков занятости данной строки матрицы, одни из входов элемента И соединены с вторыми выходами формирователей сигналов чтения по строкам, входы запуска которых и входы запуска формирователей сигналов чтения по столбцам являются входами чтения устройства, другой вход элемента И, первый и третий входы элемента И второй группы первой строки матрицы являются входами управления очередности записи информации в устройство, индикаторным выходом устройства является выход элемента И пятой группы первой строки матрицы.

3 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Ортогональная многопроцессорная система | 1990 |

|

SU1839261A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для формирования характеристических матриц | 1988 |

|

SU1596334A1 |

| Устройство для вывода информации | 1986 |

|

SU1377849A1 |

| Матричная вычислительная система | 1989 |

|

SU1608700A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

Изобретение относится к вычислительной технике и может быть применено при разработке запоминающих устройств для упорядоченного хранения и выдачи информации. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения режимов выборочного считывания. Устройство содержит матрицу элементов 8 памяти данных и элементов 9 памяти признаков заняот 13 тости, формирователи сигналов считывания по строкам, формирователи сигналов считывания по столбцам, пять групп элементов И, элемент И, группу элементов ИЛИ и элемент задержки. Каждый элемент 8 памяти данных содержит триггер 24, элемент ИЛИ 25 и элементы И 26 и 27. Каждый элемент 9 памяти признаков занятости содержит триггер 30, элемент И 28, элемент задержки 29 и элемент ИЛИ 31. Запись в устройство производится пословно, начиная с самой первой свободной ячейки памяти (т.е. строки матрицы). Элементы И исключают дублирование записи одной и той же информации в несколько разных ячеек памяти. Выборочное чтение из устройства возможно по словам (т.е. строкам матрицы), по отдельным разрядам (т.е. столбцам матрицы) и по разрядным сечениям. Установка в единицу триггера 30 свидетельствует о том, что в данной строке матрицы записана информация. 2 ил. отП в вА И Чт СО N4 СО 1 ос Фиг. 2

Составитель Т. Зайцева

Редактор Г. ВолковаТехред И. ВересКорректор А Ильин

Заказ 2517/46Тираж 589Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб д 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Стековое запоминающее устройство | 1979 |

|

SU881863A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Одноразрядное стековое запоминающее устройство | 1980 |

|

SU947911A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-28—Подача