Изобретение относится к технике связи и может быть использовано для организации каналов передачи дискретных сигналов по цифровым трактам.

Цель изобретения - повышение пропуск ной способности.

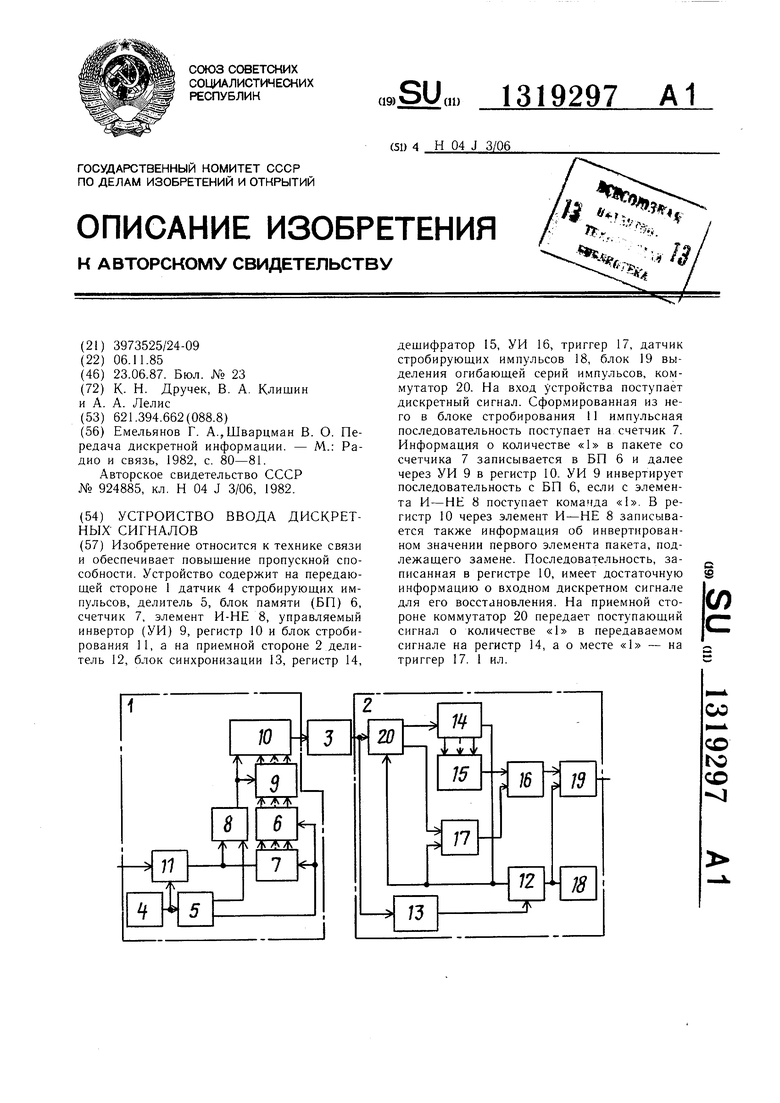

На чертеже приведена электрическая структурная схема устройства ввода дискретных сигналов.

Устройство ввода дискретных сигналов содержит передающую 1, приемную 2 стороны и цифровой тракт 3.

Передающая сторона 1 содержат первый датчик 4 стробирующих импульсов, первый делитель 5, блок 6 памяти, счетчик 7, элемент И-НЕ 8, первый управляемый инвертор 9, первый регистр 10 и блок 11 стро- бирования.

Приемная сторона 2 содержит второй делитель 12, блок 13 синхронизации , второй регистр 14, дешифратор 15, второй управляемый инвертор 16, триггер 17, второй датчик 18 стробирующих импульсов, блок 19 выделения огибающей серий импульсов и коммутатор 20.

Устройство ввода дискретных сигналов работает следующим образом.

На вход передающей стороны 1 поступает входной дискретный сигнал, а на вход блока 11 стробирования - последовательность стробирующих импульсов с первого датчика 4 стробирующих импульсов. Последовательность, образованная блоком 11 стробирования, поступает на вход счетчика 7. Информация через счетчик 7 поступает в блок 6 памяти по сигналу с первого делителя 5, на вход которого поступает стро- бирующая последовательность с первого датчика 4 стробирующих импульсов. Коэффициент деления первого делителя 5 устанавливает размеры пакета, на которые разбивается последовательность, образованная в блоке 11 стробирования. При этом счетчик 7 определяет количество «1 в каждом пакете и на выходе счетчика 7 формируется двоичное число, соответствующее числу «1, поступивших на него. Коэффициент деления определяется по формуле

К 2- - Um+1,

где X - коэффициент деления первого делителя 5;

и - количество элементов в пакете, передаваемом по цифровому тракту;

тп - количество стробирующих импульсов, приходящихся на самую короткую дискретную посылку (определяется исходя из требования по краевым искажениям). Запись информации о количестве «1 в пакете в первый регистр 10 проходит через первый управляемый инвертор 9 при ее считывании с блока 6 памяти. В первый регистр

10 через элемент И-НЕ 8 записывается также информация об инвертированном значении первого элемента пакета, подлежащего замене. Инверсия указанного элемента

нужна для улучщения структуры сигнала, передаваемого по цифровому тракту при поступлении на вход устройства дискретного сигнала с нулевым состоянием. Первый управляемый инвертор 9 инвертирует после-. довательность с блока 6 памяти в случае поступления управляющей команды «1 с элемента И-НЕ 8, на второй вход которого поступает сигнал с второго выхода первого делителя 5. Последовательность, записанная в первом регистре 10, имеет достаточную информацию о входном дискретном сигнале для его восстановления. С первого регистра 10 информация передается через цифровой тракт 3 на коммутатор 20, который транслирует поступающий сигнал о ко0

личестве «1 в передаваемом сигнале на

0

второй регистр 14, а о месте «1 - на второй вход триггера 17. Переключение коммутатора 20 происходит по команде с второго делителя 12.

Для синхронной работы передающей 1

5 и приемной 2 сторон начальной установкой второго делителя 12 управляет блок 13 синхронизации, который в качестве синхронизирующей .может использовать комбинацию вида «11110, образующуюся при передаче двух и более подряд следующих единичных входных дискретных сигналов, подлежащих передаче. В случае использования устройства ввода дискретных сигналов при построении многоканальной аппаратуры передачи дискретных сигналов установкой

с второго делителя 12 управляет общестанционное оборудование синхронизации передающей стороны 1. В этом случае необходимость в индивидуальном блоке 13 синхронизации отпадает. Информация о количестве «I с второго регистра 14 переписывает0 ся в дещифратор 15, на выходе которого выдается серия «1, соответствующая двоичному числу, поступившему на него. Последовательность с выхода дещифратора 15 поступает на второй управляе.мый инвертор

5 16, работой которого управляет триггер 17. Последний вырабатывает сигнал только в случае поступления на его второй вход «1. Полученная выходная последовательность второго управляемого инвертора 16 поступает на блок 19 выделения огибающей се0 рии импульсов, на выходе которого образуется последовательность сигнала, эквивалентная сигналу, подлежащему передаче.

Формула изобретения

Устройство ввода дискретных сигналов, содержащее на передающей стороне первый датчик стробирующих импульсов, выход которого соединен с входом первого делителя, первый выход которого соединен с первым входом блока памяти и первым входом счетчика, а на приемной стороне второй делитель, вход которого соединен с выходом блока синхронизации, отличающееся тем, что, с целью повышения пропускной способности, в него введены на передающей стороне элемент И-НЕ, первый управляемый инвертор, первый регистр, блок стробиро- вания, выход которого соединен с первым входом элемента И-НЕ и вторым входом счетчика, выходы которого соединены соот- ветственно с входами блока памяти, выход элемента И-НЕ соединен с первым входом первого управляемого инвертора и первым входом первого регистра, вторые входы которого соединены соответственно с выходами первого управляемого инвертора, вторые входы которого соединены соответственно с выходами блока памяти, а второй выход делителя соединен с вторым входом элемента И-НЕ, вход блока стробирования соединен с выходом первого датчика стро- бирующих импульсов, а на приемной стороне - второй регистр, дешифратор, второй управляемый инвертор, триггер, второй датчик стробирующих импульсов, блок определения огибающей серий импульсов, коммутатор, первый выход которого соединен с первым входом второго регистра, выходы которого соединены соответственно с входами дешифратора, выход которого соединен с первым входом второго управляемого инвертора, второй вход которого соединен с выходом триггера, первый вход которого

соединен с первым входом коммутатора, первым выходом второго делителя, и вторым входом второго регистра, второй выход которого соединен с входом второго датчика стробирующих импульсов и первым входом

блока выделения огибающей серий импульсов, второй вход которого соединен с выходом второго управляемого инвертора, второй вход триггера соединен с вторым выходом коммутатора, вход блока синхронизации соединен с входом коммутатора, причем передающая сторона соединена с приемной стороной через цифровой тракт, причем выход первого регистра является выходом передающей стороны, а вход коммутатора является входом приемной стороны.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения дискретного сигнала с синхронным цифровым трактом | 1987 |

|

SU1610600A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020424C1 |

| Устройство для предварительной обработки информации | 1991 |

|

SU1837274A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1993 |

|

RU2038634C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020422C1 |

| Анализатор экстремумов | 1984 |

|

SU1196810A1 |

Изобретение относится к технике связи и обеспечивает повышение пропускной способности. Устройство содержит на передающей стороне 1 датчик 4 стробирующих импульсов, делитель 5, блок памяти (БП) 6, счетчик 7, элемент И-НЕ 8, управляемый инвертор (УИ) 9, регистр 10 и блок строби- рования 11, а на приемной стороне 2 делитель 12, блок синхронизации 13, регистр 14, дешифратор 15, УИ 16, триггер 17, датчик стробирующих импульсов 18, блок 19 выделения огибающей серий импульсов, коммутатор 20. На вход устройства поступает дискретный сигнал. Сформированная из него в блоке стробирования 11 импульсная последовательность поступает на счетчик 7. Информация о количестве «1 в пакете со счетчика 7 записывается в БП 6 и далее через УИ 9 в регистр 10. УИ 9 инвертирует последовательность с БП 6, если с элемента И-НЕ 8 поступает команда «I. В регистр 10 через элемент И-НЕ 8 записывается также информация об инвертированном значении первого элемента пакета, подлежащего замене. Последовательность, записанная в регистре 10, имеет достаточную информацию о входном дискретном сигнале для его восстановления. На приемной стороне коммутатор 20 передает поступающий сигнал о количестве «1 в передавае.мом сигнале на регистр 14, а о месте «1 - на триггер 17. 1 ил. с S (Я со :о ю со

| Емельянов Г | |||

| Д., Шварцман В | |||

| О | |||

| Передача дискретной информации | |||

| - М.: Радио и связь, 1982, с | |||

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Устройство для ввода двоичной информации | 1980 |

|

SU924885A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-23—Публикация

1985-11-06—Подача