Изобретение относится к вычислительной технике и может быть использовано при обработке сигналов, данных измерений и т.д.

Цель изобретения - расширение функциональных возможностей за счет автоматического определения градиента функции.

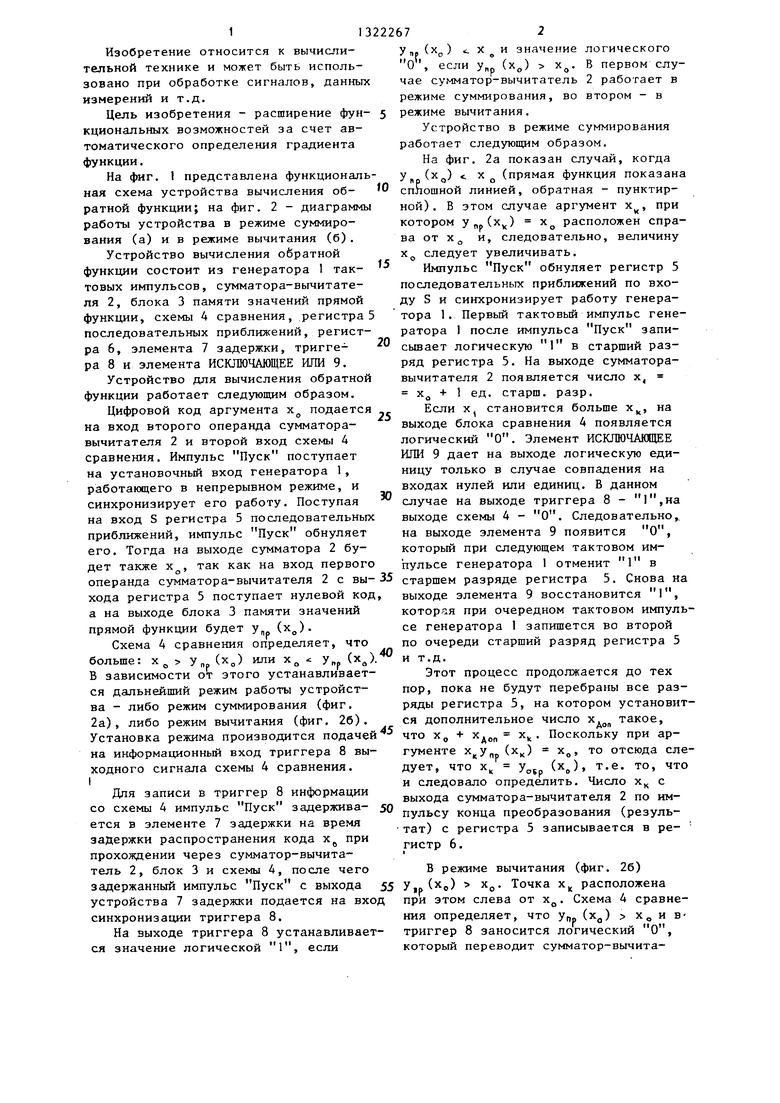

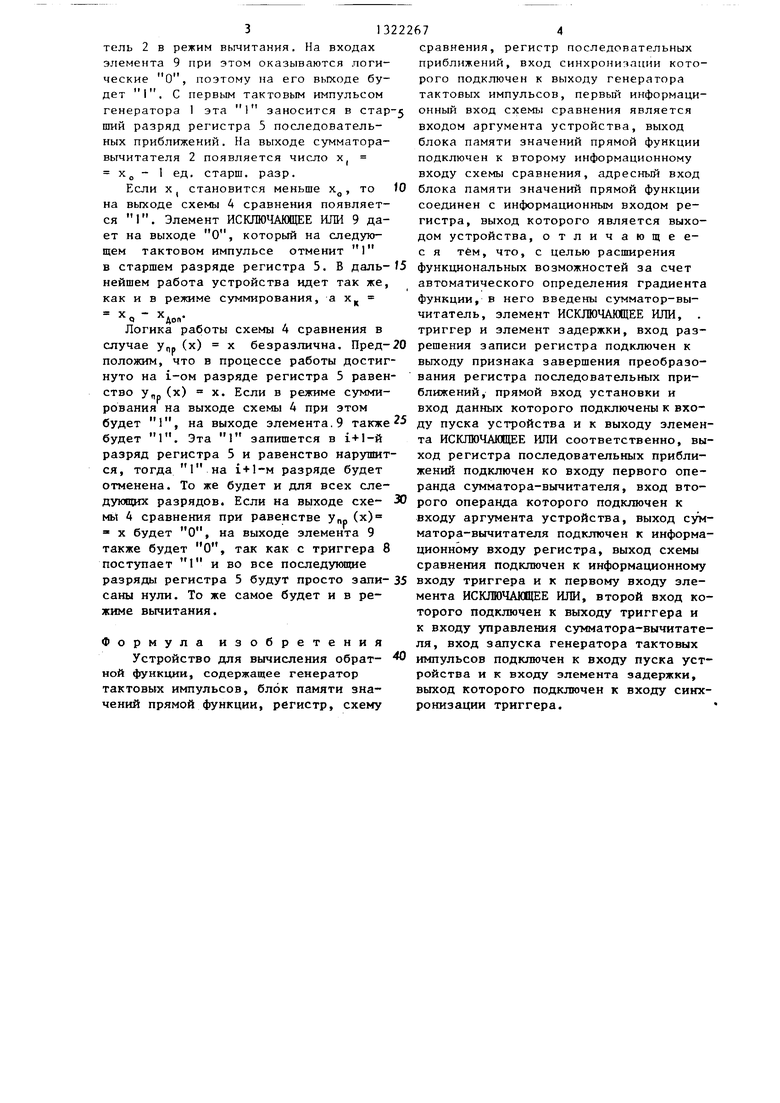

На фиг. 1 представлена функциональная схема устройства вычисления обратной функции; на фиг. 2 - диаграммы работы устройства в режиме суммирования (а) и в режиме вычитания (б).

Устройство вычисления обратной функции состоит из генератора 1 тактовых импульсов, сумматора-вычитате- ля 2, блока 3 памяти значений прямой функции, схемы 4 сравнения, регистра 5 последовательных приближений, регистра 6, элемента 7 задержки, триггера 8 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9.

Устройство для вычисления обратной функции работает следующим образом.

Цифровой код аргумента х подается на вход второго операнда сумматора- вычитателя 2 и второй вход схемы 4 сравнения. Импульс Пуск поступает на установочный вход генератора 1, работающего в непрерывном режиме, и синхронизирует его работу. Поступая на вход S регистра 5 последовательньрс приближений, импульс Пуск обнуляет его. Тогда на выходе сумматора 2 будет также Хд, так как на вход первого операнда сумматора-вычитателя 2 с вы- хода регистра 5 поступает нулевой код а на выходе блока 3 памяти значений прямой функции будет у (х).

Схема 4 сравнения определяет, что больше: х у (xj или х„ у„ (х) В зависимости от этого устанавливается дальнейший режим работы устройства - либо режим суммирования (фиг. 2а), либо режим вычитания (фиг. 26). Установка режима производится подачей на информационный вход триггера 8 выходного сигнала схемы 4 сравнения. I

Для записи в триггер 8 информации со схемы 4 импульс Пуск задержива- ется в элементе 7 задержки на время задержки распространения кода х при прохождении через сумматор-вычита- тель 2, блок 3 и схемы 4, после чего задержанный импульс Пуск с выхода устройства 7 задержки подается на вхо синхронизации триггера 8.

На выходе триггера 8 устанавливает

ся значение логической 1

если

у„. (Xj,) t значение логического О , если у„ (Xj,) Xg. В первом случае сумматор-вычитатель 2 работает в режиме суммирования, во втором - в режиме вычитания.

Устройство в режиме суммирования работает следующим образом.

На фиг. 2а показан случай, когда У| (Хд) «. X (прямая функция показана сплошной линией, обратная - пунктирной). В этом случае аргумент х, при

котором У „р (х) X

ва от X

расположен спра- и, следовательно, величину

Хд следует увеличивать.

Импульс Пуск обнуляет регистр 5 последовательных приближений по входу S и синхронизирует работу генератора 1. Первый тактовый импульс генератора 1 после импульса Пуск записывает логическую 1 в старший разряд регистра 5. На выходе сумматора- вычитателя 2 появляется число х, X + 1 ед. старш. разр.

5

0 5

0

0

5

Если X, становится больше х.

на

выходе блока сравнения 4 появляется логический О. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9 дает на выходе логическую единицу только в случае совпадения на входах нулей или единиц. В данном случае на выходе триггера 8 - 1,на выходе схемы 4 - О. Следовательно,. на выходе элемента 9 появится О, который при следующем тактовом импульсе генератора 1 отменит 1 в старшем разряде регистра 5. Снова на выходе элемента 9 восстановится 1, которая при очередном тактовом импульсе генератора 1 запишется во второй по очереди старший разряд регистра 5 и т.д.

Этот процесс продолжается до тех пор, пока не будут перебраны все разряды регистра 5, на котором установится дополнительное число х, такое,

АОП

что Хд + доп Поскольку при аргументе (х) Хд, то отсюда следует, что х у, (о) т.е. то, что

ВР и следовало определить. Число х с

выхода сумматора-вычитателя 2 по импульсу конца преобразования (резуль- тат) с регистра 5 записывается в регистр 6.

В режиме вычитания (фиг. 26) У,р (о) о- Точка X|j расположена при этом слева от х. Схема 4 сравнения определяет, что у„ (х) х„ и в- триггер 8 заносится логический О, который переводит сумматор-вычитатель 2 в режим вычитания. На входах элемента 9 при этом оказываются логические О, поэтому на его выходе будет I. С первым тактовым импульсом генератора 1 эта 1 заносится в стар ший разряд регистра 5 последовательных приближений. На выходе сумматора- вычитателя 2 появляется число х Хд - 1 ед. старш. разр.

Если Xj становится меньше х, то на выходе схемы А сравнения появляется 1. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9 дает на выходе О, который на следующем тактовом импульсе отменит 1 в старшем разряде регистра 5. В дальнейшем работа устройства идет так же, как и в режиме суммирования, а х

- Y « V

q АОПЛогика работы схемы 4 сравнения в случае у. (х) х безразлична. Предположим, что в процессе работы достигнуто на L-OM разряде регистра 5 равенство у„ (х) X. Если в режиме суммирования на выходе схемы 4 при этом будет 1, на выходе элемента.9 также будет 1. Эта 1 запишется в i+1-й разряд регистра 5 и равенство нарушится, тогда 1 на i+1-м разряде будет отменена. То же будет и для всех сле- дукяцих разрядов. Если на выходе схе- Mbt 4 сравнения при равенстве у„р (х) X будет О, на выходе элемента 9 также будет О, так как с триггера 8 поступает 1 и во все последующие разряды регистра 5 будут просто запи- саны нули. То же самое будет и в режиме вычитания.

Формула изобретения

Устройство для вычисления обрат- ной функции, содержащее генератор тактовых импульсов, блок памяти значений прямой функции, регистр, схему

сравнения, регистр последовательных приближений, вход синхронизации которого подключен к выходу генератора тактовых импульсов, первьв информационный вход схемы сравнения является входом аргумента устройства, выход блока памяти значений прямой функции подключен к второму информационному входу схемы сравнения, адресный вход блока памяти значений прямой функции соединен с информационным входом регистра, выход которого является выходом устройства, отличающее- с я тем, что, с целью расширения функциональных возможностей за счет автоматического определения градиента функции, в него введены сумматор-вы- читатель, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, . триггер и элемент задержки, вход разрешения записи регистра подключен к выходу признака завершения преобразования регистра последовательных приближений, прямой вход установки и вход данных которого подключены к входу пуска устройства и к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, выход регистра последовательных приближений подключен ко входу первого операнда сумматора-вьгчитателя, вход второго операнда которого подключен к входу аргумента устройства, выход матора-вычитателя подключен к информационному входу регистра, выход схемы сравнения подключен к информационному входу триггера и к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу триггера и к входу управления сумматора-вычитате- ля, вход запуска генератора тактовых импульсов подключен к входу пуска устройства и к входу элемента задержки, выход которого подключен к входу синхронизации триггера.

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

| Цифровой функциональный преобразователь | 1989 |

|

SU1695321A1 |

| Конвейерное устройство для вычисления тригонометрических функций | 1984 |

|

SU1168931A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Устройство для возведения в степень | 1986 |

|

SU1363205A1 |

Изобретение относится к вычислительной технике и может быть использовано при обработке сигналов, данных измерений и т.д. Устройство Гтредназна- чено для вычисления обратных функций. Цель изобретения - расширение функциональных возможностей за счет модификации алгоритма работы. Устройство содержит генератор 1 тактовых импульсов, сумматор 2, блок 3 памяти значений прямой функции, схему 4 сравнения, регистр 5 последовательных приближений, регистр 6, элемент 7 задержки, триггер 8 и злемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9 с соответствующими связями. Принцип работы устройства основан на поразрядном приближении к значению обратной функции. 2 ил. (Л Й/г./

| Устройство для вычисления обратных функций | 1975 |

|

SU589610A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный преобразователь | 1985 |

|

SU1285465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-04-19—Подача