I

Изобретение относится к вычислиельной технике и может быть испольовано при построении подсистем вода, каналов и устройств, обеспеивающих ввод измерительной информаии с селекцией некоторых измерительых каналов.

Цель изобретения - повышение наежности устройства за счет сокращеия объема оперативной памяти.путем использования инверсной дисцилины выделения, т.е. селекции даных для каналов, фаза которьтх не совпадает с заданной, если число выделяемых каналов больше половины общего числа коммутируемых измерительных каналов, и прямой дисциплины выделения, т.е. селекции данных для каналов, фаза или временной интервал которых совпадают с заданной величиной, если число выделяемых каналов меньше половины общего числа коммутируемьк измерительных каналов .

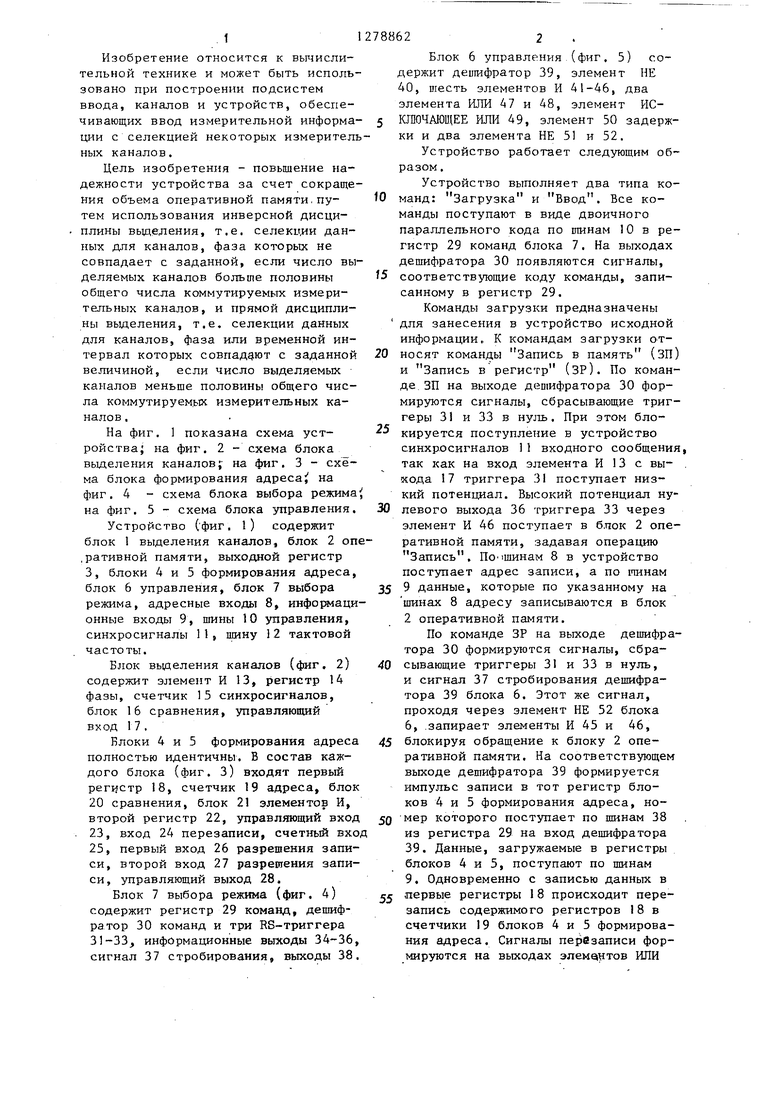

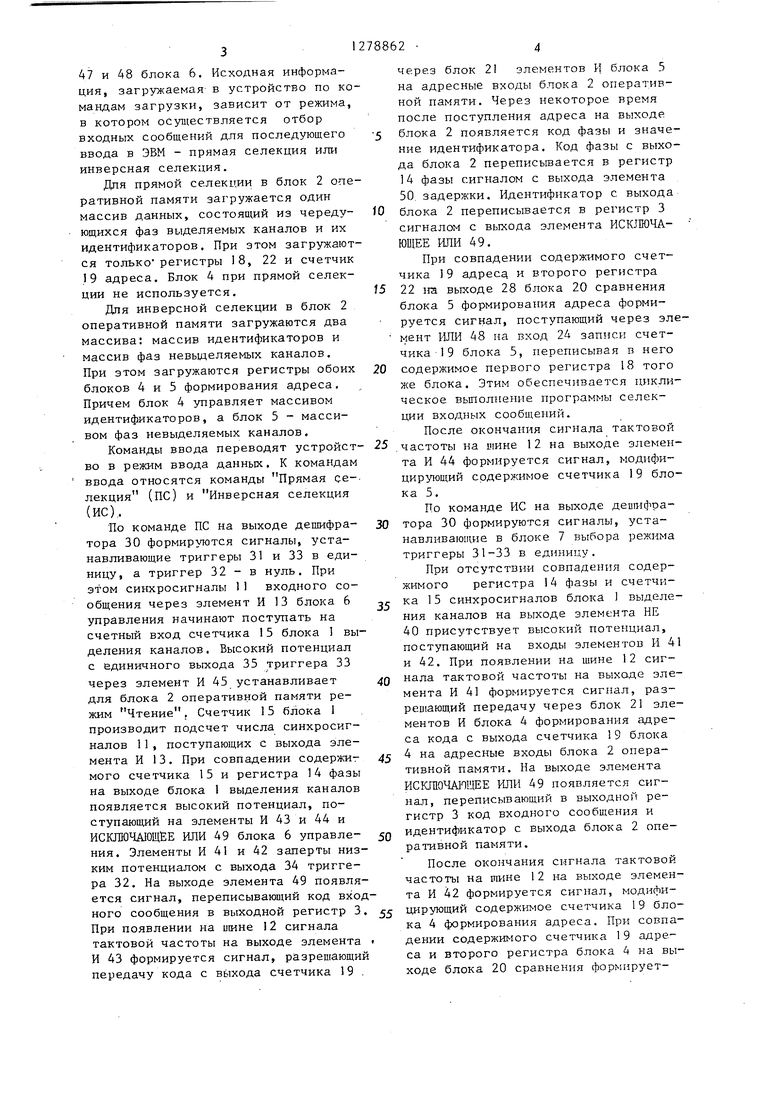

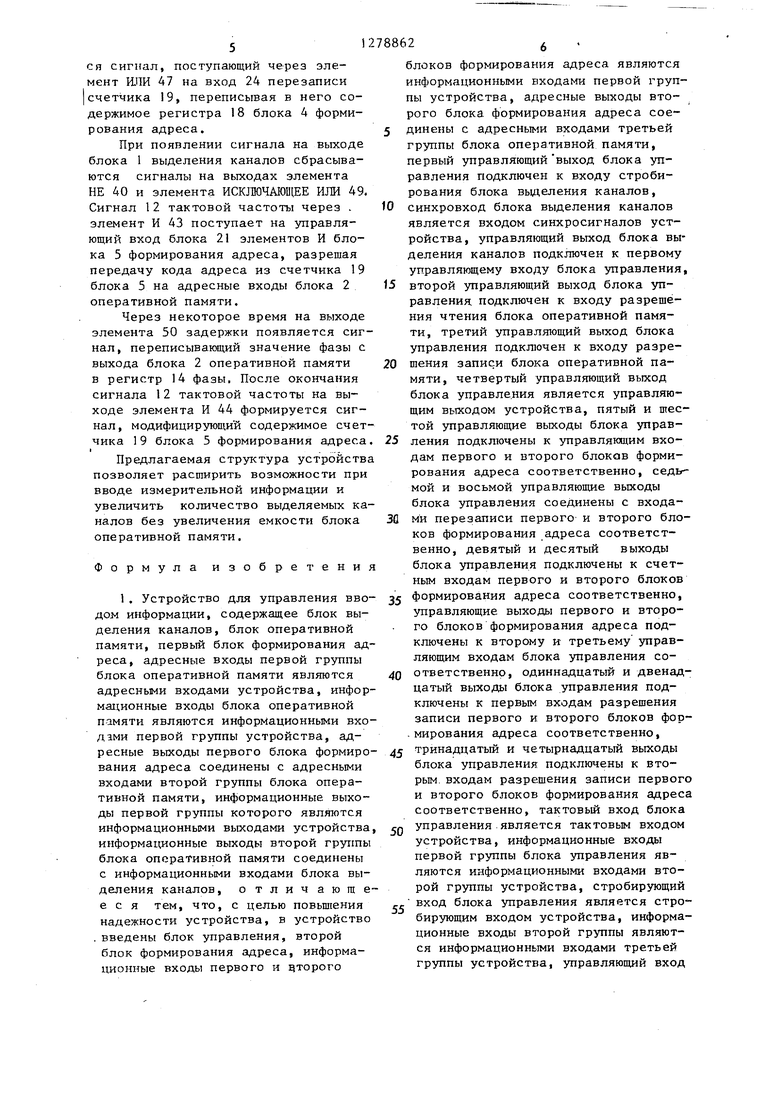

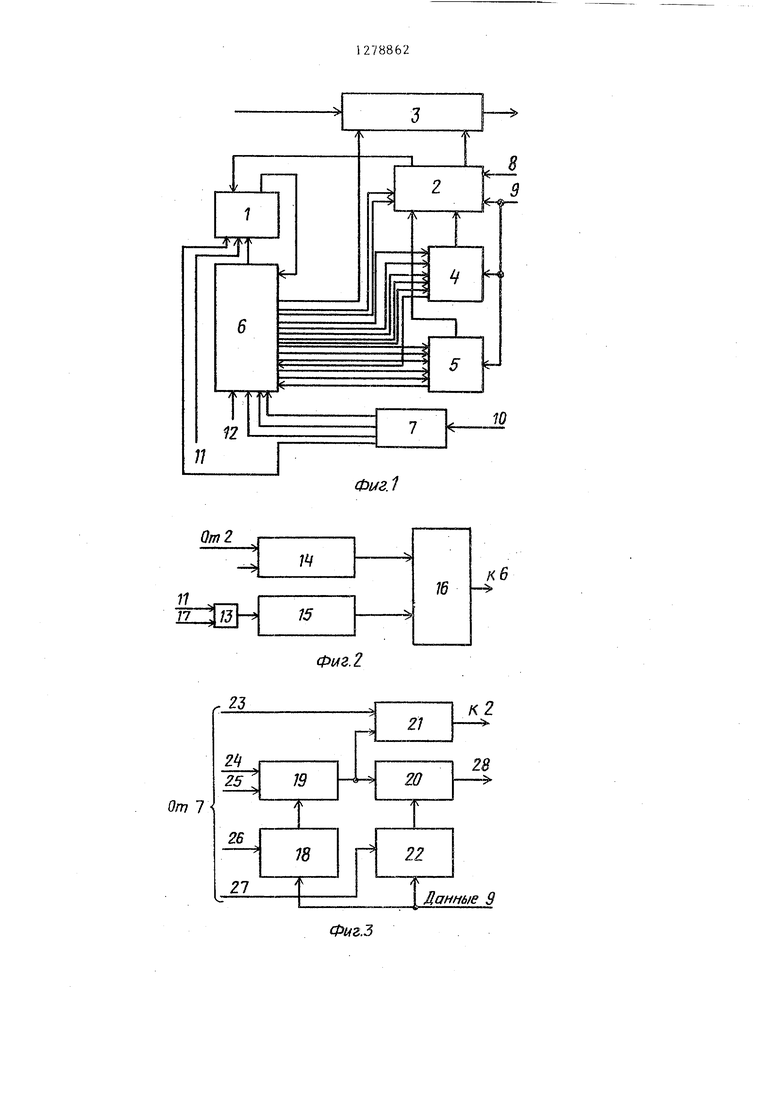

На фиг. 1 показана схема устройства; на фиг. 2 - схема блока выделения каналов; на фиг. 3 - схема блока формирования адреса на фиг. 4 - схема блока выбора режима на фиг. 5 - схема блока управления.

Устройство ( фиг, 1) содержит блок 1 выделения каналов, блок 2 опе- ративной памяти, выходной регистр 3, блоки 4 и 5 формирования адреса, блок 6 управления, блок 7 выбора режима, адресные входы 8, информационные входы 9, щины 10 управления, синхросигналы 11, шину 12 тактовой частоты.

Блок вьщеления каналов (фиг. 2) содержит элемент И 13, регистр 14 фазы, счетчик 15 синхросигналов, блок 16 сравнения, управляющий вход 17.

Блоки 4 и 5 формирования адреса полностью идентичны. В состав каждого блока (фиг. З) входят первый регистр 18, счетчик 19 адреса, блок 20 сравнения, блок 21 элементов И, второй регистр 22, управляющий вход 23, вход 24 перезаписи, счетньй вход 25, первый вход 26 разрешения записи, второй вход 27 разрешения записи, управляющий выход 28.

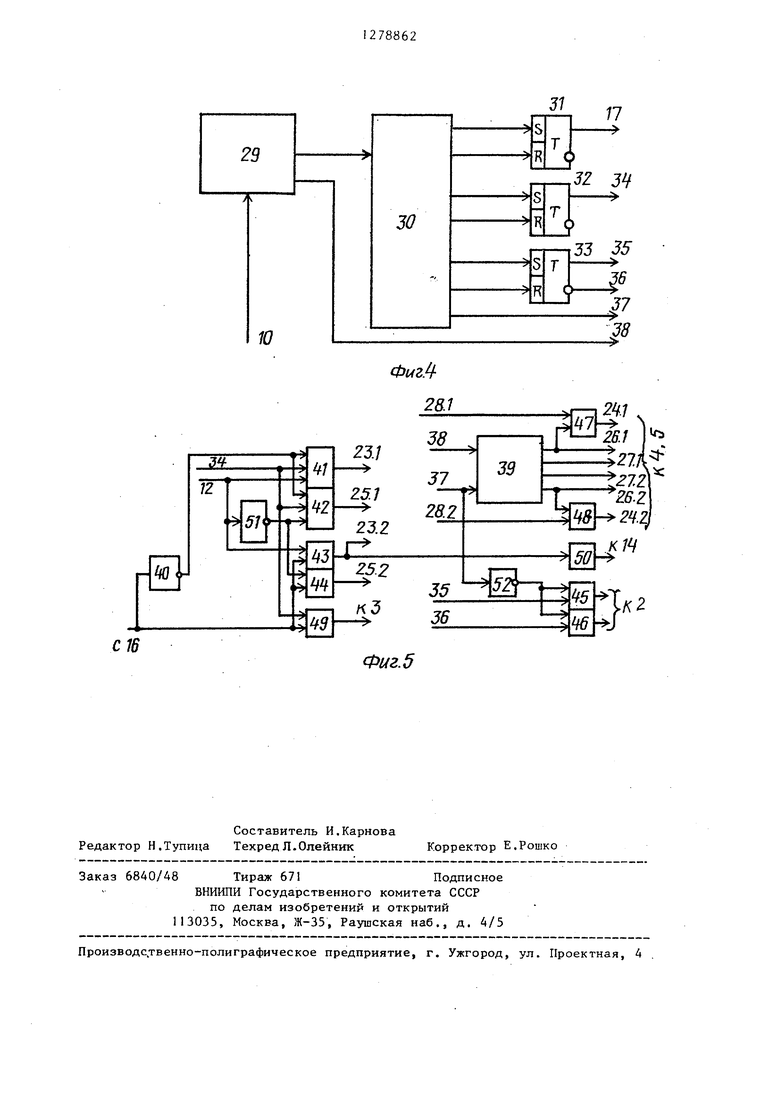

Блок 7 выбора режима (фиг. 4) содержит регистр 29 команд, дешифратор 30 команд и три RS-триггера 31-33, информационные выходы 34-36, сигнал 37 стробироваиия, выходы 38.

СОНЕ

41-46, два элемент ИС10

15

20

25

788622

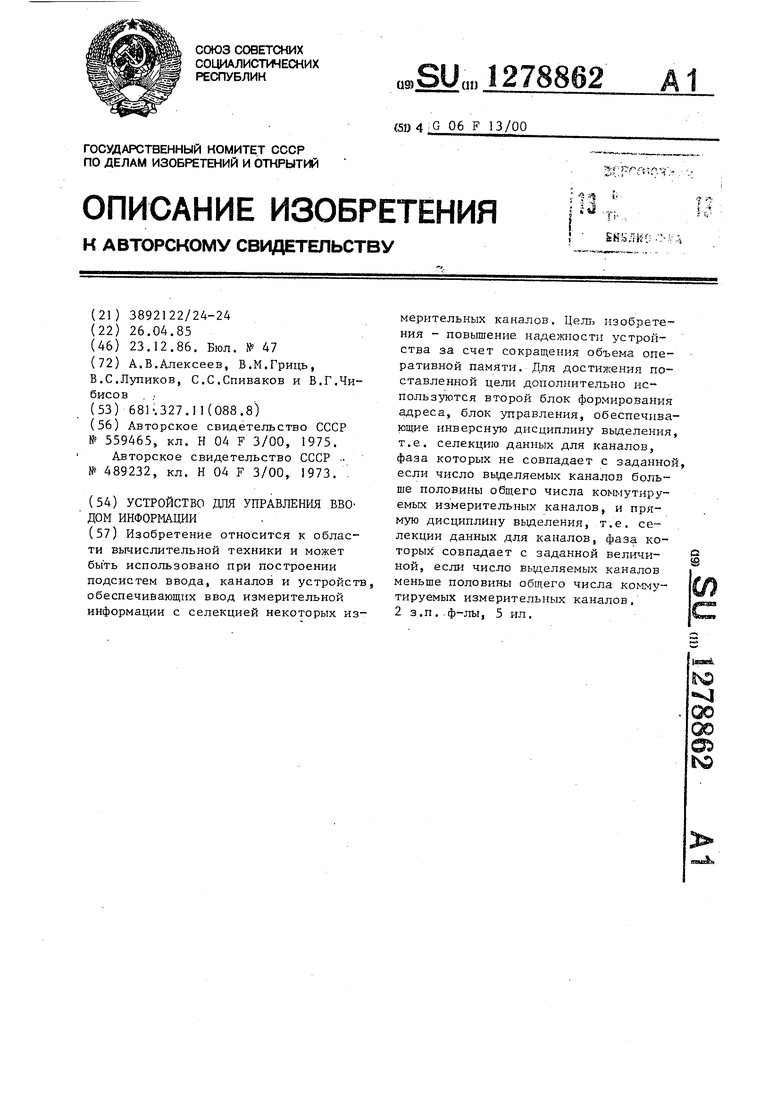

Блок 6 управления,(фиг. 5) держит деитифратор 39, элемент 40, шесть элементов И элемента ИЛИ 47 и 48,

5 КЛЮЧАЮЩЕЕ ИЛИ 49, элемент 50 задержки и два элемента НЕ 51 и 52.

Устройство работает следующим образом .

Устройство выполняет два типа команд: Загрузка и Ввод. Все команды поступают в виде двоичного параллельного кода по шинам О в регистр 29 команд блока 7. На выходах дешифратора 30 появляются сигналы, соответствующие коду команды, записанному в регистр 29.

Команды загрузки предназначены для занесения в устройство исходной информации, К командам загрузки относят команды Запись в память (ЗП) и Запись в регистр (ЗР). По команде ЗП на выходе дешифратора 30 формируются сигналы, сбрасывающие триггеры 31 и 33 в нуль. При этом блокируется поступление в устройство синхросигналов 1 входного сообщения, так как на вход элемента И 13 с вы- , кода 17 триггера 31 поступает низкий потенциал. Высокий потенциал нулевого выхода 36 триггера 33 через элемент И 46 поступает в блок 2 оперативной памяти, задавая операцию Запись, По шинам 8 в устройство поступает адрес записи, а по пинам 9 данные, которые по указанному на шинах 8 адресу записываются в блок 2 оперативной памяти.

По команде ЗР на выходе дешифратора 30 формируются сигналы, сбрасывающие триггеры 31 и 33 в нуль, и сигнал 37 стробирования дешифратора 39 блока 6. Этот же сигнал, проходя через элемент НЕ 52 блока 6, .запирает элементы И 45 и 46, блокируя обращение к блоку 2 оперативной памяти. На соответствующем выходе дешифратора 39 формируется импульс записи в тот регистр блоков 4 и 5 формирования адреса, номер которого поступает по шинам 38 из регистра 29 на вход дешифратора 39. Данные, загружаемые в регистры блоков 4 и 5, поступают по шинам 9, Одновременно с записью данных в первые регистры 18 происходит перезапись содержимого регистров 18 в счетчики 19 блоков 4 и 5 формирования адреса. Сигналы перезаписи формируются на выходах элемедтов ИЛИ

30

35

40

45

50

55

47 и 48 блока 6. Исходная информация, загружаемая в устройство по командам загрузки, зависит от режима, в котором осуществляется отбор входных сообщений для последующего ввода в ЭВМ - прямая селекция или инверсная селекция.

Для прямой селекции в блок 2 оперативной памяти загружается один массив данных, состоящий из чередующихся фаз Выделяемых каналов и их идентификаторов. При этом загружаются ТОЛЬКО регистры 18, 22 и счетчик 19 адреса. Блок 4 при прямой селекции не используется.

Для инверсной селекции в блок 2 оперативной памяти загружаются два массива: массив идентификаторов и массив фаз невьщеляемых каналов. При этом загружаются регистры обоих блоков 4 и 5 формирования адреса, Причем блок 4 управляет массивом идентификаторов, а блок 5 - массивом фаз невыделяемых каналов.

Команды ввода переводят устройство в режим ввода данных. К командам ввода относятся команды Прямая селекция (ПС) и Инверсная селекция (ИС),.

По команде ПС на выходе дешифратора 30 формируются сигналы, устанавливающие триггеры 31 и 33 в единицу, а триггер 32 - в нуль. При этом синхросигналы 11 входного сообщения через элемент И 13 блока 6 управления начинают поступать на счетный вход счетчика 15 блока 1 выделения каналов. Высокий потенциал с единичного выхода 35 триггера 33 через элемент И 45 устанавливает для блока 2 оперативной памяти режим Чтение, Счетчик 15 блока 1 производит подсчет числа синхросигналов 11, поступающих с выхода элемента И 13. При совпадении содержит мого счетчика 15 и регистра 14 фазы на выходе блока 1 выделения каналов появляется высокий потенциал, поступающий на элементы И 43 и 44 и ИСКЛЮЧАЮЩЕЕ ИЛИ 49 блока 6 управления. Элементы И 41 и 42 заперты низким потенциалом с выхода 34 триггера 32. На выходе элемента 49 появляется сигнал, переписывающий код входного сообщения в выходной регистр 3 При появлении на иине I2 сигнала тактовой частоты на выходе элемента И 43 формируется сигнал, разрешающий передачу кода с выхода счетчика 19 .

через блок 21 элементов И блока 5 на адресные входы блока 2 оперативной памяти. Через некоторое время после поступления адреса на выходе

блока 2 появляется код фазы и значение идентификатора. Код фазы с выхода блока 2 переписьшается в регистр 14 фазы сигналом с выхода элемента 50. задержки. Идентификатор с выхода

блока 2 переписывается в регистр 3 сигналом с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 49.

При совпадении содержимого счетчика 19 адресд и второго регистра

22 ira выходе 28 блока 20 сравнения блока 5 формирования адреса формируется сигнал, поступающий через эле- мент ИЛИ 48 па вход 24 записи счетчика 1 9 блока 5, переписывая в него

содержимое первого регистра 18 того же блока. Этим обеспечивается циклическое выполнение программы селекции входных сообщений.

После окончания сигнала тактовой

частоты на шине 12 на выходе элемента И 44 формируется сигнал, модифицирующий содержимое счетчика 19 блока 5 .

По команде ИС на выходе деишфратора 30 формируются сигналы, устанавливающие в блоке 7 выбора режима триггеры 31-33 в единицу.

При отсутствии совпадения содержимого регистра 14 фазы и счетчика 15 синхросигналов блока 1 выделения каналов на выходе элемента НЕ 40 присутствует высокий потенциал, поступающий на входы элементов И 41 и 42. При появлении на шине 12 сигнала тактовой частоты на выходе элемента И 41 формируется сигнал, разрешающий передачу через блок 21 элементов И блока 4 формирования адреса кода с выхода счетчика 19 блока

4 на адресные входы блока 2 оперативной памяти. На выходе элемента ИСКШОЧА11ЩЕЕ ИЛИ 49 появляется сигнал, переписывающий в выходной регистр 3 код входного сообщения и

идентификатор с выхода блока 2 оперативной памяти.

После окончания сигнала тактовой частоты на тине 12 на выходе элемента И 42 формируется сигнал, модифи- цирующий содержимое счетчика 19 блока 4 формирования адреса. При совпадении содержимого счетчика 19 адреса и второго регистра блока 4 на выходе блока 20 сравнения формируетс я сигнал, поступающий через элемент И.ПИ 47 на вход 24 перезаписи счетчика 19, переписывая в него содержимое регистра 18 блока 4 формирования адреса.

При появлении сигнала на выходе блока 1 выделения каналов сбрасываются сигналы на выходах элемента НЕ 40 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 49. Сигнал 12 тактовой частоты через . элемент И 43 поступает на управляющий вход блока 21 элементов И блока 5 формирования адреса, разрещая передачу кода адреса из счетчика 19 блока 5 на адресные входы блока 2 оперативной памяти.

Через некоторое время на выходе элемента 50 задержки появляется сигнал, переписывающий значение фазы с выхода блока 2 оперативной памяти в регистр 14 фазы, После окончания сигнала 12 тактовой частоты на выходе элемента И 44 формируется сигнал, модифицирующий содержимое счетчика 19 блока 5 формирования адреса

Предлагаемая структура устройства позволяет расширить возможности при вводе измерительной информации и увеличить количество выделяемых каналов без увеличения емкости блока оперативной памяти.

Формула изобретения

1. Устройство для управления вводом информации, содержащее блок выделения каналов, блок оперативной памяти, первый блок формирования адреса, адресные входы первой группы блока оперативной памяти явл5Ш)тся адресными входами устройства, информационные входы блока оперативной памяти являются информационными входами первой группы устройства, адресные выходы первого блока формирования адреса соединены с адресными входами второй группы блока оперативной памяти, информационные выходы первой группы которого являются информационными выходами устройства информационные выходы второй группы блока оперативной памяти соединены с информационными входами блока выделения каналов, отличающееся тем, что, с целью повьщ ения надежности устройства, в устройство . введены блок управления, второй блок формирования адреса, информационные входы первого и щторого

5

0

5

а

5

0

5

0

55

блоков формирования адреса являются информационными входами первой группы устройства, адресные выходы второго блока формирования адреса соединены с адресными входами третьей группы блока оперативной памяти, первый управляющий выход блока управления подключен к входу строби- рования блока выделения каналов, синхровход блока выделения каналов является входом синхросигналов устройства, управляющий выход блока выделения каналов подключен к первому управляющему входу блока управления, второй управляющий выход блока управления подключен к входу разрешения чтения блока оперативной памяти, третий управляющий выход блока управления подключен к входу разрешения записи блока оперативной памяти, четвертый управляющий выход блока управления является управляющим выходом устройства, пятый и тестой управляющие выходы блока управления подключены к управляющим входам первого и второго блоков формирования адреса соответственно, седьмой и восьмой управляющие выходы блока управления соединены с входами перезаписи первого и второго блоков формирования адреса соответственно, девятый и десятый выходы блока управления подключены к счетным входам первого и второго блоков формирования адреса соответственно, управляющие выходы первого и второго блоков формирования адреса подключены к второму и третьему управляющим входам блока управления соответственно, одиннадцатый и двенадцатый выходы блока управления подключены к первым входам разрешения записи первого и второго блоков фор- .мирования адреса соответственно, тринадцатый и четырнадцатый выходы блока управления подключены к вторым, входам разрешения записи первого и второго блоков формирования адреса соответственно, тактовый вход блока управления является тактовым входом устройства, информационные входы первой группы блока управления являются информационными входами второй группы устройства, стробирующий вход блока управления является стро- бирующим входом устройства, информационные входы второй группы являются информационными входами третьей группы устройства, управляющий вход

7

блока выделения каналов является управляющим входом устройства.

2, Устройство по п. 1, отличаю m е е с я тем, что блок управления содержит дешифратор, шест элементов И, два элемента ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент задержки, три элемента НЕ, информаци онные входы дешифратора являются иформационными входами первой групп блока, синхронизирующий вход дешифратора и вход первого элемента НЕ являются стробирующим входом блока первые входы пятого и шестого элементов И соединены с выходом первого элемента НЕ, вторые входы первого, второго, пятого и шестого элементов И и второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются информациоными входами второй группы блока, первый вход элемента ИСКЛЮЧАЮЩЕЕ Ш первые входы третьего и четвертого элементов И, вход третьего элемента НЕ являются первым управляющим входом блока, первые входы первого и второго элементов И соединены с выходом третьего элемента НЕ, вход второго элемента НЕ, третий вход первого элемента И и второй вход третьего элемента И являются тактовым входом блока, третий вход второго элемента И и второй вход четвертого элемента И подключены к выходу второго элемента НЕ, выход тртьего элемента И и вход элемента задержки являются шестым управляющим выходом блока, выход элемента задержки является первым у правляю- щиМ выходом блока, выход первого элмента И, выход второго элемента И, выход четвертого элемента И, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются пятым, девятым, десятым, четвертым управляющими выходами блока соответственно, первый вход первого элемента ИЛИ является вторым управляющим входом блока управления, первый вход второго элемента ИЛИ явля

8

ется третьим управляющим входом блока управления, первый выход дешифратора подключен к второму входу первого элемента ИЛИ и является один- 5 надцатым управляющим выходом блока, выход первого элемента ИЛИ является седьмым управляющим выходом блока, четвертый выход дешифратора подключен к второму входу второго эле0 мента ИЛИ и является двенадцатым уп- равляютигм выходом блока, второй и третий выходы дешифратора являются тринадцатым и четырнадцатым управляющими выходами блока соответственно,

5 выход, второго элемента ИЛИ является восьмым управляющим выходом блока управления, выход пятого элемента И, выход шестого элемента И являют- . ся вторым и третьим управляющими вы0 ходами блока соответственно.

3. Устройство по п. 1, о т л и- ;чающееся тем, что блок фор- ;мирования адреса содержит счетчик, блок элементов И, блок сравне ния,

5 первый и второй регистры, информационные входы первого и второго регистров являются информационными входами блока, управляющие входы первого и второго регистров являются пер0 вым и вторым входами разрешения записи соответственно, информационные выходы первого регистра соединены С информационными входами счетчика, счетный вход которого является счетe ным ВХОДОМ блока, управляющий вход счетчика является входом перезаписи блока, выходы счетчика подключены к информационным входам первой группы блока сравнения и блока элементов

0 И, информационные выходы второго регистра соединены с информационными входами второй группы блока сравнения, выход которого является управляющим выходом блока, управляющий

5 вход блока элементов И является управляющим входом блока, информационные выходы блока элементов И являются адресными выходами блока.

.2

От 7Х

.З

cw

Составитель И.Карнова Редактор Н.Тупица Техред Л.Олейник

Заказ 6840/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производс.твенно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 5

Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Устройство для ввода информации | 1978 |

|

SU746484A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1251181A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для селекции информационных каналов | 1975 |

|

SU559465A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для селекции информационных каналов | 1973 |

|

SU489232A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| . | |||

Авторы

Даты

1986-12-23—Публикация

1985-04-26—Подача