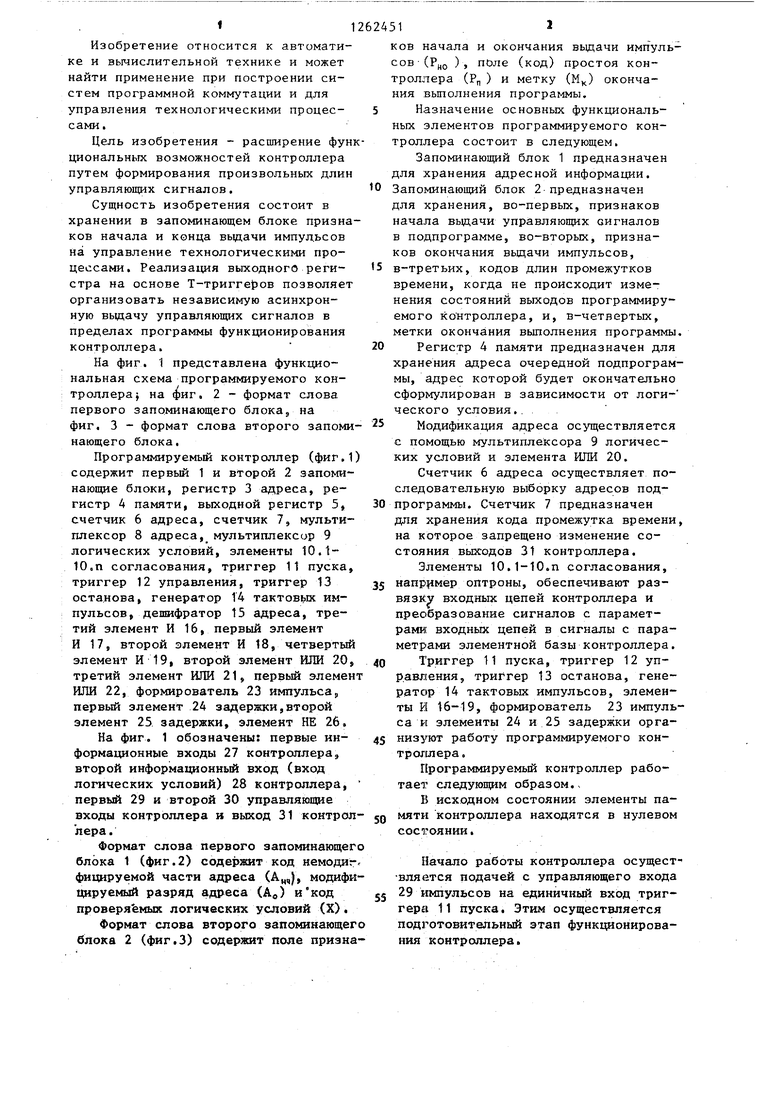

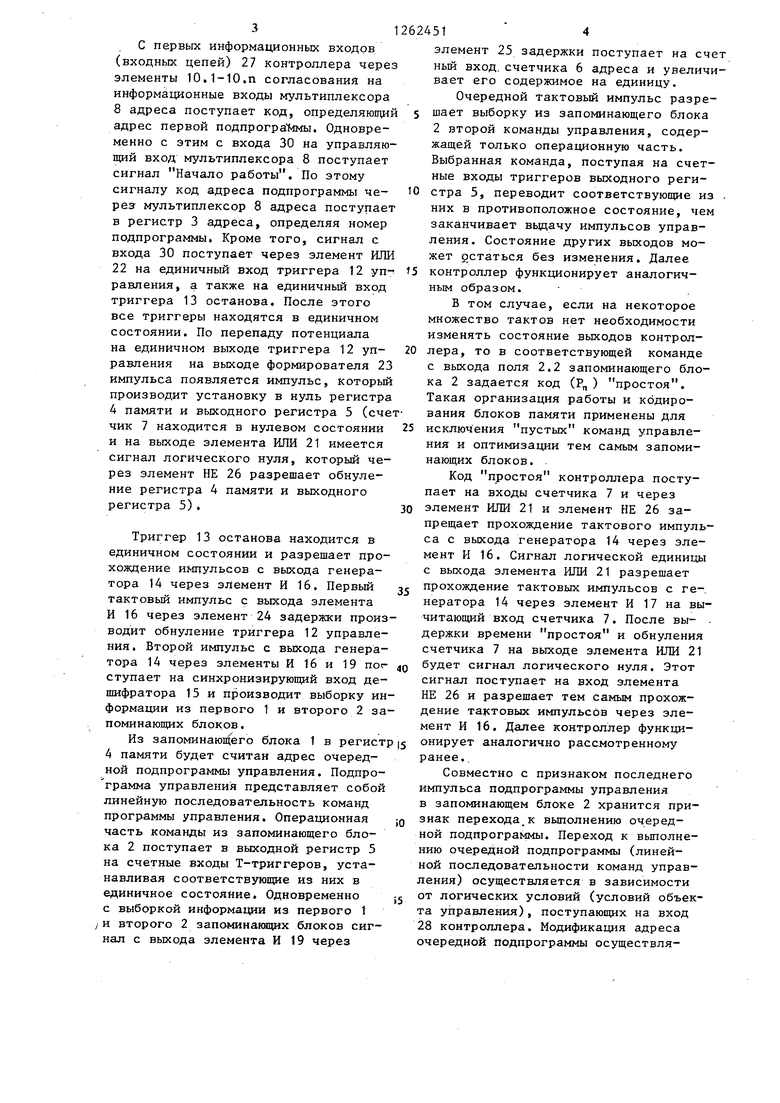

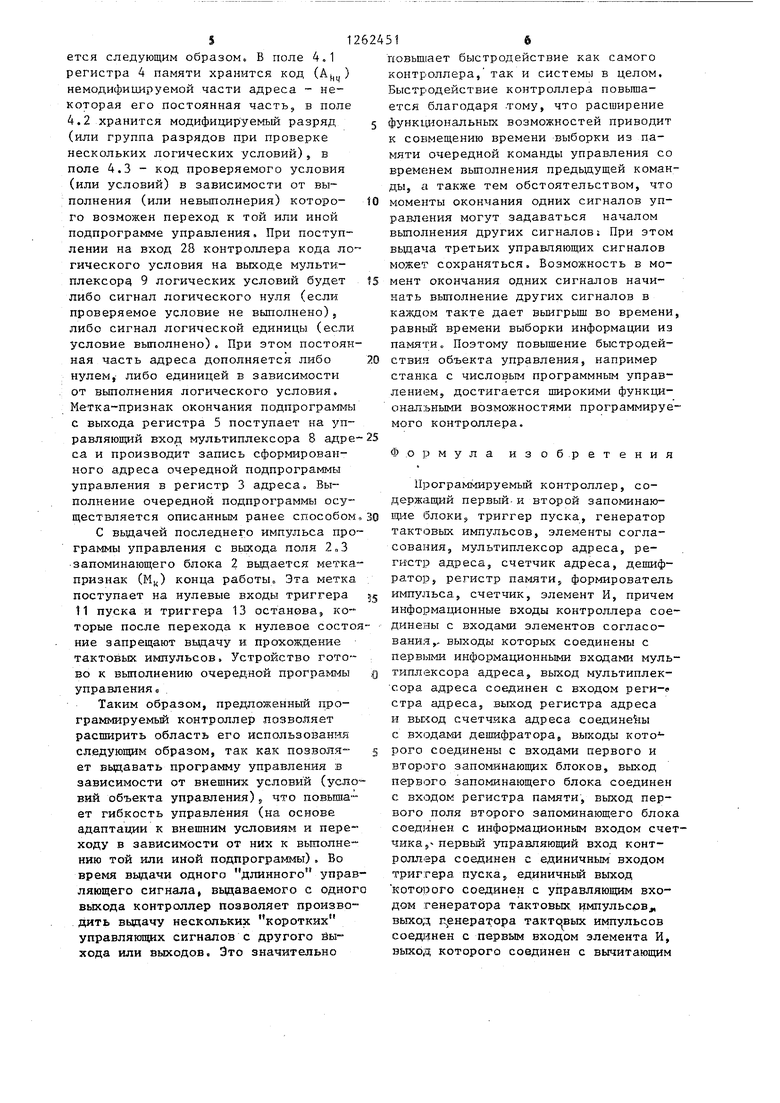

Изобретение относится к автоматике и вычислительной технике и может найти применение при построении систем программной коммутации и для управления технологическими процессами . Цель изобретения - расширение фун циональных возможностей контроллера путем формирования произвольных длин управляющих сигналов. Сущность изобретения состоит в хранении в запоминающем блоке призна ков начала и конца выдачи импул.ьсов на управление технологическими процессами. Реализация выходного регистра на основе Т-тригге1)ов позволяет организовать независимую асинхронную вьщачу управляющих сигналов в пределах программы функционирования контроллера. На фиг. 1 представлена функциональная схема программируемого контроллера ; на фиг. 2 - формат слова, первого запоминающего блока, на фиг. 3 - формат слова второго запоми нающего блока. Программируемый контроллер (фиг. содержит первый 1 и второй 2 запоминающие блоки, регистр 3 адреса, регистр 4 памяти, выходной регистр 5, счетчик 6 адреса, счетчик 7, мультиплексор 8 адреса, мультиплексор 9 логических условий, элементы 10.110.п согласования, триггер 11 пуска триггер 12 управления, триггер 13 оста.нова, генератор 14 тактовьш импульсов, дешифратор 15 адреса, третий элемент И 16, первый элемент И 17, второй элемент И 18, четверты элемент И 19, второй элемент ИЛИ 20 третий элемент ИЛИ 21, первый элеме ИЛИ 22, формирователь 23 импульса, первый элемент 24 задержки,второй элемент 25 задержки, элемент НЕ 26. На фиг, 1 обозначены: первые информационные входы 27 контроллера., второй информационный вход (вход логических условий) 28 контроллера, первый 29 и второй 30 управляющие входы контроллера и выход 31 контро лера. Формат слова первого запоминающе блока 1 (фиг.2) содержит код немоди фицируемой части адреса (А„,|, модиф цируемый разряд адреса (Ао) икод проверяёмьос логических условий (X). Формат слова второго запоминающе блока 2 (фигфз) содержит поле призн 1 ов начала и окончания выдачи импульсов- (Рцо ) поле (код) простоя контроллера (РП ) и метку (Мц) окончания выполнения программы. Назначение основных функциональных элементов программируемого контроллера состоит в следующем. Запоминающий блок 1 предназначен для хранения адресной информации. Запоминающий блок 2 предназначен для хранения, во-первых, признаков начала вьщачи управляющих сигналов в подпрограмме, во-вторых, признаков окончания вьщачи импульсов, в-третьих, кодов длин промежутков времени, когда не происходит изменения состояний выходов программируемого контроллера, и, в-четвертых, метки окончания выполнения программы. Регистр 4 памяти предназначен для хранения адреса очередной подпрограммы, адрес которой будет окончательно сформулирован в зависимости от логического условия.. Модификация адреса осуществляется с помощью мультиплексора 9 логических условий и элемента ИЛИ 20. Счетчик 6 адреса осуществляет последовательную выборку адресов подпрограммы. Счетчик 7 предназначен для хранения кода промежутка времени, на которое запрещено изменение состояния выходов 31 контроллера. Элементы 10.1-10.п согласования, например оптроны, обеспечивают развязку входных цепей контроллера и преобразование сигналов с параметрами входных цепей в сигналы с параметрами элементной базы контроллера. Триггер 11 пуска, триггер 12 управления, триггер 13 останова, генератор 14 тактовых импульсов, элементы И 16-19, формирователь 23 импульса и элементы 24 и 25 задержки организуют работу программируемого контр огш ера. Программируемый контроллер работает следуювщм образом, V В исходном состоянии элементы памяти контроллера находятся в нулевом соспгоянии. Начало работы контроллера осуществляется подачей с управляющего входа 29 импульсов на единичный вход триггера 11 пуска. Этим осуществляется подготовительный этап функционирования контроллера. с первых информационных входов (входных цепей) 27 контроллера через элементы 10,1-10.п согласования на информационные входы мультиплексора 8 адреса поступает код, определяющий адрес первой подпрограМмы. Одновременно с этим с входа 30 на управляющий вход мультиплексора 8 поступает сигнал Начало работы. По этому сигналу код адреса подпрограммы череа мультиплексор 8 адреса поступает в регистр 3 адреса, определяя номер подпрограммы. Кроме того, сигнал с входа 30 поступает через элемент ИЛИ 22 на единичный вход триггера 12 уп- 5 равления, а также на единичный вход триггера 13 останова. После этого все триггеры находятся в единичном состоянии. По перепаду потенциала на единичном выходе триггера 12 управления на выходе формирователя 2 импульса появляется импульс, которы производит установку в нуль регистр 4 памяти и выходного регистра 5 (сч чик 7 находится в нулевом состоянии и на выходе элемента ИЛИ 21 имеется сигнал логического нуля, который че рез элемент НЕ 26 разрешает обнуление регистра 4 памяти и выходного регистра 5). Триггер 13 останова находится в единичном состоянии и разрешает про хождение импульсов с выхода генератора 14 через элемент И 16. Первый тактовый импульс с выхода элемента И 16 через элемент 24 задержки произ водит обнуление триггера 12 управления. Второй импульс с выхода генератора 14 через элементы И 16 и 19 пог ступает на синхронизирующий вход дешифратора 15 и производит выборку ин формации из первого 1 и второго 2 за поминающих блоков. Из запоминающего блока 1 в регист 4 памяти будет считан адрес очередной подпрограммы управления. Подпрограмма управления представляет собой линейную последовательность команд программы управления. Операционная часть команды из запоминающего блока 2 поступает в выходной регистр 5 на счетные входы Т-триггеров, устанавливая соответствующие из них в единичное состояние. Одновременно с выборкой информации из первого 1 / и второго 2 запоминаннцих блоков сигнал с выхода элемента И 19 через 1 514 элемент 25 задержки поступает на счет ньй вход, счетчика 6 адреса и увеличивает его содержимое на единицу. Очередной тактовый импульс разрешает выборку из запоминающего блока 2 второй команды управления, содержащей только операционную часть. Выбранная команда, поступая на счетные входы триггеров выходного регистра 5, переводит соответствующие из . них в противоположное состояние, чем заканчивает вьщачу импульсов управления. Состояние других выходов может остаться без изменения. Далее контроллер функционирует аналогичным образом. В том случае, если на некоторое множество тактов нет необходимости изменять состояние выходов контроллера, то в соответствующей команде с выхода поля 2.2 запоминающего блока 2 задается код (Р) простоя. Такая организация работы и кодирования блоков памяти применены для исключения пустых команд управления и оптимизации тем самым запоминающих блоков. Код простоя контроллера поступает на входы счетчика 7 и через элемент ИЛИ 21 и элемент НЕ 26 запрещает прохождение тактового импульса с выхода генератора 14 через элемент И 16. Сигнал логической единицы с выхода элемента ИЛИ 21 разрешает прохождение тактовых импульсов с генератора 14 через элемент И 17 на вычитающий вход счетчика 7. После вы- . держки времени простоя и обнуления счетчика 7 на выходе элемента ИЛИ 21 будет сигнал логического нуля. Этот сигнал поступает на вход элемента НЕ 26 и разрешает тем самым прохождение тактовых импульсов через элемент И 16. Далее контроллер функционирует аналогично рассмотренному ранее.. Совместно с признаком последнего импульса подпрограммы управления в запоминающем блоке 2 хранится признак перехода к выполнению очередной подпрограммы. Переход к выполнению очередной подпрограммы (линейной последовательности команд управления) осуществляется в зависимости от логических условий (условий объекта управления), поступающих на вход 28 контроллера. Модификация адреса очередной подпрограммы осуществляется следующим образом. В поле 4,1 регистра 4 памяти хранится код (Ац ) немодифицируемой части адреса - некоторая его постоянная часть, в поле 4.2 хранится модифицируемый разряд (или группа разрядов при проверке нескольких логических условий), в поле 4.3 - код проверяемого условия (или условий) в зависимости от выполнения (или невьшолнерия) которого возможен переход к той или иной подпрограмме управления. При поступлении на вход 28 контроллера кода логического условия на выходе мультиплексору 9 логических условий будет либо сигнал логического нуля (если проверяемое условие не вьшолнено), либо сигнал логической единицы (если условие выполнено). При этом постоянная часть адреса дополняется либо нулем,- либо единицей в зависимости от выполнения логического условия. Метка-признак окончания подпрограммы с выхода регистра 5 поступает на управляющий вход мультиплексора 8 адре са и производит запись сформированного адреса очередной подпрограммы управления в регистр 3 адреса. Выполнение очередной подпрограммы осуществляется описанным ранее способом

С вьщачей последнего импульса программы управления с выхода поля 2„3 -запоминающего блока 2 выдается меткапризнак (М|) конца работы Эта метка поступает на нулевые входы триггера 11 пуска и триггера 13 останова, ко торые после перехода к нулевое состоние запрещают вьщачу и прохождение тактовых импульсов. Устройство готово к выполнению очередной програм1-1ы управления

Таким образом, предложенный программируемый контроллер позволяет расширить область его использования следующим образом, так как позволяет вьщавать программу управления в зависимости от внешних условий (условий объекта управления)., что повышает гибкость управления (на основе адаптации к внешним условиям и переходу в зависимости от них к выполнению той или иной подпрограммы). Во время выдачи одного длинного управляющего сигнала, выдаваемого с одног выхода контроллер позволяет производить выдачу нескольких коротких управляющих сигналов с другого йы хода или выходов. Это значительно

повьш.1ает быстродействие как самого контроллера, так и системы в целом. Быстродействие контроллера повышается благодаря .тому, что расширение функциональных возможностей приводит к совмещению времени выборки из памяти очередной команды управления со временем вьшолнения предыдущей команды, а также тем обстоятельством, что моменты окончания одних сигналов управления могут задаваться началом вьшолнения других сигналов При этом вьщача третьих управляющих сигналов модет сохраняться. Возможность в момент окончания одних сигналов начинать выполнение других сигналов в каждом такте дает выигрьш во времени равный времени выборки информации из памяти Поэтому повышение быстродействия объекта управления, например станка с числовым программным управлением, достигается широкими функциональными возможностями программируемого контроллера.

Ф.ормула изоб.ретения

Программируемый контроллер, содержащий первый-и второй запоминающие блоки5 триггер пуска, генератор тактовых импульсов, элементы согласования, мультиплексор адреса, реги-стр адреса, счетчик адреса, дешифратор, регистр памяти, формирователь импульса, счетчик, элемент И, причем информационные входы контроллера соединены с входами элементов согласования,- выходы которых соединены с перв1з1ми информационными входами мультиплексора адресаJ выход мультиплексора адреса соединен с входом реги-в стра адреса, выход регистра адреса и счетчика адреса соедине51Ы с вxoдa sи дешифратора, выходы которого соединены с входами первого и второго запоминающих блоков, выход первого запоминающего блока соединен с входом регистра памяти, выход первого поля второго запоминающего блок соединен с информационным входом счечика , первый управляющий вход контроллера соединен с единичным входом триггера пускаj единичньй выход которого соединен с управляющим входом генератора тактовых импульсов, выход г енератора тактовых импульсов соединен с первым входом элемента И, выход которого соединен с вычитающим

входом счетчика, отличающийс я тем, что, с целью расширения функциональных возможностей путем формирования произвольных длин управляющих сигналов, контроллер дополнительно содержит триггер управления, триггер останова, выходной регистр, мультиплексор логических условий, второй, третий и четверть элементы И, три элемента ИЛИ, два элемента задержки и элемент НЕ, причем второй управляющий вход контроллера соединен с первым управляющим входом мультиплексора адреса, с единичным входом триггера останова и первым входом первого элемента ИЛИ, выход которого соединен с единичным входом триггера управления, единичный выход триггера управления соединен с входом формирователя импульсов,-выход которого соединен с первым входом второго элемента И, выход второго элемента И соединен с входом установки в нуль выходного регистра и регистра памяти, выход генератора тактовых импульсов. соединен с первым входом третьего элемента И, выход которого соединен с первым входом четвертого элемента И и входом первого элемента задержки, выход первого элемента за- держки соединен с нулевьм входом триггера управления,, нулевой выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с синхронизирующим входом дешифратора и входом второго элемента задержки, выход второго элемента задержки соединен со счетным входом

счетчика адреса, единичный выход тригера останова соединен с вторым входом третьего элемента И, выход кода проверяемых логических условий регистра памяти соединен с первым информационным входом мультиплексора логических условий, второй информационный вход контроллера соединен с вторым информационным входом мультиплексора логических условий, выход которого соединен с первым входом второго элемента ИЛИ, выход модифицируемого разряда регистра памяти соединен с вторым входом второго элемента ИЛИ, выход немодифицируемого кода адреса регистра памяти соединен с вторым информационным входом мультиплексора, выход второго элемента ИЛИ соединен также с вторым информационным входом мультиплексора, выходы второго поля второго запоминающего блока соединены с счетными входами выходного регистра, йыходы которого являются выходами контрол- лерар управляющий выход второго запоминающего блока соединен с нулевыми входами триггера пуска и триггера останова, единичные выходы счетчика соединены с входами третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и входом элемента НЕ, выход элемента НЕ соединен с вторым входом второгоэлемента И и третьим входом третьего элемента И, управлякнций разряд выходного регистра.соединен с вторым входом первого элемента ИЛИ и вторьм управляющим входом мультиплексора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1481759A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для коррекции программ | 1990 |

|

SU1751768A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для программного управления | 1990 |

|

SU1784939A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение при построении систем программной коммутации и для управления технологическими Процесca iи. Решается задача расширения функциональных возможностей программируемого контроллера путем совмещения процесса выборки информации из памяти с временем вьдачи управляющих сигналов, а также путем формирования сигналов произвольно : длительности. С первых информащюнных входов контроллера через элементы согласования на информационные входы мультиплексора адреса поступает код адреса первой подпрограммьь Одновременно на управляющий вход мультиплексора адреса поступает сигнал Начало работы. Импульс с выхода генератора тактовых импульсов, пройдя через третий rf четвертый элементы И, поступает на синхронизирующий вход дешифратора адреса и производит выборку информации из первого и второго запоминающих блоков. Операционная часть команды из второго запоминающего блока поступает в выходной регистр. Одновременно сигнал с выхода четвертого элемента И через второй элемент задержки поступает на счетный вход счетчика адреса и увеличивает его содержимое. Код простоя контроллера поступает на входы счетчика и через третий элемент 1-ШИ разрешает прохождение импульсов так-: тового генератора на вычитающий вход счетчика через первый элемент И. сле вьщержки времени простоя и обнуления счетчика разрешается прохождение тактовых импульсов через третий элемент И. При поступлении на второй информац11онный вход контроллера кода логического условия на выходе мультиплексора логических условий появляется либо сигнал логичесsssim кого нуля, либо логической единицы. ю При этом постоянная часть адреса до05 солняется либо нулем, либо единицей. Ю rf Метка - признак окончания программы с выхода выходного регис тра поступает на второй управляющий вход мультиплексора адреса и записывает сформированный адрес очередной подпрограм ы управления в регистр адреса. При поступлении метки-признака конца работы из второго запоминающего блока триггеры пуска и останова переводятся в нулевое состояние и запрещает про:хождение тактовых импульсов. З.ил.

Фиг. 2

| Программное временное устройство | 1976 |

|

SU647655A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ управления процессом прессования порошкового материала и устройство для его осуществления | 1987 |

|

SU1507537A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-10-07—Публикация

1984-10-10—Подача