Изобретение относится к автоматике и вычислительной технике и может быть использовано для деления последовательности входных импульсов ва ll Известен делитель частоты, который содержит в каждом разряде триггер памяти и два коммутационных 14. Однако устройство требует большого количества оборудования, что ведет к увеличению его габаритов, веса, потребляемой мощности. Кремле того, оно ие осуществляет деление входной последовательности импульсов на 11. Наиболее близким к предлагаемому является устройство, содержащее четыре разряда, каждый из которых сс стонт из триггера памяти и коммутационного триггера, а три первых разряда и из элемента И-НЕ, причем в первых двух разрядах единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный выход которого соединен со входом элемента И-НЕ, а нулевой выход соединен с единичным входом триггера памяти, в третьем разряде нулевой выход триггера памяти соединен с единичным входом коммутационного триггера, а в четвертом разряде нулевой выход триг гера памяти соединен с нулевым входом колвлутационного триггера, нулевой выход коммутационного триггера второго разряда соединен с нулевыми входами триггера памяти и коммутационного триггера первого разряда и со входом элемента И-НЕ этого разряда, выход элемента И-НЕ третьего разряда соединен с единичным входом триггера памяти этого разряда, с нулевыми входами коммутационных триггеров, триггеров и со входами элементов И-НЕ всех предыдущих разрядов, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом триггера памяти четвертого разряда, с нулевыми входами триггеров памяти и ко1 1утационных триггеров всех млгщших разрядов и со входом элемента И-НЕ второго разряда, единичный выход коммутационного триггера четвертого разряда соединен с нулевыми входг1ми всех триггеров делителя, выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго разряда и со входом элемента И-НЕ третьего разряда, выход элемента И-НЕ второго разряда соединен с нулевым входом коммутационного триггера и со

входом элемента И-НЕ третьего разряда, а тактовая шина подключена к нулевьгм входам коммутационных триггеро первого, второго и третьего разрядов, к единичному входу коммутационного триггера четвертого разряда и входу элемента И-НЕ второго разряда 2 .

Однако известное устройство выполнено на большом количестве оборуд вания и обладает низкой надежностью. Цель изобретения - повышение надежности работы устройства.

Поставленная цель достигается тем что в делителе частоты на 11, содержащем четыре разряда, каждый из которых состоит из триггера памяти и коммутационного триггера, а три первых разряда и из элемента И-НЕ, выходы элементов И-НЕ первого и второго разрядов соединены с единичными входами кoм Iyтaциoннoгo триггера четвертого разряда, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом коммутационного триггера первого разряда, а единичный выход коммутационного триггера четвертого разряда соединен со входами элементов И-НЕ первого, второго и третьего разрядов,

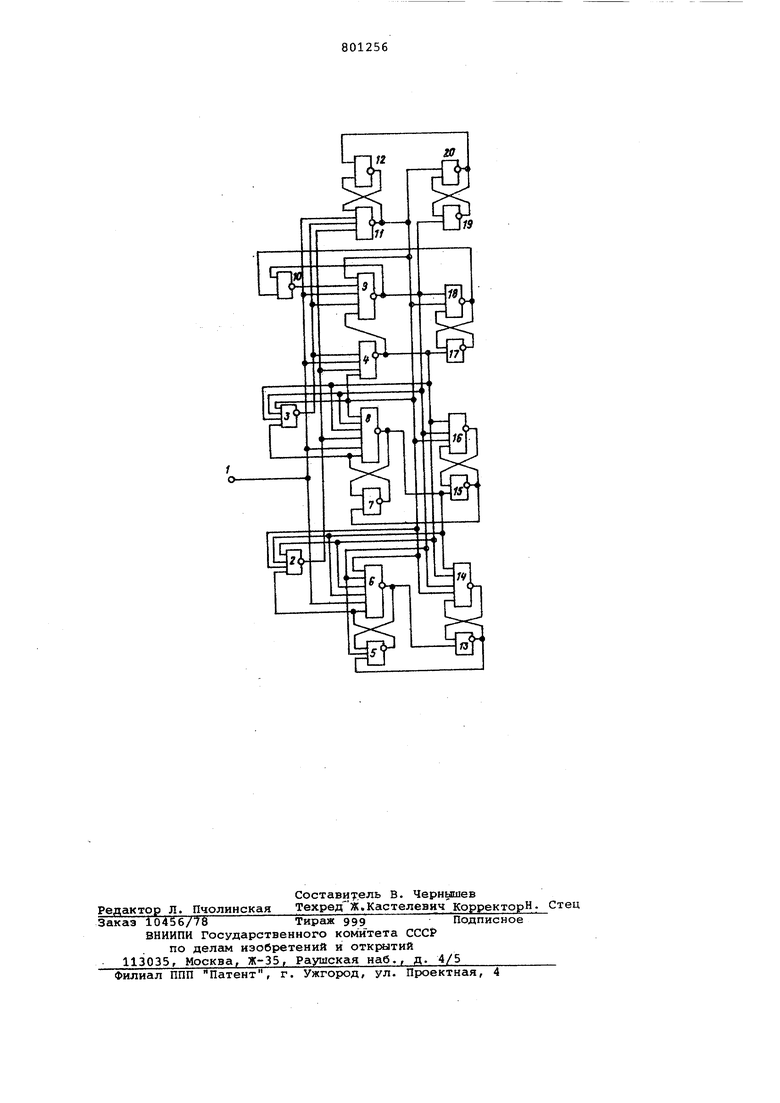

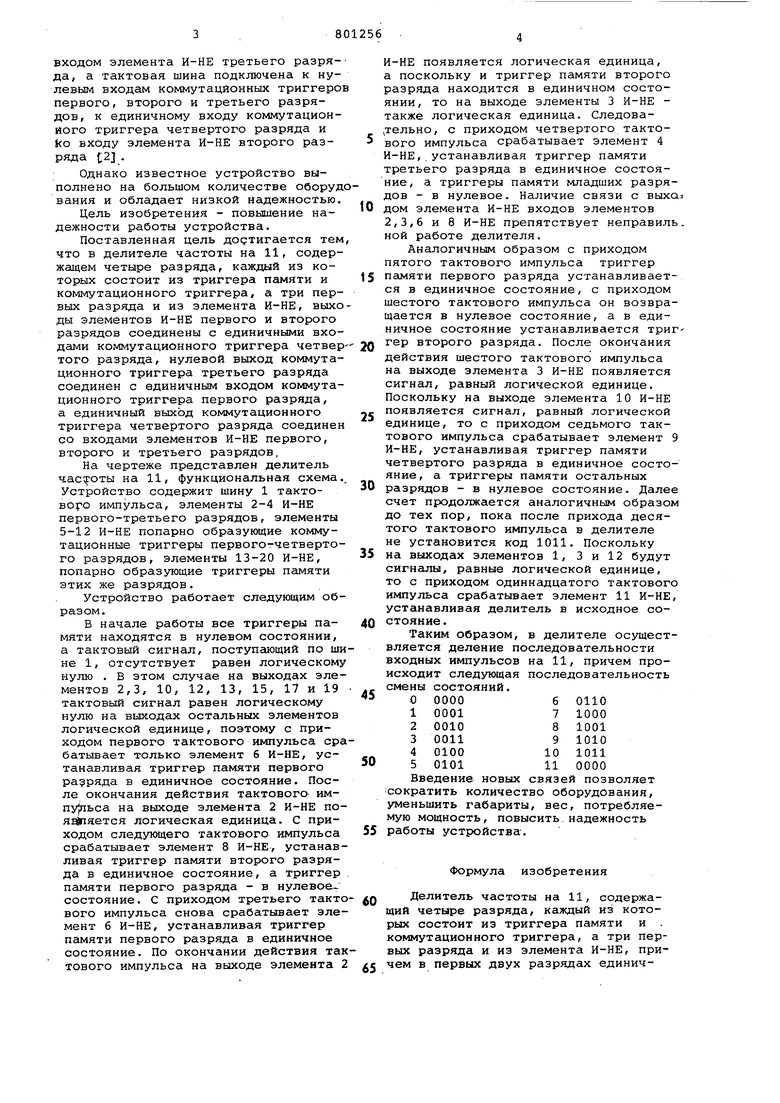

На чертеже представлен делитель частоты на 11, функциональная схема. Устройство содержит шину 1 тактоворо импульса, элементы 2-4 И-НЕ первого-третьего разрядов, элементы 5-12 И-НЕ попарно образующие коммутационные триггеры первого-четвертого разрядов, элементы 13-20 И-НЕ, попарно образующие триггеры памяти этих же разрядов.

Устройство работает следующим образом.

В начале работы все триггеры памяти находятся в нулевом состоянии, а тактовый сигнал, поступающий по шине 1, отсутствует равен логическому нулю . В этом случае на выходах элементов 2,3, 10, 12, 13, 15, 17 и 19 тактовый сигнал равен логическому нулю на выходах остальных элементов логической единице, поэтому с приходом первого тактового импульса срабатывает только элемент 6 И-НЕ, устанавливая триггер памяти первого разряда в единичное состояние. После окончания действия тактового- импу|пьса на выходе элемента 2 И-НЕ поян пяется логическая единица. С приходом следующего тактового импульса срабатывает элемент 8 И-НЕ, устанавливая триггер памяти второго разряда в единичное состояние, а триггер памяти первого разряда - в нулевоесостояние. С приходом третьего тактового импульса снова срабатывает элемент б И-НЕ, устанавливая триггер памяти первого разряда в единичное состояние. По окончании действия тактового импульса на выходе элемента 2

И-НЕ появляется логическая единица, а поскольку и триггер памяти второго разряда находится в единичном состоянии, то на выходе элементы 3 И-НЕ также логическая единица. Следова тeльнo, с приходом четвертого тактового импульса срабатывает элемент 4 И-НЕ, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти младших разрядов - в нулевое. Наличие связи с выхаз

0 дом элемента И-НЕ входов элементов

2,3,6 и В И-НЕ препятствует неправиль. ной работе делителя.

Аналогичным образом с приходом пятого тактового импульса триггер

5 Пс1мяти первого разряда устанавливается в единичное состояние, с приходом шестого тактового импульса он возвращается в нулевое состояние, а в единичное состояние устанавливается тригQ гер второго разряда. После окончания действия шестого тактового импульса на выходе элемента 3 И-НЕ появляется сигнал, равный логической единице. Поскольку на выходе элемента 10 И-НЕ

е появляется сигнал, равный логической единице, то с приходом седьмого тактового импульса срабатывает элемент 9 И-НЕ, устанавливая триггер памяти четвертого разряда в единичное состояние, а триггеры памяти остальных

0 разрядов - в нулевое состояние. Далее счет продолжается аналогичным образом до тех пор, пока после прихода десятого тактового импульса в делителе не установится код 1011. Поскольку

5 на выходах элементов 1, 3 и 12 будут сигналы, равные логической единице, то с приходом одиннадцатого тактового импульса срабатывает элемент 11 И-НЕ, устанавливая делитель в исходное состояние.

Таким образом, в делителе осуществляется деление последовательности входных импульсов на 11, причем происходит следующая последовательность смены состояний.

О 00006 ОНО

100017 1000

200108 1001

3ООН9 1010

40100 10 1011 0 5 0101 11 0000

Введение новых связей позволяет сократить количество оборудования, уменьшить габариты, вес, потребляемую мощность, повысить.надежность 5 работы устройства.

Формула изобретения

Q Делитель частоты на 11, содержащий четыре разряда, каждый из которых состоит из триггера памяти и . коммутационного триггера, а три первых разряда и из элемента И-НЕ, чем в первых двух разрядах единичный выход триггера памяти соединен с единичным входом коммутационного рриггера, единичный выход которого соединен со входом элемента И-НЕ, а. нулевой выход соединен с единичным входом триггера памяти, в. третьем разряде нулевой выход триггера пзмяти соединен с единичным входом коммутационного триггера, а в четвертом разряде нулевой выход триггера памяти соединен с нулевьш входом коммутационного триггера, нулевой выход коммутационного триггера второго разряда соединен с нулевыми входами триггера памяти и коммутационного триггера первого разряда и со входом элемента И-НЕ этого разряда, выход элемента И-НЕ третьего разряда соединен с единичным входом триггера пг1мяти этого разряда, с нулевыми входами коммутационных триггеров, триггеров памяти и со входами элем йтов И-НЕ всех предьадущих разрядов, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом триггера памяти четвертого разряда, с нулевыми входами триггеров памяти и коммутационных триггеров всех младших разрядов и со входом элемента И-НЕ второго разряда, единичный выход коммутационного триг гера четвертого разряда оединен с нулевыми входами всех триггеров делителя, выход элемента И-НЕ первого

разряда соединен с нулевым входом коммутационного триггера второго разряда и со входом элемента И-НЕ третьего разряда, выход элемента И-НЕ второго разряда соединен с нулевым f входом коммутационного триггера и со входом элемента И-НЕ третьего разряда, а тактовая шина подключена к нулевым входам коммутационных триггеров первого, второго и третьего раэ рядов, к единичному входу коммутационного триггера четвертого разряда и ко входу элемента И-НЕ второго разряда, отличающийся тем, что, с целью повьииения надежности работы устройства, выходы элементов

5 И-НЕ первого и второго разрядов соединены с единичнЕл и входами коммутационного триггера четвертого разряда, нулевой выход коммутационного триггера третьего разряда соединен

0 с единичным входом коммутационного триггера первого разряда, а единичный выход коюлутационного триггера четвертого разряда соединен со входами элементов И-НЕ первого, второго

5 и третьего разрядов.

Источники инфор «1ации, принятые во внимание при экспертизе

1. Авторскоесвидетельство СССР № 444330, кл. Н 03 К 23/00, 1971

2. Авторское свидетельство СССР

по заявке 2528043, кл. Н 03 К 23/02, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты импульсов на двенадцать | 1977 |

|

SU733110A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты импульсов | 1979 |

|

SU843247A2 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

Авторы

Даты

1981-01-30—Публикация

1979-01-26—Подача