1325709 Изобретение относится к информационно-измерительной технике и предназначено для преобразования унитарного кода в двоичный позиционный код параллельного и последовательного типов. Цель изобретения - упрощение преобразователя.

На фиг.1 приведена функциональная

ший разряд в единичное, а все младшие в нулевое состояние), На адресных входах мультиплексора 2 устанавливается двоичный номер 16-го разряда унитарного кода, и значение этого разряда поступает через ъгультиплек- сор 2 на информационный вход регистра 3. В момент Ц и тактовому импуль- схема преобразователя; на фиг.2 -вре-ю су г с выхода мультиплексора 2 считы- менные циаграммы, поясняющие его работу.

Преобразователь содержит первый регистр 1 сдвига, мультиплексор 2, второй регистр 3 последовательного приближения, D - триггер 4 и такто- вьй генератор 5, выполненный на элементе НЕ 6, элементах И 7 и 8, элементе НЕ 9, резисторах 10-13 и конденсаторах 14 и 15.

Устройство работает следующим образом.

На входы регистра 1 поступает (2 -1)-разрядный унитарный код, котовается значение старшего разряда последовательного двоичного результата, а по импульсу в это значение заносится в старший разряд регистра 3 и од15 новременно его более младший разряд устанавливается в единичное состояние. Таким образом, если значение 16-го разряда унитарного кода равно нулю, .а значит и все более старшие

20 разряды в унитарном коде равны нулю, то на адресных входах мультиплексора 2 формируется двоичный номер 8-го разряда (01000) или, в противном случае, номер 24-го разряда унитар35

40

pbrii заносится в него по строб-импуль- 25 ного кода (ГЮОО), т.е. на адресных су а, поступающему на тактовый вход регистра 1 от источника запускающего сигнала. Одновременно, строб-импульсом а триггер 4 устанавливается в единичное состояние и разрешает вы- ЗО работку тактовых импульсов в и г на первом и втором выходах генератора 5, период частоты следования которых равен времени суммарной задержки сигналов в мультиплексоре 2 и регистре 3. По тактовым импульсам на выходе регистра 3 формируется последовательность двоичных чисел, которые одновременно являются адресами разрядов регистра 1. В соответствии с поступившим адресом логический сигнал выбранного разряда проходит через мультиплексор 2 на информационный вход регистра 3. Это позволяет осуществить преобразование входного унитарного ()-разрядного кода в двоичный код по алгоритму последовательного приближения за Р тактов с представлением результата в последовательной форме на выходе мультиплексора 2 и в параллельной форме на выходах регистра 3.

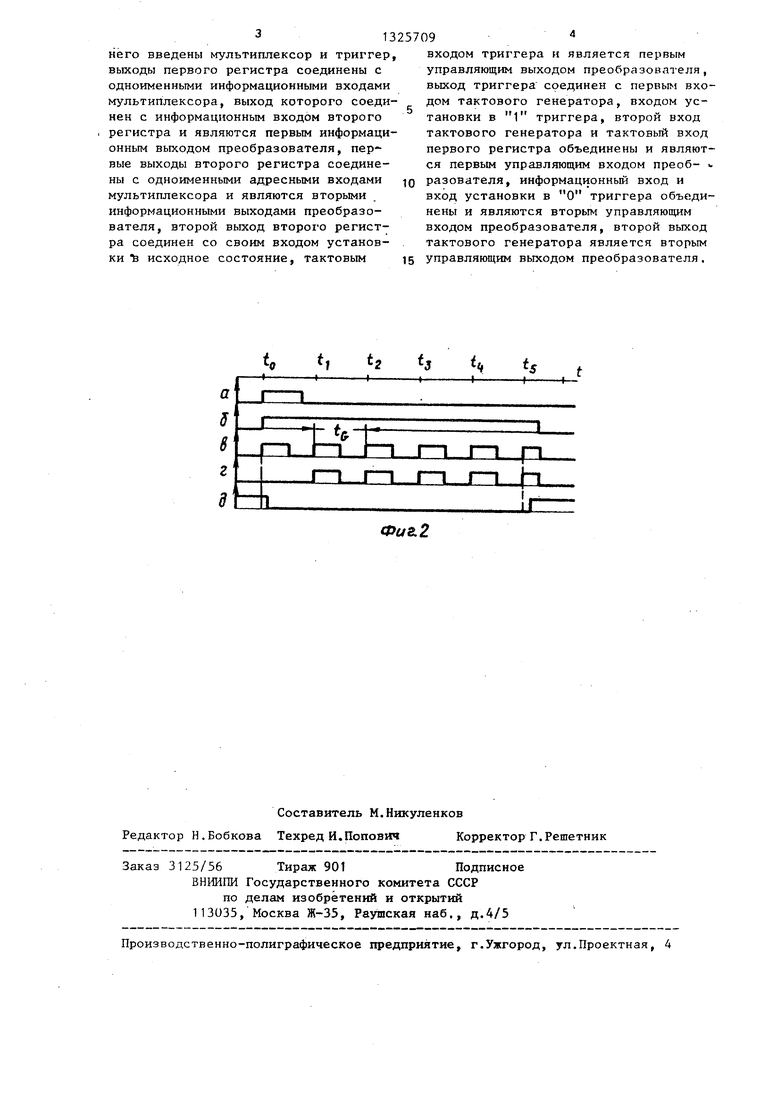

Временные диаграммы (фиг.2) поясняют работу преобразователя на примере преобразования 31-разрядного унитарного кода в 5-разрядный двоичный код. В .момент t по тактовому

45

входах мультиплексора 2 формируется последовательность номеров коммутируемых разрядов унитарного кода в зависимости от их значений по алгоритму последовательного приближения. Это обеспечивает формирование в моменты t на выходе мультиплексора 2 значений разрядов последовательного двоичного кода, где ,2,..., , а в момент t р - параллельного двоичного кода на выходах регистра 3.

Преобразователь 255-т)азрядного унитарного кода в 8-разрядный двоичный код реализован на интегральных микросхемах 155 и 531 серий; регистр последовательного приближения типа К155ИР17, мультиплексор типа К155КП1. Число внутрисхемных связей не превысило величины триста, а время на получение 8-разрядного двоичного кода в последовательной и параллельной формах составляет 800 не.

Формула изобретения

50

Преобразователь унитарного кода в двоичный позиционный,код, содержащий первый регистр, информационные входы которого являются информационными вхо- дами преобразователя, и тактовый генератор, первьй выход которого соединен с тактовым входом второго регистра, отличающийся тем, что, ся в исходное состояние lOOOOj (стар- с целью упрощения преобразователя, в

импульсу в регистр 3 устанавливает9

ший разряд в единичное, а все младшие в нулевое состояние), На адресных входах мультиплексора 2 устанавливается двоичный номер 16-го разряда унитарного кода, и значение этого разряда поступает через ъгультиплек- сор 2 на информационный вход регистра 3. В момент Ц и тактовому импуль- су г с выхода мультиплексора 2 считы-

вается значение старшего разряда последовательного двоичного результата, а по импульсу в это значение заносится в старший разряд регистра 3 и одновременно его более младший разряд устанавливается в единичное состояние. Таким образом, если значение 16-го разряда унитарного кода равно нулю, .а значит и все более старшие

разряды в унитарном коде равны нулю, то на адресных входах мультиплексора 2 формируется двоичный номер 8-го разряда (01000) или, в противном случае, номер 24-го разряда унитар

ного кода (ГЮОО), т.е. на адресных

входах мультиплексора 2 формируется последовательность номеров коммутируемых разрядов унитарного кода в зависимости от их значений по алгоритму последовательного приближения. Это обеспечивает формирование в моменты t на выходе мультиплексора 2 значений разрядов последовательного двоичного кода, где ,2,..., , а в момент t р - параллельного двоичного кода на выходах регистра 3.

Преобразователь 255-т)азрядного унитарного кода в 8-разрядный двоичный код реализован на интегральных микросхемах 155 и 531 серий; регистр последовательного приближения типа К155ИР17, мультиплексор типа К155КП1. Число внутрисхемных связей не превысило величины триста, а время на получение 8-разрядного двоичного кода в последовательной и параллельной формах составляет 800 не.

Формула изобретения

iero введены мультиплексор и триггер, выходы первого регистра соединены с одноименными информационными входами мультиплексора, выход которого соединен с информационным входом второго регистра и являются первым информационным выходом преобразователя, пер- вые выходы второго регистра соединены с одноименными адресными входами мультиплексора и являются вторыми информационными выходами преобразователя, второй выход второго регистра соединен со своим входом установки исходное состояние, тактовым

to 2 J 5 t

входом триггера и является первым управляющим выходом преобразователя, выход триггера соединен с первым входом тактового генератора, входом установки в 1 триггера, второй вход тактового генератора и тактовый вход первого регистра объединены и являются первым управляющим входом преоб- «.

разователя, информационный вход и вход установки в О триггера объединены и являются вторым управляющим входом преобразователя, второй выход тактового генератора является вторым

управляющим выходом преобразователя.

Фиё,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Многоканальный формирователь кодов | 1984 |

|

SU1228288A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Преобразователь кодов | 1987 |

|

SU1444957A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

Изобретение относится к информационно-измерительной технике и предг назначено для преобразования унитарного кода в двоичный позиционный код. Изобретение позволяет упростить преобг разователь. Преобразование унитарного в двоичный код осуществляется по алгоритму последовательного приближения с представлением результата в последовательной и параллельной формах. Преобразователь содержит регистр 1 сдвига, мультиплексор 2, регистр 3 последовательного приближения, триггер 4 и тактовый генератор 5, выполненный на элементах НЕ 6 и 9, элементах И 7 и 8, резисторах 10-13 и конденсаторах 14 и 15. 2 ил. с & (Л ft.f.. со СЛ VI О Фиг.1

| Устройство для преобразования кодов | 1982 |

|

SU1078613A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА В ЦИКЛИЧЕСКИЙ С ПОСТОЯННЫМ ЧИСЛОМ П ЕДИНИЦ ИЗ р | 0 |

|

SU404078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-10—Подача