Изобретение относится к технике радиосвязи и может использоваться в радиоприемниках, имеющих несколько режимов приема дискретной информации

Цель изобретения - повьшение достоверности приема.

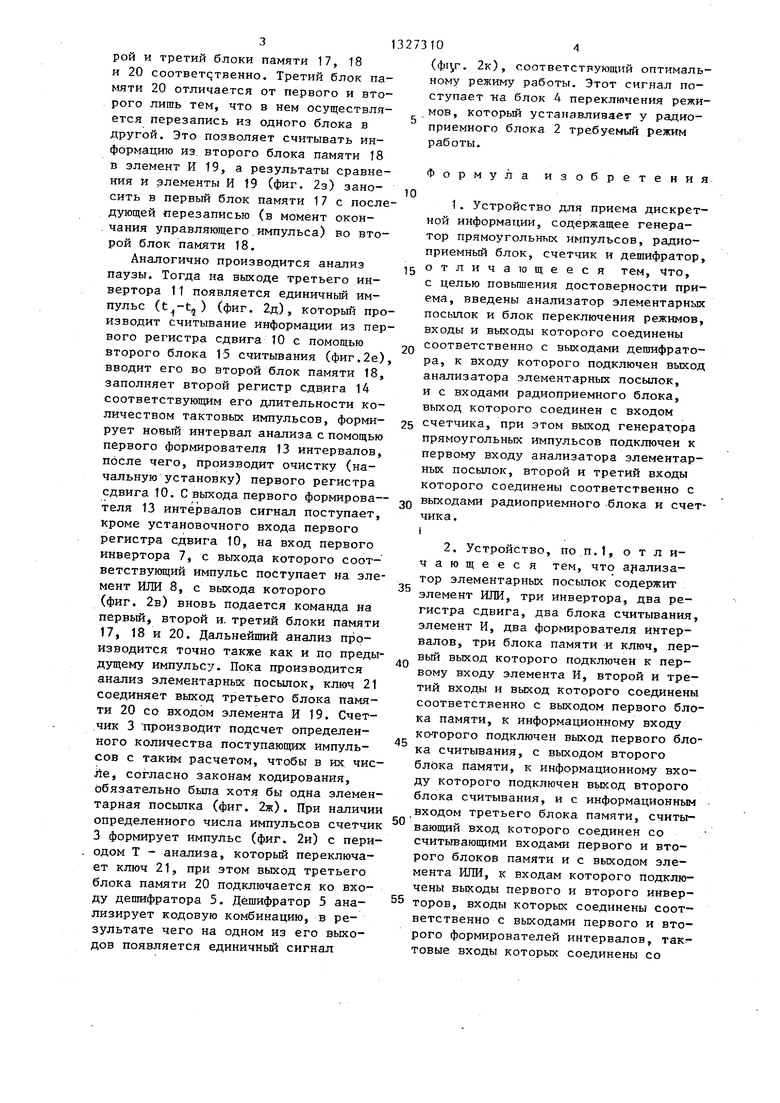

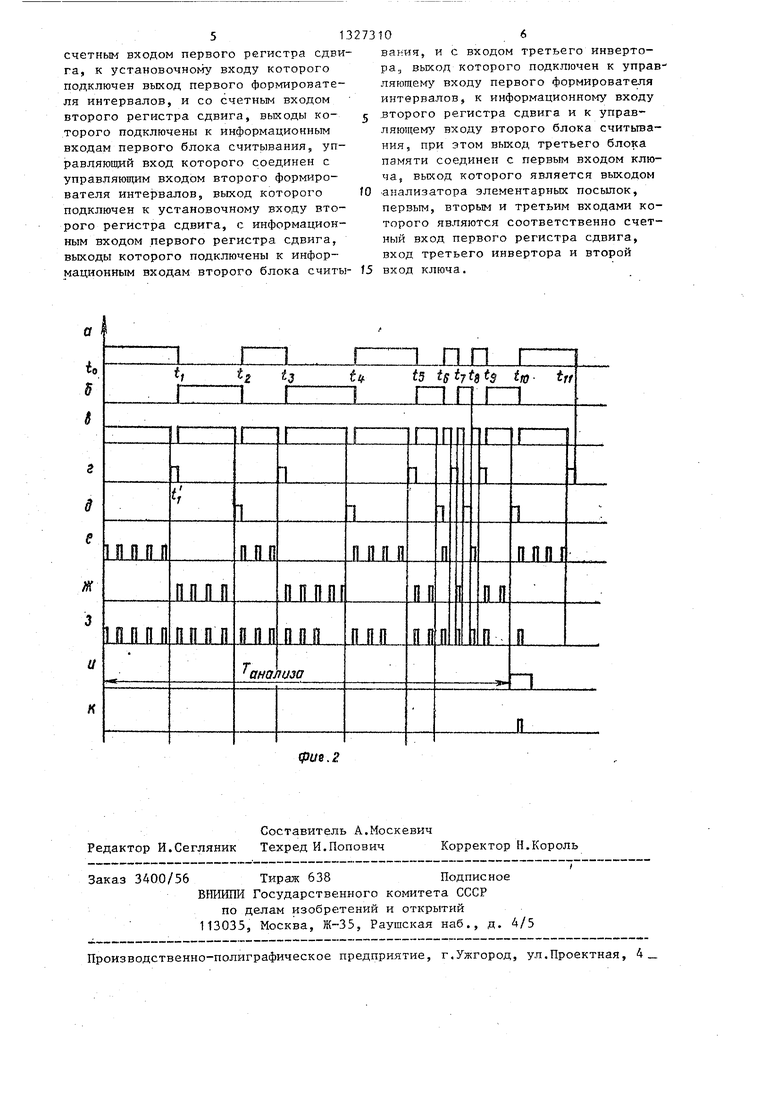

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - эпюры напряжений, поясняющие его работу.

Устройство для приема дискретной информации содержит генератор 1 прямоугольных импульсов, радиоприемный блок 2, счетчик 3, блок 4 переключения режимов, дешифратор 5, анализатор 6 элементарных посылок, состоящий из первого инвертора 7, элемента РШИ 8, второй инвертор 9, первый регистр сдвига 10, третий инвертор 1 первый блок 12 считывания, первый формирователь 13 интервалов, второй регистр сдвига 14, второй блок 15 считывания, второй формирователь 16 интервалов, первый и второй блоки памяти 17 и 18, элемент И 19, третий блок памяти 20 и ключ 21.

Устройство работает следующим образом.

На передающем конце (не показанном на фиг. 1) радиолинии информаци- онньш сигнал, состоящий из совокупности одиночных, двойных, тройных и других импульсов, как результат физической реализации двоичной кодовой :последовательности, поступает в передающее устройство, преобразуется в высокочастотный дискретньш сигнал и излучается в пространство. В момент начала приема дискретной информации радиоприемный блок 2 находится в режиме, обеспечивающем прием при наихудших условиях передачи и параметрах излученного сигнала. Для установления оптимального режима работы радиоприемного блока 2 информация с его выхода в виде элементарных посылок (прямоугольных импульсов) поступает на оконечную аппаратуру (не показанную на фиг.1), счетчик 3 и анализатор 6 элементарных посылок. При этом, генератор 1 прямоугольньк импульсов тактирует работу анализатора 6 элементарных посылок. Длительность тактового импульса может быть вдвое или иное кратное число раз меныйе длительности элементарной посыпки для режима с наибольшей скоростью передачи информации. Чтобы

5

0

устранить оптимальный режим работы радиоприемного блока 2, Необходимо определить дл-ительность наименьшего, т.е, одиночного импульса, иными словами, минимального из принимаемых. Для этого используется анализатор 6 элементарных посылок со второго информационного входа которого, подключенного к выходу радиоприемного блока 2, принимаемые импульсы подаются на первый регистр сдвига 10 для анализа и на третий инвертор 11 для инвертирования пауз с целью сокращения интервала анализа в случае передачи информации с активной паузой. Таким образом, анализатор б элементарных посылок производит измерение длительности импульсов и пауз. Для измерения длительности импульс стробирует- ся тактовыми импульсами с генератора 1, поступающими на счетный вход первого регистра сдвига 10 при наличии импульса или второго регистра сдвига 14 при наличии паузы. При этом, пауза после третьего инвертора 11 преобразуется в прямоугольный импульс. Для определения минимального импульса производится сравнение каждого последующего импульса с пре- . дьщущим. Процесс вьщеления наименьшего импульса из принимаемой кодовой последовательности наглядно представлен на фиг. 2. Первый импульс (фиг. 2а) поступает на первый регистр сдвига 10, в ячейку которого за время существования импульса (.) запишутся несколько единиц, соответствующих количеству тактовых Iимпульсов, поступивших за это время на его счетный вход. Этот единичный импульс на выходе третьего инвертора 11 отсутствует (фиг. 26), а при поступлении на второй формирователь 16 интервалов формирует импульс дли5

0

5

5

0

5

тельностью (фиг. 2 г). Кроме того, он производит считывание кодовой комбинации (количества изначаль-. но введенных тактовых импульсов) с помощью первого блока 12 считывания из ячеек второго регистра сдвига 14. Эта кодовая комбинация записывается- в первый блок памяти 17. Короткий импульс с выхода второго формирователя 16 интервалов поступает на второй инвертор 9, затем на смеситель, выполненный в виде элемента ИЛИ 8, с вьпсода которого управляющий в сигнал (фиг, 2в) поступает на первый, вто

31

рой и третий блоки памяти 17, 18 и 20 cooTBeTqTBeHHo. Третий блок памяти 20 отличается от первого и второго лишь тем, что в нем осуществляется перезапись из одного блока в другой. Это позволяет считывать информацию из второго блока памяти 18 в элемент И 19, а результаты сравнения и элементы И 19 (фиг. 2з) зано- сить в первый блок памяти 17 с последующей перезаписью (в момент окон- . чания управляющего.импульса) во второй блок памяти 18.

Аналогично производится анализ паузы. Тогда на выходе третьего инвертора 11 появляется единичньй импульс (t -tj) (фиг. 2д), которьш производит считывание информации из первого регистра сдвига 10 с помощью второго блока 15 считывания (фиг.2е) вводит его во второй блок памяти 18, заполняет второй регистр сдвига 14 соответствующим его длительности количеством тактовьк импульсов, форми- рует новый интервал анализа с помощью первого формирователя 13 интервалов, после чего, производит очистку (начальную установку) первого регистра сдвига 10. С выхода первого формирова- теля 13 интервалов сигнал поступает, кроме установочного входа первого регистра сдвига 10, на вход первого инвертора 7, с выхода которого соот- ветствующий импульс поступает на элемент ИЛИ 8, с выхода которого (фиг. 2в) вновь подается команда на первый, второй и. третий блоки памяти 17, 18 и 20. Дальнейший анализ производится точно также как и по предыдущему импульсу. Пока производится анализ элементарных посылок, ключ 21 соединяет выход третьего блока памяти 20 со входом элемента И 19. Счетчик 3 производит подсчет определенного количества поступающих импульсов с таким расчетом, чтобы в их чис- rte, согласно законам кодирования, обязательно была хотя бы одна элементарная посылка (фиг. 2ж). При наличии определенного числа импульсов счетчик 3 формирует импульс (фиг. 2и) с периодом Т - анализа, который переключает ключ 21, при этом выход третьего блока памяти 20 подключается ко входу дешифратора 5. Дешифратор 5 анализирует кодовую комбинацию, в результате чего на одном из его выходов появляется единичньй сигнал

5

73

Q

5 р

5

0

0

5

Ш4

(. 2к), соответствующий оптимальному режиму работы. Этот сигнал поступает -на блок 4 переключения режимов, который устанавливает у радиоприемного блока 2 требуемый режим работы.

Формула изобретения

1.Устройство для приема дискретной информации, содержащее генератор прямоугольных импульсов, радиоприемный блок, счетчик и дешифратор, отличающееся тем, то,

с целью повышения достоверности приема, введены анализатор элементарных посыпок и блок переключения режимов, входы и выходы которого соединены соответственно с выходами дешифратора, к входу которого подключен выход анализатора элементарных посылок, и с входами радиоприемного блока, выход которого соединен с входом счетчика, при этом выход генератора прямоугольных импульсов подключен к первому входу анализатора элементарных посыпок, второй и третий входы которого соединены соответственно с выходами радиоприемного блока и счетчика. I

2.Устройство, по П.1, отличающееся тем, что арализа- тор элементарных посылок содержит элемент ИЛИ, три инвертора, два регистра сдвига, два блока считывания, элемент И, два формирователя интервалов, три блока памяти и ключ, первый выход которого подключен к первому входу элемента И, второй и третий входы и выход которого соединены соответственно с выходом первого блока памяти, к информационному входу которого подключен выход первого блока считывания, с выходом второго блока памяти, к информационному входу которого подключен выход второго блока считывания, и с информационным входом третьего блока памяти, считывающий вход Которого соединен со считывающими входами первого и второго блоков памяти и с выходом элемента ИЛИ, к входам которого подключены выходы первого и второго инверторов, входы которых соединены соответственно с выходами первого и второго формирователей интервалов, товые входы которых соединены со

513

счетным входом первого регистра сдвига, к установочному входу которого подключен выход первого формирователя интервалов, и со счетным входом второго регистра сдвига, выходы ко- торого подключены к информационным входам первого блока считывания, управляющий вход которого соединен с управляющим входом второго формирователя интервалов, выход которого подключен к установочному входу второго регистра сдвига, с информационным входом первого регистра сдвига, выходы которого подключены к информационным входам второго блока считы-

Cf

о S

6 S

д е

3

а

Фие.г

Составитель А.Москевич Редактор И.Сегляник Техред И.Попович Корректор Н.Король

Заказ 3400/56 Тираж 638Подписное

ВНИИЖ Государственного комитета СССР

по делан изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4„

10. 6

вания, и с входом третьего инвертора, выход которого подключен к управ ляющему входу первого формирователя интервалов, к информационному входу второго регистра сдвига и к управляющем входу второго блока считьгаа- ния, при этом выход третьего блока памяти соединен с первым входом ключа, выход которого является выходом анализатора элементарных посылок, первым, вторым и третьим входами которого являются соответственно счетный вход первого регистра сдвига, вход третьего инвертора и второй вход ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

| Тренажер радиотелеграфистов | 1983 |

|

SU1111194A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1427589A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Вторичные часы | 1976 |

|

SU651302A1 |

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

| Цифровой фазовый дискриминатор | 1979 |

|

SU801027A1 |

Изобретение относится к технике радиосвязи и повышает достоверность приема. Устр-во содержит генератор 1 прямоугольных импульсов, радиоприемный бункер 2, счетчик 3, дешифратор 5, инверторы 9 и 11, регистры 10 и 14 сдвига, блоки 12 и 15 считывания, формирователи 13 и 16 интервалов, блоки 17, 18, 20 памяти, эл-т И 19 и ключ 21. В устр-во введены блок 4 переключения режимов и анализатор 6 элементарных посьток. 1 з.п. ф-лы, 2 ил. СП со IvD

| Устройство для оптимального приемадиСКРЕТНОй иНфОРМАции B КАНАлАХ C пЕРЕ-ЕМННыМи пАРАМЕТРАМи | 1978 |

|

SU725538A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-07-30—Публикация

1986-03-06—Подача