1 13306322

Иэобрете)1ие относится к вычисли-на фиг.2 - временная диаграмма рательной технике и может быть исполь-боты.

зовано для масштабирования чисел вУстройство для масштабирования

вычислительных устройствах, работаю-чисел в системе остаточных классов

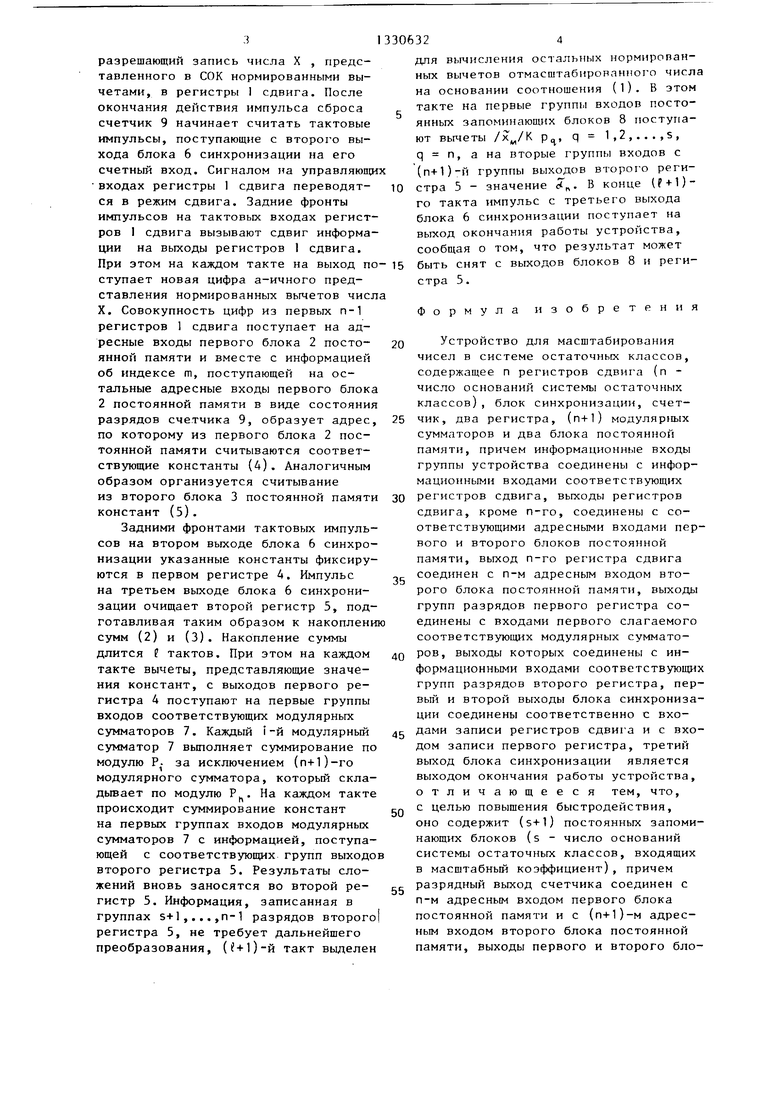

щих в непозиционной системе счисле-содержит (фиг.1) п регистров 1 сдвинип в остаточных классах (СОК), на-га, блоки 2 и 3 постоянной памяти,

пример в цифровых фильтрах и процес-регистры 4 и 5, блок 6 синхронизасорах быстрого преобразования Фурье,ции, (п+1) модулярных сумматоров 7,

использующих модулярную арифметику. (s+1) постоянных запоминающих блоЦель изобретения - повышение быс-ков 8, счетчик 9.

тродействия.Сущность работы устройства состоит

в следующем.

На фиг.1 представлена структурнаяНормированные вычеты результата

схема устройства для масштабированияis масштабирования определяются следуючисел в системе остаточных классов;щей формулой

|ХЗ/РЯ

н- 1оГ„ Р/К|р |р при

(1)

Х«/К1р + Р - 1(рп -oTjP /Klp lp при оГ гр„/2

1-1 где ) IZ F(x, ,...,х „., )| p,q 1 - п;(2)

f-1

m«0

h 1 Q(x,i ,...,Xm, Jl Р„;(3)

m(x,,х„ „., ) II (xn, ,. ..,х„ ., )1

Fjx, ,....x ,.J h L - х„, P;,./K|pq ;

Qm(i,1 ..m,J а ( Z. x .P,. );(5)

Ui

S

, s n- масщтабньш коэф- Блок 3 постоянной памяти содержит

фициент- константы О (x,,,),...,x,J. см. L лп формулу (5). Постоянные запоминающие X , х,,...х„ - нормированные выче- ,. а/ /

1 i 1-1-блоки о содержат значения /х./р , ты, кодированные в позиционной систе- . /,

см. формулу (и. ме счисления с основанием а:„ г, m т г т,

J Для случая Р, 03, Р 5, PJ

,К Р. ,а 2 блоки 2 и 3 имеют

Х- хД Х

. T7(j 45 кодировку, представленную в табл.1

X 1 X -Р I р.- 1 i п Кодировка блоков 8 по основаниям

-р/рр р-Пр. представлена соответственно

iff. / f п 1 л . О У

1 п ;.1 в табл.3 и 4.

L У а wane J «Блок 6 синхронизации формирует

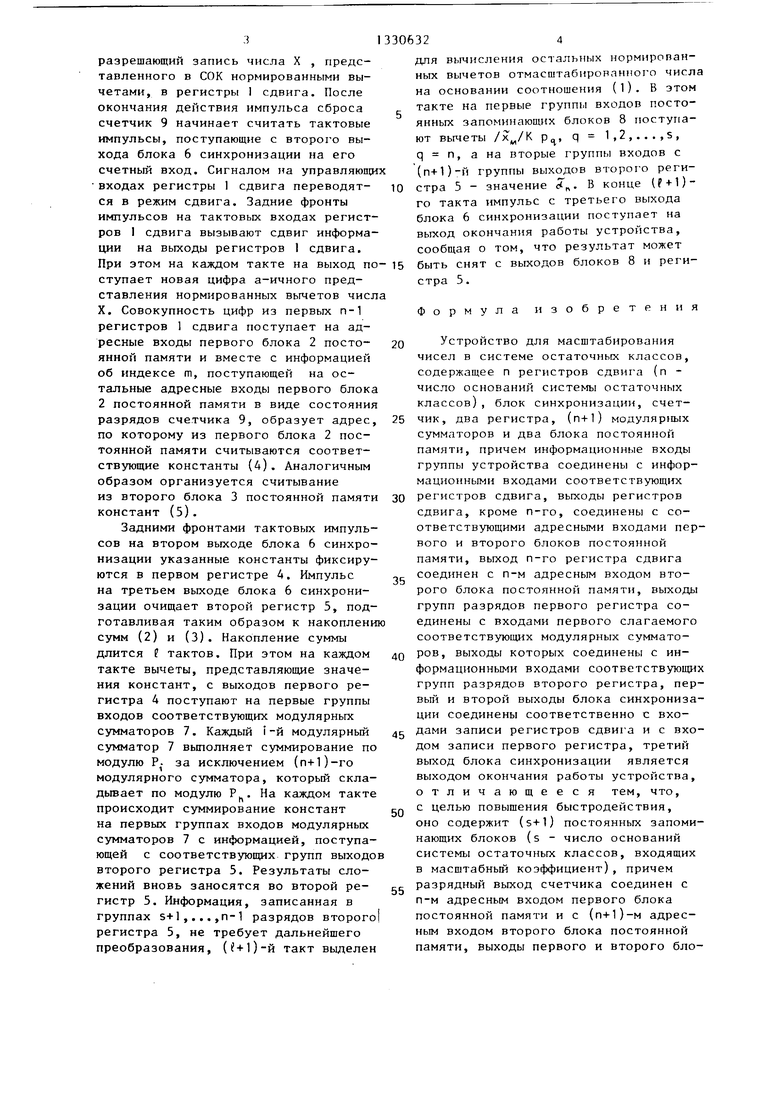

Р,. - основания СОК;на выходах импульсы согласно фиг.2.

- остатки по основаниям СОК. Устройство работает следующим

Следует отметить, что числа изобразом.

интервала (Р,()/2 - х J, Р/2) gg После включения питания импульсом

недопустимы.на первом выходе блока 6 синхронизаБлок 2 постоянной памяти содержитции счетчик 9 сбрасывается в нулевое

константы „(х ,...,х „, ), см.состояние. На управляющих входах

формулу (4).регистров 1 сдвига появляется сигнал.

разрешающий запись числа X , представленного в СОК нормированными выетами, в регистры 1 сдвига. После кончания действия импульса сброса счетчик 9 начинает считать тактовые импульсы, поступающие с второго выода блока 6 синхронизации на его счетный вход. Сигналом на управляющих входах регистры 1 сдвига переводят- ю ся в режим сдвига. Задние фронты импульсов на тактовых входах регистров 1 сдвига вызывают сдвиг информации на выходы регистров 1 сдвига.

ри этом на каждом такте на выход по- 15 быть снят ступает новая цифра а-ичного пред- стра 5. ставления нормированных вычетов числа . Совокупность цифр из первых п-1 регистров 1 сдвига поступает на адресные входы первого блока 2 посто- 20 НИНОЙ памяти и вместе с информацией об индексе т, поступающей на остальные адресные входы первого блока 2 постоянной памяти в виде состояния разрядов счетчика 9, образует адрес, 25 по которому из первого блока 2 постоянной памяти считываются соответствующие константы (4). Аналогичным образом организуется считывание из второго блока 3 постоянной памяти ЗО констант (5).

Задними фронтами тактовых импульсов на втором выходе блока 6 синхроизации указанные константы фиксирутся в первом регистре А. Импульс а третьем выходе блока 6 синхронизации очищает второй регистр 5, подготавливая таким образом к накоплению умм (2) и (3). Накопление суммы лится f тактов. При этом на каждом акте вычеты, представляюЕцие значеия констант, с выходов первого реистра 4 поступают на первые группы ходов соответствующих модулярных умматоров 7. Каждый i-и модулярный 45 умматор 7 вьшолняет суммирование по одулю Р. за исключением (п+1)-го одулярного сумматора, который скла- ьшает по модулю Р. На каждом такте

для вычисл ных вычето на основан такте на п янных запо ют вычеты q n, a н (п+1)-й гр стра 5 - з го такта и блока 6 си выход окон сообщая о

35

40

Форму

Устройс чисел в си содержащее число осно классов), чик, два р сумматоров памяти, пр группы уст мационными регистров сдвига, кр ответствую вого и вто памяти, вы соединен с рого блока групп разр единены с соответств ров, выход формационн групп разр вьм и втор ции соедин дами запис дом записи выход блок выходом ок отлич с целью по оно содерж нающих бло системы ос в масштабн разрядный п-м адресн постоянной ным входом памяти, вы

происходит суммирование констант на первых группах входов модулярных сумматоров 7 с информацией, поступающей с соответствующих групп выходов второго регистра 5. Результаты сложений вновь заносятся во второй регистр 5. Информация, записанная в группах s+l,...,n-1 разрядов второго регистра 5, не требует дальнейшего преобразования, ({+1)-й такт выделен

15 быть снят стра 5. 20 25 ЗО

306324

для вычисления остальных нормированных вычетов отмасштабиронанного числа на основании соотношения (1). В этом такте на первые группы входов посто- янных запоминающих блоков 8 поступают вычеты Pcj, q 1,2,.,.,s, q n, a на вторые группы входов с (п+1)-й группы выходов второго регистра 5 - значение d. В конце lf+1)- го такта импульс с третьего выхода блока 6 синхронизации поступает на выход окончания работы устройства, сообщая о том, что результат может

с выходов блоков 8 и реги5 быть снят стра 5. 0 5 О

5

5

0

0

5

Формула изобретения

Устройство для масштабирования чисел в системе остаточных классов, содержащее n регистров сдвига (п - число оснований системы остаточных классов), блок синхронизации, счетчик, два регистра, (n+l) модулярных сумматоров и два блока постоянной памяти, причем информационные входы группы устройства соединены с информационными входами соответствующ1тх регистров сдвига, выходы регистров сдвига, кроме п-го, соединены с соответствующими адресными входами первого и второго блоков постоянной памяти, выход п-го регистра сдвига соединен с п-м адресным входом второго блока постоянной памяти, выходы групп разрядов первого регистра соединены с входами первого слагаемого соответствующих модулярных сумматоров, выходы которых соединены с информационными входами соответствующих групп разрядов второго регистра, пер- вьм и второй выходы блока синхронизации соединены соответственно с входами записи регистров сдвига и с входом записи первого регистра, третий выход блока синхронизации является выходом окончания работы устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит (s+1) постоянных запоминающих блоков (S - число оснований системы остаточных классов, входящих в масштабный коэффициент), причем разрядный выход счетчика соединен с п-м адресньЕм входом первого блока постоянной памяти и с (п+1)-м адресным входом второго блока постоянной памяти, выходы первого и второго бло513

ков постоянной памяти соединены ср- ответственно с информационными входами групп разрядов первого регистра, выходы групп разрядов второго регистра соединены с входами второго ела- гаемого соответствующих модулярных сумматоров, выходы групп с первой по s-ю и п-й разрядов второго регистра соединены соответственно с первыми адресными входами постоянных запоминающих блоков, вторые адресные входы которых соединены с выходами ( группы разрядов второго реги- стра, выходы постоянных запоминающих блоков с первого по s-й, выходы групп (s-fl)-A по (п-1)-ю разрядов второго регистра и выход (s-bl)-ro постоянного запоминающего блока являются группой информационных выходов устройства, первьп выход блока синхронизации со- единен с входом сброса счетчика, счетный вход которого соединен с тактовыми входами регистров сдвига, с входом записи второго регистра и с вторым выходом блока синхронизации, третий выход которого соединен с входом сброса второго регистра, четвертый выход блока синхронизации соединен с входами разрешения сдвига регистров сдвига.

Таблица 1

о 1

о 1

о 1

о 1 о

00 00 00 00 01 01 01 01 10

о

2

1

о о 1 о

о

2 А 1

О 4 1 О О

Таблица 2

Т

Адресные входы

1 .г m,J

m

Выхо- -ДЬ

/Q../7 .

- е .i fO- п 15 о 20 25

О

о о

30 о

1

1

35

1

40

45

50

О О

о

1

.1

о о 1 1

о о 1 1

о о 1 I

о о 1 1

о 1

о 1

о 1 1 1

о 1

о I

о I

о 1

00

00

00

00

00

00

00

00

01

01

01

01

01

01

01

01

о 1 4 5 2 3

6 о о

2

1

3 4 6 5 О

55

13306328

Таблица 3

Вторая группа входов

iliillllilZri

О 1

2

О I

2 3 4 5 6

О 1

2 3

4 5 6

1

2 О

2 О 1

О 1 2

О 1 2

12

2О О 1

Таблица 4

3 4 5 6 О 1 2

1 2 3 4 5 6 О

6 О 1

2 3 4 5

4 5 6 О 1 2 3

2 3 4 5 6 О 1

i t/ Bxaff

Cxlpi X fff}pi

n

Ду/яб/гд

I I L

.xx JTJHJTJTJnjlJlJlJnJl..

.S/t. 1 fftr/xoff / S/f.S

2л7Х

n

Составитель А.Клюев Редактор М.Дылын Техред В.Кадар

3583/50

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

(2}pi

n

JT

,; йседс

n

rL

тта

иг,2

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для умножения чисел в непозиционной системе счисления | 1981 |

|

SU1015382A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1732353A1 |

| Устройство для масштабирования чисел | 1989 |

|

SU1667066A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

Изобретение относится к вычислительной технике, в частности к специализированным устройствам, работающим в непозиционной системе счисления в остаточных классах, и может быть использовано для масштабирования чисел в цифровых фильтрах и процессорах быстрого преобразования Фурье, использующих модулярную арифметику. Целью изобретения является повьш1ение быстродействия. Поставленная цель достигается тем, что в устройство для масштабирования чисел в системе остаточных классов, содержащее регистры 1 сдвига, блоки 2 и 3 постоянной памяти, регистры 4 и 5, блок 6 синхронизации, модулярные сумматоры 7 и счетчик 9, введены постоянные запоминающие блоки 8 с соответствующими связями. 2 ил. с (Л 00 со о о со N5 47Г

| УСТРОЙСТВО ДЛЯ ОКРУГЛЕНИЯ ЧИСЛА В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 0 |

|

SU398949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для масштабирования чисел в остаточной системе счисления | 1983 |

|

SU1140114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1987-08-15—Публикация

1986-02-11—Подача