Изобретение относится к вычислительной технике, в частности к устройствам контроля функциональных электрических узлов.

Цель изобретения - сокращение оборудования и повышение достоверности функционирования регистра сдвига с самоконтролем.

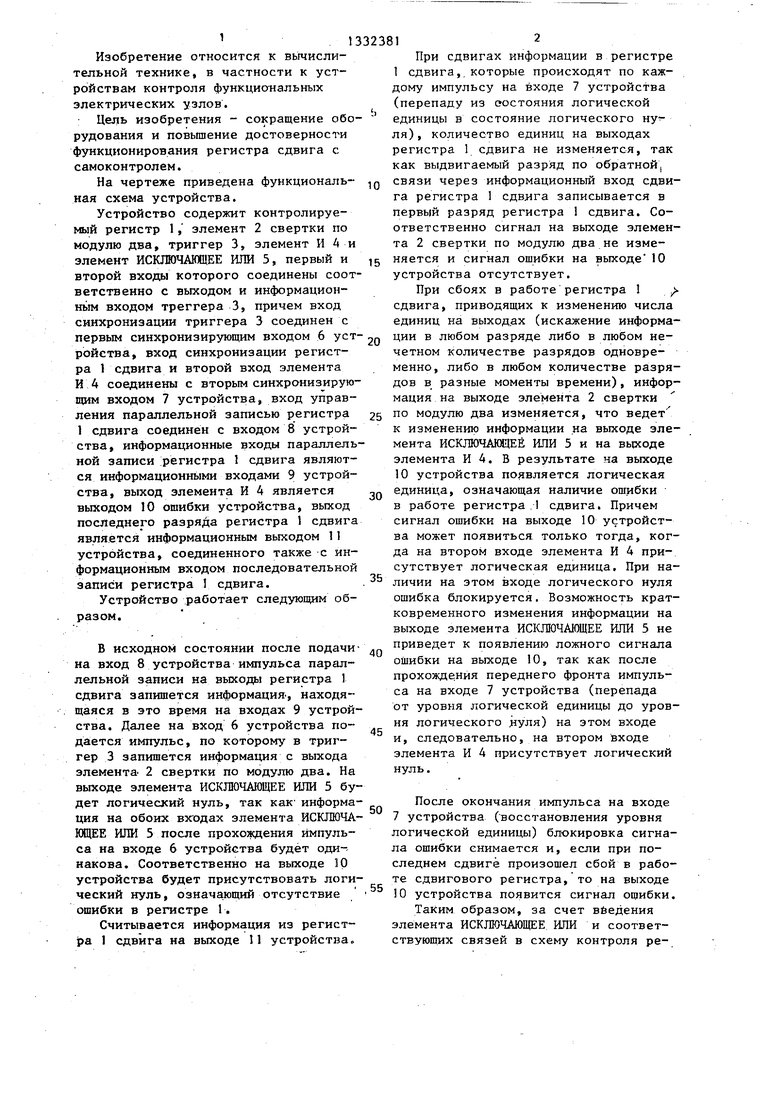

На чертеже приведена функциональная схема устройства.

Устройство содержит контролируемый регистр 1, элемент 2 свертки по модулю два, триггер 3, элемент И Аи элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, первый и второй входы которого соединены соответственно с выходом и информацион- нь1М входом треггера 3, причем вход синхронизации триггера 3 соединен с первым синхронизирующим входом 6 устройства, вход синхронизации регистра 1 сдвига и второй вход элемента И 4 соединены с вторым синхронизирующим входом 7 устройства, вход управления параллельной записью регистра 1 сдвига соединен с входом 8 устройства, информационные входы параллельной записи регистра I сдвига являются информационными входами 9 устройства, выход элемента И 4 является выходом 10 ошибки устройства, выход последнего разряда регистра I сдвига является информационным выходом 11 устройства, соединенного также с информационным входом последовательной записи регистра 1 сдвига.

Устройство работает следующим образом.

В исходном состоянии после подачи на вход 8 устройства импульса параллельной записи на выходы регистра 1 сдвига запишется информация, находящаяся в это время на входах 9 устройства. Далее на вход 6 устройства подается импульс, по которому в триггер 3 запишется информация с выхода элемента 2 свертки по модулю два. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 будет логический нуль, так как информация на обоих входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 после прохождения импульса на входе 6 устройства будет одинакова. Соответственно на выходе 10 устройства будет присутствовать логический нуль, означающий отсутствие ошибки в регистре 1.

Считывается информация из регист- ipa 1 сдвига на выходе П устройства.

5

5

0

5

0

5

0

5

При сдвигах информации в регистре 1 сдвига,, которые происходят по каждому импульсу на входе 7 устройства (перепаду из состояния логической единицы в состояние логического ну ля), количество единиц на выходах регистра 1 сдвига не изменяется, так как выдвигаемый разряд по обратной, связи через информационный вход сдвига регистра 1 сдвлга записывается в первый разряд регистра 1 сдвига. Соответственно сигнал на выходе элемента 2 свертки по модулю два не изменяется и сигнал ошибки на выходе 10 устройства отсутствует.

При сбоях в работе регистра 1 . сдвига, приводящих к изменению числа единиц на выходах (искажение информации в любом разряде либо в любом нечетном количестве разрядов одновременно, либо в любом количестве разрядов в разные моменты времени), информация на выходе элемента 2 свертки по модулю два изменяется, что ведет к изменению информации на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и на вьрсоде элемента И 4. В результате на выходе 10 устройства появляется логическая единица, означающая наличие ошибки в работе регистра . сдвига. Причем сигнал ошибки на выходе 10 устройства может появиться только тогда, когда на втором входе элемента И 4 присутствует логическая единица. При наличии на этом входе логического нуля ошибка блокируется. Возможность кратковременного изменения информации на выходе элемента ИС1ШОЧАЮЩЕЕ ИЛИ 5 не приведет к появлению ложного сигнала ошибки на выходе 10, так как после прохождения переднего фронта импульса на входе 7 устройства (перепада от уровня логической единицы до уровня логического дуля) на этом входе и, следовательно, на втором входе элемента И 4 присутствует логический нуль.

После окончания импульса на входе 7 устройства (восстановления уровня логической единицы) блокировка сигнала ошибки снимается и, если при последнем сдвиге произошел сбой в работе сдвигового регистра, то на выходе 10 устройства появится сигнал ошибки.

Таким образом, за счет вйедения элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и соответствующих связей в схему контроля регистра сдвига обеспечивается упрощение схемы устройства, а также блокирование лож1-гых сигналов ошибки, возникающих в результате переходных процессов в схеме, что приводит к повышению достоверности результата контроля сдвигового регистра и сокращению оборудования.

Формула изобретения

Регистр сдвига с самоконтролем, содержалщй элемент свертки по модулю два, входы которого соединены с выходами контролируемого регистра сдвига триггер и элемент И, отличающийся тем, что, с целью сокращения оборудования и повьшения достоверности функционирования,- в него введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,, выход которого соединен с первым входом элемента И, первый вход элемента

Редактор С. Пекарь Заказ 3839/48

Составитель А. Яковлев Техред Л.Сердюкова

Корректор С.

Тираж 589 .Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5

0

ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом триггера, а второй вход элемента ИС- КЛЮЧАЩЕЕ ИЛИ соединен с информационным входом триггера и выходом элемента свертки по модулю два, вход синхронизации триггера является первым входом синхронизации устройства, вход синхронизации регистра сдвига и второй вход элемента И являются вторым синхронизирующим входом устройства, вход управления параллельной записью регистра сдвига является входом записи информации устройства, информационные входы параллельной Записи регистра сдвига являются информационными входами устройства, выход элемента И является выходом ошибки устройства, выход последнего разряда регистра сдвига соединен с информационным входом последовательной записи регистра и является информационным выходом устройства.

Корректор С. Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Устройство для контроля передачи информации | 1984 |

|

SU1251083A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| ДВУХУРОВНЕВОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК | 1992 |

|

RU2037891C1 |

| Устройство Нисневича для контроля двоичной информации | 1987 |

|

SU1464294A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Запоминающее устройство с тестовым самоконтролем | 1986 |

|

SU1396160A1 |

Изобретение относится к вычислительной технике, в частности к устройствам контроля функциональных электрических узлов. Целью изобретения является, сокращение оборудования и повышение достоверности функциони- рования. Регистр сдвига содержит/ контролируемый регистр 1, элемент 2 свертки по модулю два, триггер 3,. элемент И 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Обнаруживаются ошибки в любом количестве разрядов регистра сдвига в режиме хранения, а также ошибки в любом разряде и в любом нечетном количестве разрядов при сдвиге информа-. ции. В регистре обеспечивается контроль информации в регистре как при хранении, так и при сдвиге информации. 1 йл.

| Устройство для контроля регистраСдВигА | 1978 |

|

SU799018A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля регистраСдВигА | 1979 |

|

SU813434A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-23—Публикация

1985-09-30—Подача