Изобретение относится к вычислительной технике и может бьггь использовано при разработке цифровых интегральных схем на ВДП-транзисторах,

Цепь изобретения - повьпиение бьк;тродействия матрицы постоянного запоминающего устройства,

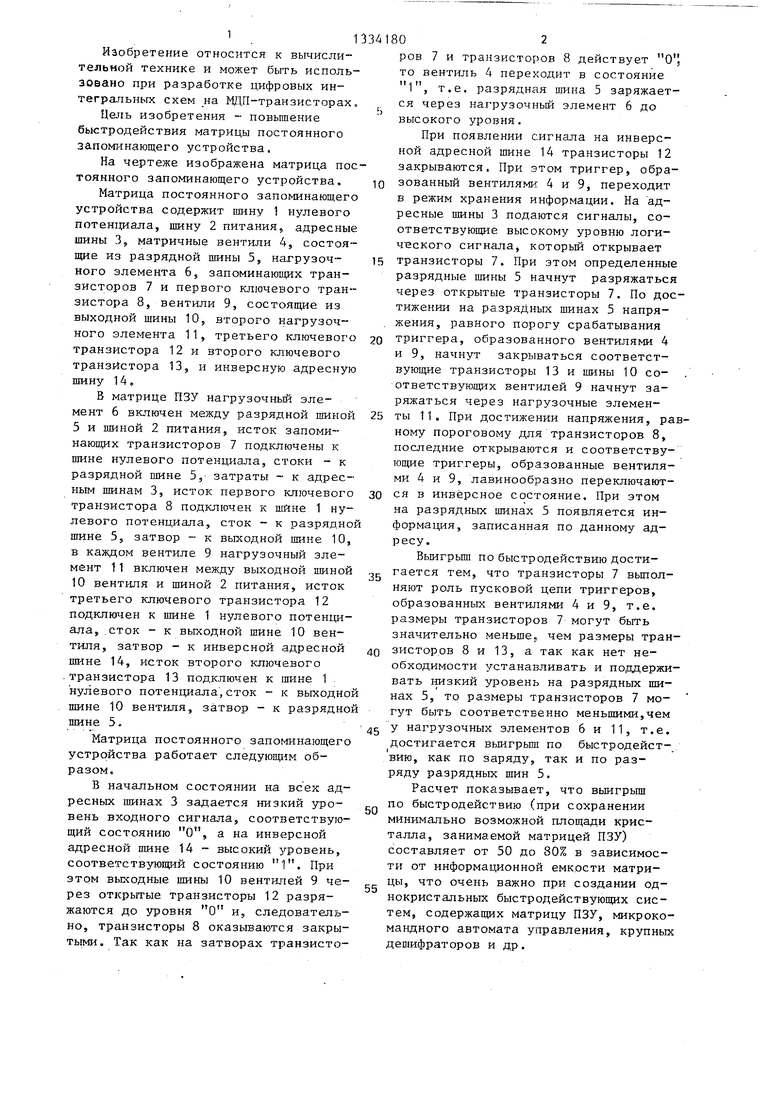

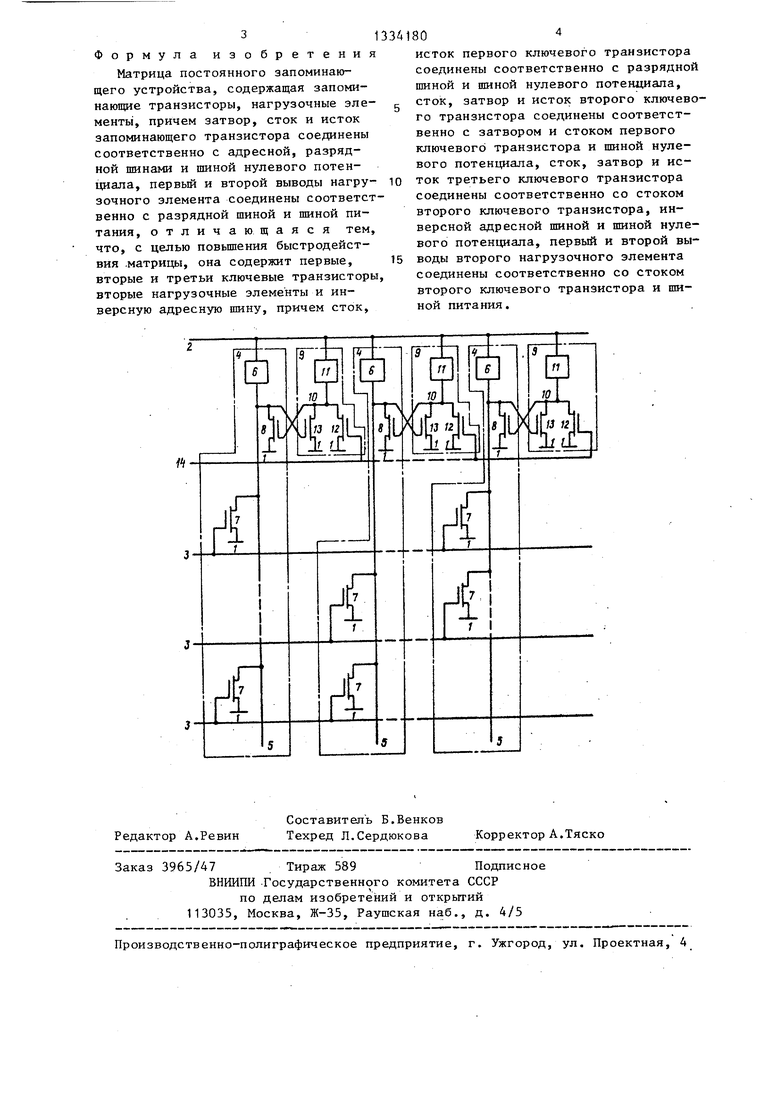

На чертеже изображена матрица постоянного запоминающего устройства.

Матрица постоянного запоминающего устройства содержит шину 1 нулевого потенциала, шину 2 питания, адресные шины 3, матричные вентили 4, состоящие из разрядной шины 5, нагрузочного элемента 6, запоминающих транзисторов 7 и первого ключевого транзистора 8, вентили 9, состоящие из выходной шины 10, второго нагрузочного элемента 11, третьего ключевого транзистора 12 и второго ключевого транзистора 13, и инверсную адресную шину 14.

В матрице ПЗУ нагрузочньй элемент 6 включен между разрядной шиной 5 и шиной 2 питания, исток запоминающих транзисторов 7 подключены к шине нулевого потенциалаэ стоки - к разрядной шине 5,- затраты - к адресным шинам 3, исток первого ключевого транзистора 8 подключен к шине 1 нулевого потенциала, сток - к разрядно шине 5, затвор - к выходной шине 10, в каждом вентиле 9 нагрузочный элемент 11 включен между выходной шиной 10 вентиля и шиной 2 питания, исток третьего ключевого транзистора 12 подключен к шине 1 нулевого потенциала, .сток - к выходной шине 10 вентиля, затвор - к инверсной адресной шине 14, исток второго ключевого .транзистора 13 подключен к шине 1 нулевого потенциала,сток - к выходно шине 10 вентиля, затвор - к разрядно шине 5.

Матрица постоянного запоминающего устройства работает следующим образом

В начальном состоянии на вс ех адресных шинах 3 задается низкий уровень входного сигнала, соответствующий состоянию О, а на инверсной адресной шине 14 - высокий уровень, соответствзпощий состоянию 1, При этом выходные шины 10 вентилей 9 через открытые транзисторы 12 разряжаются до 1ФОВНЯ О и, следовательно, транзисторы 8 оказываются закрытыми. Так как на затворах транзисто0

5

0

5

0

5

0

5

0

5

ров 7 и транзисторов 8 действует О то вентиль 4 переходит в состояние 1, т.е. разрядная шина 5 заряжается через нагрузочный элемент 6 до высокого уровня.

При появлении сигнала на инверсной адресной шине 14 транзисторы 12 закрываются. При этом триггер, образованный вентилями 4 и 9, переходит в режим хранения информации. На адресные шины 3 подаются сигналы, соответствующие высокому уровню логи- ч еского сигнсша, которьш открывает транзисторы 7. При этом определенные разрядные шины 5 начнут разряжаться через открытые транзисторы 7. По достижении на разрядных шинах 5 напряжения, равного порогу срабатывания триггера, образованного вентилями 4 и 9, начнут закрьшаться соответствующие транзисторы 13 и шины 10 соответствующих вентилей 9 начнут заряжаться через нагрузочные элементы 11, При достижении напряжения, равному пороговому для транзисторов 8, последние открываются и соответствующие триггеры, образованные вентилями 4 и 9, лавинообразно переключаются в инверсное состояние. При этом на разрядных шинах 5 появляется информация, записанная по данному адресу.

Выигрьш по быстродействию достигается тем, что транзисторы 7 вьшол- няют роль пусковой цепи триггеров, образованных вентилями 4 и 9, т.е. размеры транзисторов 7 могут быть значительно меньше, чем размеры транзисторов 8 и 13, а так как нет необходимости устанавливать и поддерживать низкий уровень на разрядных шинах 5, то размеры транзисторов 7 могут быть соответственно меньшими,чем у нагрузочных элемЕШтов 6 и 11, т.е. достигается выигрьш по быстродейст- , вию, как по заряду, так и по разряду разрядных шин 5.

Расчет показывает, что вьшгрьпп по быстродействию (при сохранении минимально возможной площади кристалла, занимаемой матрицей ПЗУ) составляет от 50 до 80% в зависимости от информационной емкости матрицы, что очень важно при создании однокристальных быстродействующих систем, содержащих матрицу ПЗУ, микрокомандного автомата управления, крупных дешифраторов и др.

Формула изобретения

Матрица постоянного запоминающего устройства, содержащая запоминающие транзисторы, нагрузочные элементы, причем затвор, сток и исток запоминающего транзистора соединены соответственно с адресной, разрядной шинами и шиной нулевого потенциала, первый и второй выводы нагрузочного элемента соединены соответственно с разрядной шиной и шиной питания, отличающаяся тем, что, с целью повьш 1ения быстродействия .матрицы, она содержит первые, вторые и третьи ключевые транзисторы вторые нагрузочные элементы и инверсную адресную шину, причем сток.

исток первого ключевого транзистора соединены соответственно с разрядной шиной и шиной нулевого потенциала, сток, затвор и исток второго ключевого транзистора соединены соответственно с затвором и стоком первого ключевого транзистора и пшной нулевого потенциала, сток, затвор и исток третьего ключевого транзистора соединены соответственно со стоком второго ключевого транзистора, инверсной адресной шиной и шиной нулевого потенциала, первый и второй выводы второго нагрузочного элемента соединены соответственно со стоком второго ключевого транзистора и шиной питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1348908A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Ассоциативный запоминающий элемент | 1978 |

|

SU675452A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Элемент памяти | 1984 |

|

SU1163356A1 |

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке интегральных схем запоминающих устройств. Целью изобретения является повьшение быстродействия. Поставленная цель достигается тем, что в матрицу введены первые, вторые и третьи ключевые транзисторы, вторые нагрузочные элементы и инверсная адресная шина. 1 ил. оо 00

Редактор А.Ревин

Составитель Б.Венков Техред Л.Сердюкова

Заказ 3965/47Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открьп-ий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А.Тяско

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

| Генератор с приводом для ручной электрической лампы | 1919 |

|

SU586A1 |

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

| НЕФТЯНАЯ РЕГЕНЕРАТИВНАЯ ПЕЧЬ | 1921 |

|

SU727A1 |

| Сенситометр | 1922 |

|

SU1809A1 |

Авторы

Даты

1987-08-30—Публикация

1983-03-02—Подача