Изобретение относится к вычислительной технике и может найти применение при разработке цифровых интегральных схем на МДП-транзисторах.

Цель изобретения - повышение быстродействия постоянного запоминающего устройства (ПЗУ).

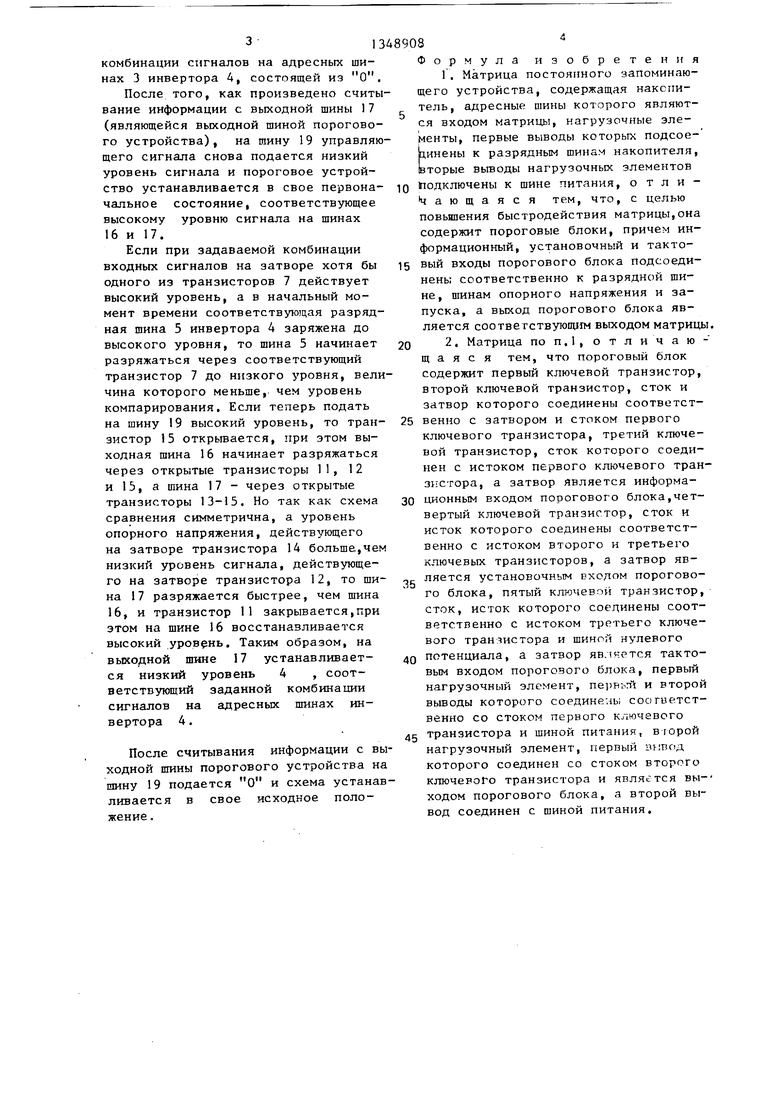

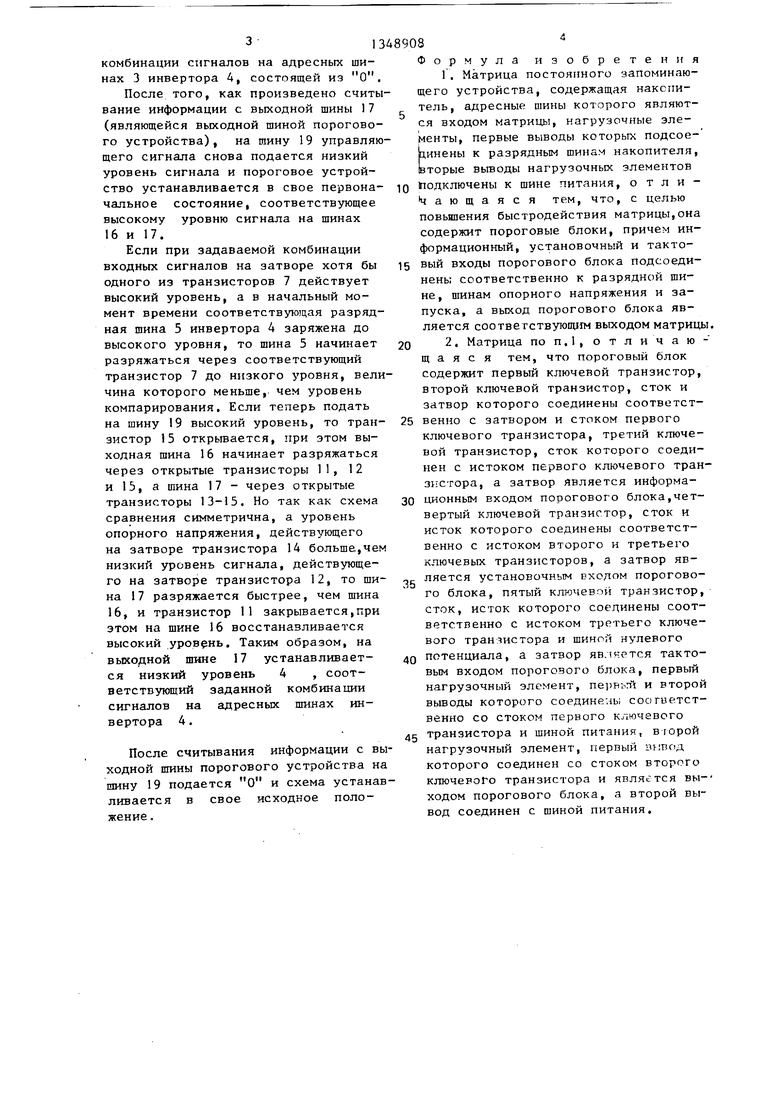

На чертеже изображена матрица ПЗУ.

Матрица содержит общую шину 1,шину 2 питания, адресные шины 3, инверторы 4, каждый из которых состоит из разрядной шины 5, нагрузочного элемента 6 и запоминающих транзисторов 7, пороговые блоки 8, состоящие из нагрузочных элементов 9 и 10, первого ключевого транзистора I1, третьего ключевого транзистора 12, второго ключевого транзистора 13, четвертого ключевого транзистора 14, пятого ключевого транзистора 15, выходной шины 16 инверсного плеча, выходной шины 17 прямого плеча, входной шины 18 опорного напряжения и входной запускающей шины 19. В быстродействующей матрице в каждом инверторе 4 нагрузочный элемент 6 включен между разрядной шиной 5 и шиной 2 питания, истоки запоминающих транзисторов 7 подключены к общей шине 1,стоки - к разрядной шине 5, затворы - к соответствующим адресным шинам 3, в каждом пороговом блоке нагрузочный элемент 9 включен ме/зду выходной шиной 17 и шиной 2 питания, нагрузочный элемент 10 включен между выходной шиной 17 и шиной 2 питания,сток первого ключевого транзистора 11 подключена к выходной шине 16 инверсно- 40 на шину 19 запуска высокий уровень,

го плеча и затвору второго ключевого транзистора 13, затвор - к выходной шине 17 прямого плеча, исток - к стоку третьего ключевого транзистора

12 затвор третьего ключевого транзистора 12 подключен к соответствующей разрядной шине 5, исток - к стоку пятого ключевого транзистора 15, сток второго ключевого транзистора 13 подключен к выходной шине 17 прямого плеча, исток - к стоку четвертого ключевого транзистора 14, затвор четвертого ключевого транзистора 14 подключен к шине опорного напряжения, исток - к стоку пятого ключевого транзистора 15, затвор пятого ключевого транзистора 15 подключен к шине 19 запуска сигнала, исток - к общей шине ,

Пороговое устройство (схема сравнения) представляет собой симметричный RS-триггер с управлением (т.е. паразитные емкости выходных шин 16 и 17 равны, идентичны нагрузочные элементы 9 и 10, транзисторы 11 и 13,

12и 14 соответственно). Матрица ПЗУ работает следующим

образом.

На шине 18 опорного напряжения задается требуемый уровень опорного напряжения (уровень компарирования). Пусть в начальный момент времени на

шине 19 запуска действует низкий уровень входного сигнала (О), тогда транзистор. 15 закрыт и выходные шины 16 и 17 заряжены до высокого уровня (1) через нагрузочные элементы 9 и 10 соответственно от шины питания. Следовательно, транзисторы 11,

13и 14 oткJ)ыты, но так как транзистор 15 закрыт, уровень сигнала на выходных щинах 16 и 17 не зависит от уровня сигнала, действующего на затворе логического транзистора инверсного плеча 12 в этот момент времени.

Подадим теперь на шины 3 комбинацию входных сигналов. Если разряд- ная шина 5 в начальный момент была разряжена (т.е. уровень сигнала на шине 5 соответствовал О), а комбинация входных сигналов состоит из

О, то разрядная шина 5 начи- заряжаться от шины 2 питания через нагрузочный элемент 6 до высокого уровня, превышающего уровень опорного напряжения, и транзистор 12 открывается. Если теперь подать

одних нает

то транзистор 15 открывается, выходная шина 16 начинает разряжаться через открытые транзисторы 11, 12 и 15, а выходная шина 17 - через отк45 рытые транзисторы 13 - 15. Но так как схема сравнения симметрична, а уровень сигнала, действующего на затворе транзистора 12, больше, чем опорное напряжение, то выходная ши-

50 на 16 разрядится быстрее, чем шина 17, и транзистор 13 закрывается, при этом на выходной шине 17 восстанавливается высокий уровень (через нагрузочный элемент 10 от шины 2 пита55 ния) и поддерживает транзистор 13 в открытом состоянии. Таким обра-- зом, на выходной шине 17 устанавливается высокий уровень сигнала (1), соответствующий заданной

комбинации сигналов на адресных шинах 3 инвертора 4, состоящей из О

После того, как произведено считывание информации с выходной шины 17 (являющейся выходной шиной порогового устройства), на шину 19 управляющего сигнала снова подается низкий уровень сигнала и пороговое устройство устанавливается в свое первоначальное состояние, соответствующее высокому уровню сигнала на шинах 16 и 17.

Если при задаваемой комбинации входных сигналов на затворе хотя бы одного из транзисторов 7 действует высокий уровень, а в начальный момент времени соответствующая разрядная шина 5 инвертора 4 заряжена до высокого уровня, то шина 5 начинает разряжаться через соответствующий транзистор 7 до низкого уровня, величина которого меньше, чем уровень компарирования, Если теперь подать на шину 19 высокий уровень, то транзистор 15 открьгоается, при этом выходная шина 16 начинает разряжаться через открытые транзисторы 11, 12 и 15, а шина 17 - через открытые транзисторы 13-15. Но так как схема сравнения симметрична, а уровень опорного напряжения, действующего на затворе транзистора 14 больше,чем низкий уровень сигнала, действующего на затворе транзистора 12, то шина 17 разряжается быстрее, чем шина 16, и транзистор 11 закрывается,при этом на шине 16 восстанавливается высокий уровень. Таким образом, на выходной шине 17 устанавливается низкий уровень 4 , соответствующий заданной комбинации сигналов на адресных шинах инвертора 4.

После считывания информации с выходной шины порогового устройства на шину 19 подается О и схема устанавливается в свое исходное положение .

5

0

5

0

5

0

5

Формула изобретения

1.Матрица постоянного запоминающего устройства, содержащая накопитель, адресные шины которого являются входом матрицы, нагрузочные элементы, первые выводы которых подсоединены к разрядньм шинам накопителя, вторые вьшоды нагрузочных элементов 1подключены к шине питания, о т л и - чающаяся тем, что, с целью повьнпения быстродействия матрицы,она содержит пороговые блоки, причем информационный, установочный и тактовый входы порогового блока подсоединены соответственно к разрядной шине, шинам опорного напряжения и запуска, а выход порогового блока является соответствующим выходом матрицы.

2.Матрица по п.1, о т л и ч а ю - щ а я с я тем, что пороговый блок содержит первый ключевой транзистор, второй ключевой транзистор, сток и затвор которого соединены соответственно с затвором и стоком первого ключевого транзистора, третий ключевой транзистор, сток которого соединен с истоком первого ключевого транзистора, а затвор является информационным входом порогового блока,четвертый ключевой транзистор, сток и исток которого соединены соответственно с истоком второго и третьего ключевых транзисторов, а затвор является установочным входом порогового блока, пятый клтачевой транзистор, сток, исток которого соединены соответственно с истоком третьего ключевого транзистора и шиной нулевого потенциала, а затвор является тактовым входом порогового блока, первый нагрузочный элемент, первьЛ и второй вьшоды которого соединены соогиетст- венно со стоком первого ключевого транзистора и шиной питания, в горой нагрузочный элемент, первый инвод которого соединен со стоком второго ключевого транзистора и является вы-- ходом порогового блока, а второй вывод соединен с шиной питания.

г

I

г

8

IB 77

Ю

11

L

м

ш д

I-L-1

4Г

Составитель Б.Венков Редактор Т.Лазоренко Техред М.Ходанич

Заказ 5196/52Тираж 587Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

п

f t

r

п

и

h

w

IB

Корректор Н.Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1334180A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке интегральных схем запоминающих устройств. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что матрица содержит пороговые блоки, опорного напряжения и запуска порогового элемента, 1 з.п. ф-лы, 1 и.п. (Л с со 4 оо со о сю

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

| Генератор с приводом для ручной электрической лампы | 1919 |

|

SU586A1 |

| Сенситометр | 1922 |

|

SU1809A1 |

Авторы

Даты

1987-10-30—Публикация

1983-04-01—Подача