I

Известно устройство для преобразования уровней напряжения 1, в котором к входу подключены затворы транзисторов г -типа, р-типа и исток второго транзисторап-типа. Устройство служит для согласования с ТТЛсхемами, однако, не выполняет функции защелки, т. е. запоминания информации.

Наиболее близким по технической сущности к изобретению является быстродействующий усилитель на КМДП-транзисторах 2, который- содержит два ключевых транзистора р-типа и два нагрузочных транзистора П-типа, соединенных по схеме триггера, два ключевых транзистора П-типа, истоки которых подключены к шине нулевого потенциала, а затворы - к первой управляющей щине, и два транзистора сброса р-типа, стоки которых соединены со стоками соответствующих ключевых р-типа транзисторов и с выходами усилителя, истоки - с истоками ключевых транзисторов р-типа и с щиной питания, а затворы подключены ко второй управляющей шине, первую и вторую разрядные шины (шины входной информации), два согласующихп-типа транзистора, истоки которых соединены со стоками соответствующих ключевыхП-типа транзисторов,

стоки - с истоками соответствующих нагрузочныхП-типа, транзисторов, а затворы - соответственно с первой и второй разрядными шинами.

Недостатками этого усилител являются ограниченные функциональные возможности;

5 необходимость в дифференциальном входном сигнале и невозможность использования схемы для непосредственной стыковки с ТТЛ-схемами в режиме.защелки.

Целью изобретения является расширение функциональных возможностей усилителя за счет обеспечения функции запоминания. Поставленная цель достигается тем, что в усилителе на КМДП-транзисторах, содержащем два клк)чевых транзистора р-типа и два нагрузочных транзистора п-типа, единенных по схеме триггера, в котором стоки первых ключевого- и нагрузочного транзисторов подключены к прямому выходу усилителя и к затворам второго ключевого и нагрузочного транзисторов, стоки которых подключены к инверсному выходу усилителя

20 и к затворам первых ключевого и нагрузочного Транзисторов, истоки ключевых транзисторов триггера подключены к шине питания, два согласующих транзистораа-типа.

сток каждого из которых подключен к истоку соответствующего нагрузочного триггера, два ключевых транзистораП-типа, сток каждого из которых подключен к истоку соответствующего согласующего транзистора, а исток первого ключевого транзистора д-типа соединен с шиной нулевого потенциала, а затвор - с входной информационной шиной, два транзистора сброса р-типа, стоки которых соединены со стоками соответствующих ключевых транзисторов р-типа, истоки - с щиной питания, а затворы - с управляющей шиной, введены дополнительные транзисторы сброса Л.-типа, истоки которых подключены к шине нулевого потенциала, а каждый сток - к соответствующему истоку нагрузочных транзисторов триггера Л.-типа, затворы - к затворам согласующих транзисторов fv-типа и к затворам транзисторов сброса р-типа, исток ключевого транзистораЛ-типа подключен к шине входной информационной, а затвор - к шине питания.

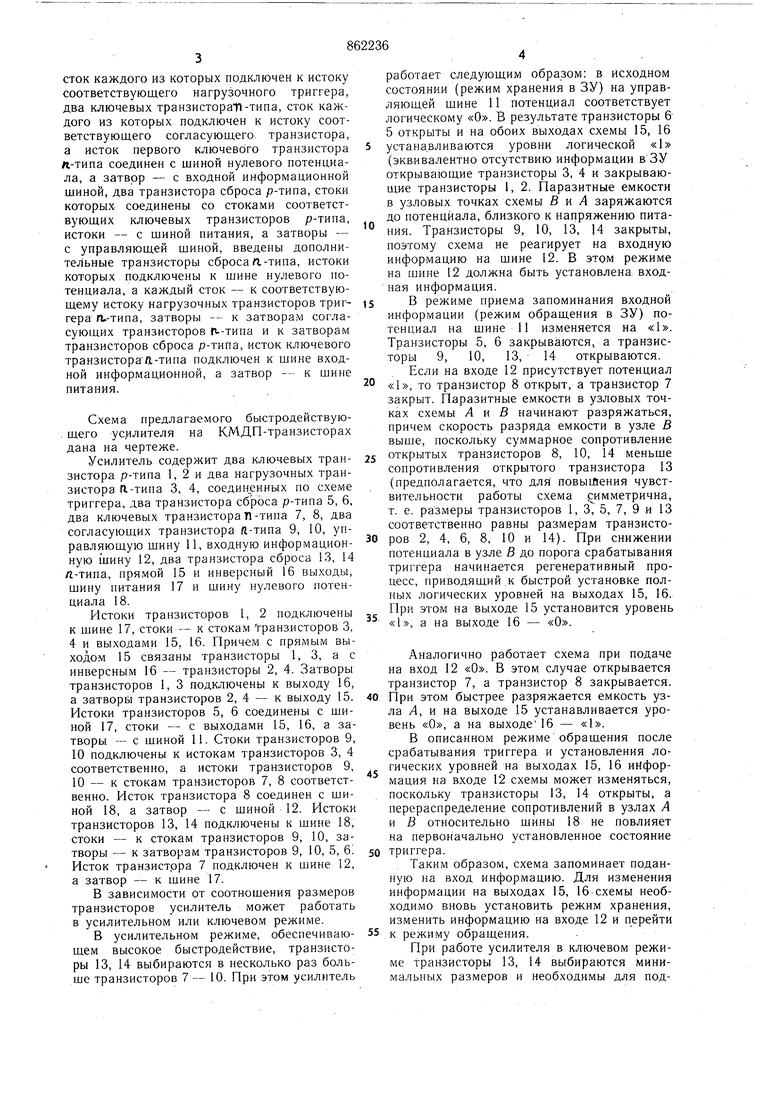

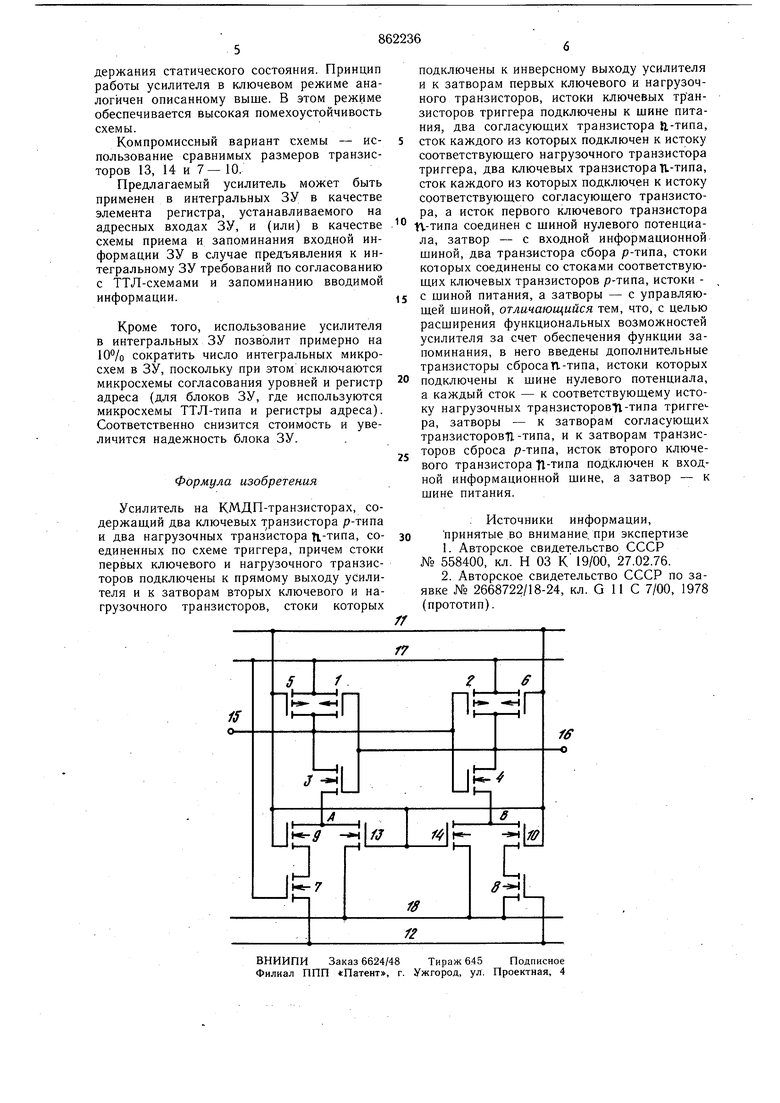

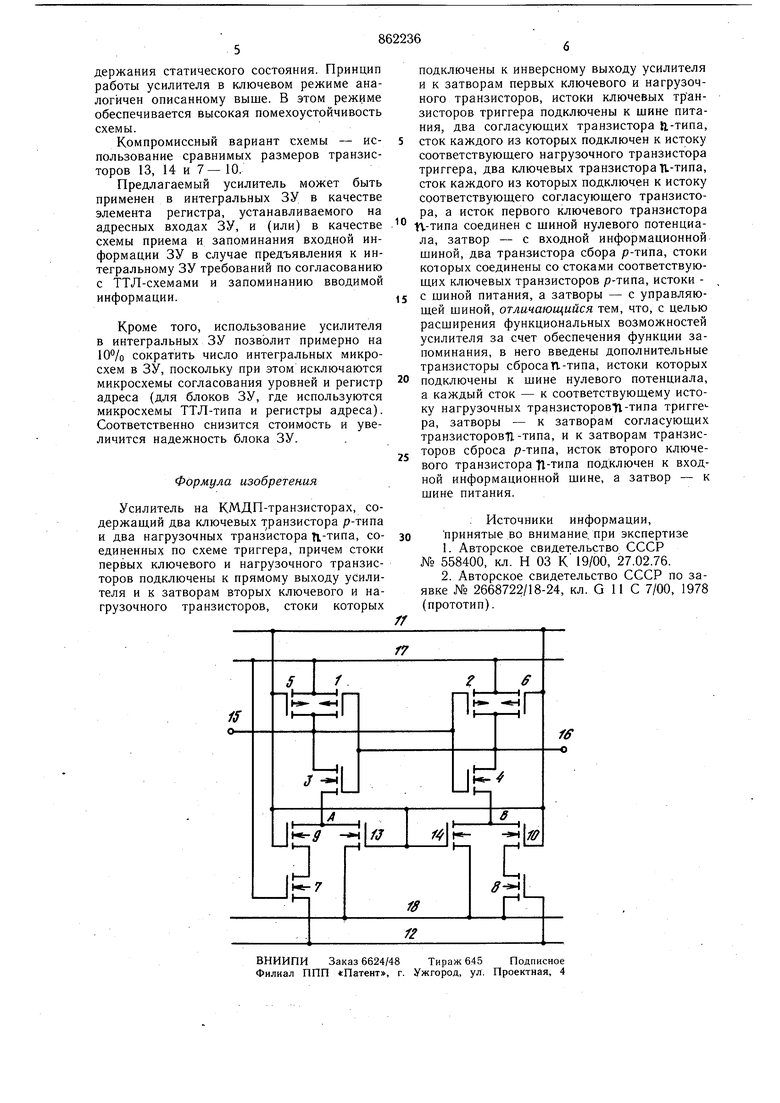

Схема предлагаемого быстродействую. щего усилителя на КМДП-транзисторах дана на чертеже.

Усилитель содержит два ключевых транзистора р-типа 1, 2 и два нагрузочных транзистора П-типа 3, 4, соединенных по схеме триггера, два транзистора сброса р-типа 5, 6, два ключевых транзистора Т1-типа 7, 8, два согласующих транзистора й-типа 9, 10, управляющую шину 11, входную информационную fuHHy 12, два транзистора сброса 13, 14 л-типа, прямой 15 и инверсный 16 выходы, шину питания 17 и шину нулевого потенциала 18.

Истоки транзисторов 1, 2 подключены к шине 17, стоки - к стокам транзисторов 3, 4 и выходами 15, 16. Причем с прямым выходом 15 связаны транзисторы 1, 3, а с инверсным 16 - транзисторы 2, 4. Затворы транзисторов 1, 3 подключены к выходу 16, а затворы транзисторов 2, 4 - к выходу 15. Истоки транзисторов 5, 6 соединены с шиной 17, стоки - с выходами 15, 16, а затворы - с шиной 11. Стоки транзисторов 9, 10 подключены к истокам транзисторов 3, 4 соответственно, а истоки транзисторов 9, 10 - к стокам транзисторов 7, 8 соответственно. Исток транзистора 8 соединен с шиной 18, а затвор - с шиной 12. Истоки транзисторов 13, 14 подключены к шине 18, стоки - к стокам транзисторов 9, 10, затворы - к затворам транзисторов 9, 10, 5, 6. Исток транзистора 7 подключен к шине 12, а затвор к шине 17.

В зависимости от соотношения размеров транзисторов усилитель может работать в усилительном или ключевом режиме.

В усилительном режиме, обеспечивающем высокое быстродействие, транзисторы 13, 14 выбираются в несколько раз больше транзисторов 7 - 10. При этом усилитель

работает следующим образом: в исходном состоянии (режим хранения в ЗУ) на управляющей шине 11 потенциал соответствует логическому «О. В результате транзисторы 6 5 открыты и на обоих выходах схемы 15, 16 устанавливаются уровни логической «1 (эквивалентно отсутствию информации в ЗУ открывающие транзисторы 3, 4 и закрывающие транзисторы 1, 2. Паразитные емкости в узловых точках схемы В и А заряжаются до потенциала, близкого к напряжению питания. Транзисторы 9, 10, 13, 14 закрыты, поэтому схема не реагирует на входную информацию на шине 12. В этом режиме на шине 12 должна быть установлена, входная информация.

В режиме приема запоминания входной информации (режим обращения в ЗУ) потенциал на шине 11 изменяется на «1. Транзисторы 5, 6 закрываются,, а транзисторы 9, 10, 13, 14 открываются.

Если на входе 12 присутствует потенциал «1, то транзистор 8 открыт, а транзистор 7 закрыт. Паразитные емкости в узловых точках схемы Лий начинают разряжаться, причем скорость разряда емкости в узле В выше, поскольку суммарное сопротивление открытых транзисторов 8, 10, 14 меньше сопротивления открытого транзистора 13 (предполагается, что для повышения чувствительности работы с.хема (:имметрична, т. е. размеры транзисторов 1, , 7, 9 и 13 соответственно равны размерам транзисторов 2, 4, 6, 8, 10 и 14). При снижении потенциала в узле В до порога срабатывания триггера начинается регенеративный процесс, приводящий.к быстрой установке полных логических уровней на выходах 15, 16. При этом на выходе 15 установится уровень «1, а на выходе 16 - «О.

Аналогично работает схема при подаче на вход 12 «О. В этом случае открывается транзистор 7, а транзистор 8 закрывается. При этом быстрее разряжается емкость узла Л, и на выходе 15 устанавливается уровень «О, а на выходе 16 - «1.

В описанном режимеобращения после срабатывания триггера и установления логических уровней на выходах 15, 16 информация на входе 12 схемы может изменяться, поскольку транзисторы 13, 14 открыты, а перераспределение сопротивлений в узлах А и В относительно шины 18 не повлияет на первоначально установленное состояние триггера.

. Таким образом, схема запоминает поданную на вход информацию. Для изменения информации на выходах 15, 16-схемы необходимо вновь установить режим хранения, изменить информацию на входе 12 и перейти к режи.му обращения.

При работе усилителя в ключевом режиме транзисторы 13, 14 выбираются минимальных размеров и необходимы для поддержания статического состояния. Принцип работы усилителя в ключевом режиме аналогичен описанному выше. В этом режиме обеспечивается высокая помехоустойчивость схемы. Компромиссный вариант схемы - использование сравнимых размеров транзисторов 13, 14 и 7- 10. Предлагаемый усилитель может быть применен в интегральных ЗУ в качестве элемента регистра, устанавливаемого на адресных входах ЗУ, и (или) в качестве схемы приема и запоминания входной информации ЗУ в случае предъявления к интегральному ЗУ требований по согласованию с ТТЛ-схемами и запоминанию вводимой информации. Кроме того, использование усилителя в интегральных ЗУ позволит примерно на 10% сократить число интегральных микросхем в ЗУ, поскольку при этом исключаются микросхемы согласования уровней и регистр адреса (для блоков ЗУ, где используются микросхемы ТТЛ-типа и регистры адреса). Соответственно снизится стоимость и увеличится надежность блока ЗУ. Формула изобретения Усилитель на КМДП-транзисторах, содержаший два ключевых транзистора р-типа и два нагрузочных транзистора ц-типа, соединенных по схеме триггера, причем стоки первых ключевого и нагрузочного транзисторов подключены к прямому выходу усилителя и к затворам вторых ключевого и нагрузочного транзисторов, стоки которых подключены к инверсному выходу усилителя и к затворам первых ключевого и нагрузочного транзисторов, истоки ключевых транзисторов триггера подключены к шине питания, два согласуюш,их транзистора Ц-типа, сток каждого из которых подключен к истоку соответствуюш,его нагрузочного транзистора триггера, два ключевых транзистора и-типа, сток каждого из которых подключен к истоку соответствуюшего согласуюш,его транзистора, а исток первого ключевого транзистора -типа соединен с шиной нулевого потенциала, затвор - с входной информационной шиной, два транзистора сбора р-типа, стоки которых соединены со стоками соответствуюших ключевых транзисторов р-типа, истоки с шиной питания, а затворы - с управляюшей шиной, отличающийся тем, что, с целью расширения функциональных возможностей усилителя за счет обеспечения функции запоминания, в него введены дополнительные транзисторы сбросаП.-типа, истоки которых подключены к шине нулевого потенциала, а каждый сток - к соответствующему истоку нагрузочных транзисторовЦ-типа триггера, затворы - к затворам согласующих транзисторов -типа, и к затворам транзисторов сброса р-типа, исток второго ключевого транзистора Ц-типа подключен к входной информационной шине, а затвор - к шине питания. . Источники информации, принятые во внимание, при экспертизе 1.Авторское свидетельство СССР № 558400, кл. Н 03 К 19/00, 27.02.76. 2.Авторское свидетельство СССР по заявке № 2668722/18-24, кл. G 11 С 7/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

Авторы

Даты

1981-09-07—Публикация

1979-12-26—Подача