Чг

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1405050A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1335985A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1259259A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих устройствах. Целью изобретения является повышение быстродействия. Устройство содержит регистр 1 аргумента, вычитатель 3, матричный умножитель 5, блок 2 памяти, мультиплексор 4. Вычисление обратной величины происходит путем получения разности между старшей и младшей частями аргумента и двукратного умножения этой разности на коэффициент. 1 ил.

я/г

Jte O П

Лог.(

0,3

/I

-

л

-

СП

О5 О) 00 4 -U

Ц

Изобретение сп носится к вычислительной технике и может быть использовано для быстрого вычисления обратной величины нормализованной двоич- ной дроби в быст родействующих арифметических устройствах.

Цель изобретения - повышение быстродействия устройства.

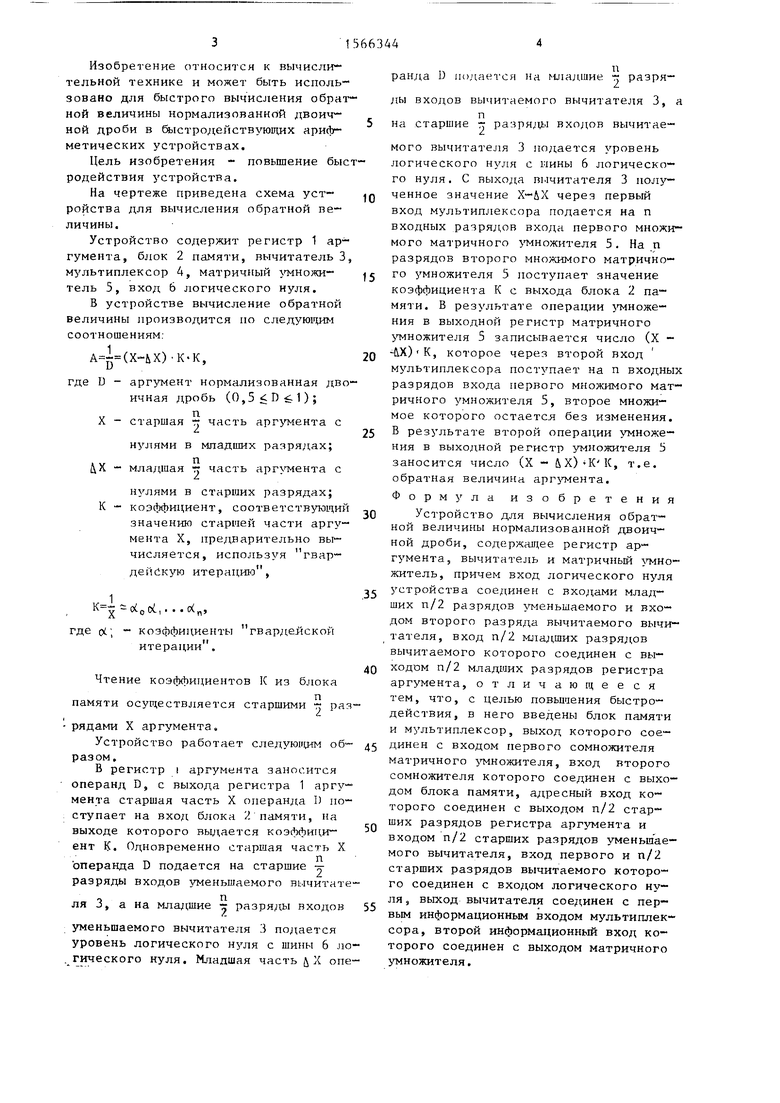

На чертеже приведена схема уст- ройства для вычисления обратной величины.

Устройство содержит регистр 1 аргумента, блок 2 памяти, пычитательЗ, мультиплексор А, матричный умножи- тель 5, вход b логического нуля.

В устройстве вычисление обратной величины производится по следующим соот ношениям

(Х-ЬХ) К-К,

где D - аргумент нормализованная двоичная дробь (0,5 );

п X - старшая - часть аргумента с

нулями в младших разрядах; ДХ - младшая -j часть aprvMeHTa с

нулями в старших разрядах; К - коэффициент, соответствующий значению старшей части аргумента X, предварительно вычисляется, ИСПОЛЬЗУЯ гвардейскую итерацию,

0Ј | Х„

где (X., коэффициенты гвардейской итерации.

Чтение коэффициентов К из блока

п памяти осуществляется старшими - разрядами X аргумента.

Устройство работает следующим об- д5 разом.

В регистр i аргумента заносится

операнд D, с выхода регистра 1 аргумента старшая часть X операнда 1) поступает на вход блока А памяти, на выходе которого выдается коэффициент К. Одновременно старшая часть X

п операнда D подается на старшие -

разряды входов уменьшаемого вичитатепля J, а на младшие - разряды входов 55

уменьшаемого вычитателя 3 подается уровень логического нуля с шины 6 чо- гического нуля. Младшая часть дХ one-

50

j

0

5

0

5

0

5

55

50

ранда D подается на младшие -, разряды входов вычитаемого вычитателя 3, а

п

на старшие - разряды входов вычитаемого вычитателя J подается уровень логического нуля с пины 6 логического нуля. С выхода ппчитателя 3 полученное значение X-&Х через первый вход мультиплексора подается на п входных разрядов входа первого множимого матричного умножителя 5. На п разрядов второго множимого матричного умножителя 3 поступает значение коэффициента К с выхода блока 2. памяти. В результате операции умножения в выходной регистр матричного умножителя 5 записывается число (X - АХ) К, которое через второй вход мультиплексора поступает на п входных разрядов входа первого множимого матричного умножителя 5, второе множимое которого остается без изменения. В результате второй операции умножения в выходной регистр умножителя b заносится число (X - ЬХ)-К К, т.е. обратная величина аргумента. Формула изобретения

Устройство для вычисления обратной величины нормализованной двоичной дроби, содержащее регистр аргумента, вычитатель и матричный умножитель, причем вход логического нуля устройства соединен с входами младших п/2 разрядов уменьшаемого и входом второго разряда вычитаемого вычи- тателя, вход п/2 младших разрядов вычитаемого которого соединен с выходом п/2 младших разрядов регистра аргумента, отличающееся тем, что, с целью повышения быстродействия, в него введены блок памяти и мультиплексор, выход которого соединен с входом первого сомножителя матричного умножителя, вход второго сомножителя которого соединен с выходом блока памяти, адресный вход которого соединен с выходом п/2 старших разрядов регистра аргумента и входом п/2 старших разрядов уменьшаемого вычитателя, вход первого и п/2 старших разрядов вычитаемого которого соединен с входом логического нуля , выход вычитателя соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходом матричного умножителя.

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1983 |

|

SU1125623A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1335985A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-10-04—Подача