Изобретение относится к автоматике, вычислительной технике и может использоваться в автономных системах П1 ёобразования и кодирования информации.

Целью изобретения является повышение быстродействия преобразователя.

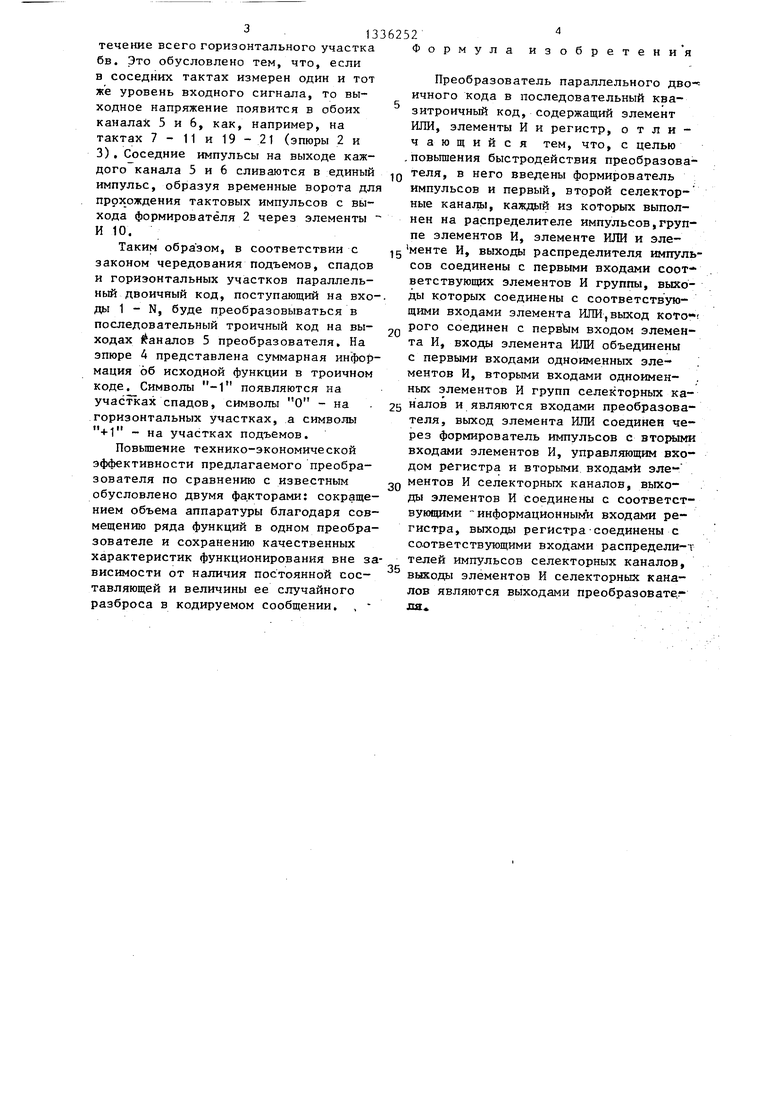

На фиг, 1 показана функциональная схема преобразователя; на фиг, 2 - временные диаграммы, поясняющие его работу.

Преобразователь содержит элемент ИЛИ 1, формирователь 2 импульсов, элементы И 3, регистр 4 и первый, второй селекторные каналы 5 и 6, каждый из KoTopbix выполнен на распределителе 7 импульсов, элементах И 8, объединенных в группу, элементе ИЛИ 9 и элементе И 10,

Преобразователь работает следующим образом.

На входы преобразователя на каждом такте преоб.разования поступает Nзначный параллельный двоичный, код еди-25 который поступит одновременно через

ничного веса.

Если сопоставить входной сигнал и его пр,оизводную (соответственно эпюры 1 и 4 на фиг, 2), то участкам спадов аб, гд, жз будут соответствовать участки отрицательной полярности производной, участкам подъемов вг, еж - участки положительной полярности, а горизонтальным участкам - участки нулевого уровня на эпюре 4, Таким образом, знаковая функция производной входного сигнала представляет собой трехуровневую функцию, дискретизация которой тактовыми импульсами 1 - 29 на эпюре 1 приводит к последовательному троичному коду. Так как ЭВМ строят из двоичных элементов, то преобразователь должен содержать 2 канала: канал для селектирования символов +1 и О (эпюра 3) и .канал для символов -1 и О (эпюра 2), Нетрудно видеть, что информация об индивидуальных особенностях входного сигнала сохраняется, тюскольку суммирование символов на эпюрах 2 и 3 приводит к эпюре 4,

Структура преобразователя при сопряжении его с многоканальным выходом существенно упрощается, так как формирование трехуровневой знаково функции производной входного сигнала осуществляется без предварительного, дифференцирования и клиппирования ; сигнала. Чтобы в этом убедиться, достаточно рассмотреть характер преобразований на одном из участков входного сигнала, например, на участке подъема,

В этом случае с каждым последующим тактом измерений амплитуда, т,е, номер входа преобразователя,в котором появляется импульс, растет. Например,

0 при зонд ировании участка вг (эпюра 1) на тактах 9-16 номера уровней растут от О до (i-2) и т,д. Поэтому достаточно отселектировать последовательность выходных импульсов на участках

5 подъемов в один канал, а на участках спадов - в другой канал.

Суть преобразований,включающих дифференцирование, клиппирование, дискретизацию, заключается в следую0 щем.

Пусть в первом такте измеренное значение входного сигнала соответствует i-му уровню, В этом случае на i-м входе появится импульс напряжения.

35

открытые элементы И 3 на 1-вход i- го триггера регистра 4 и на вторые входы i-x элементов И, На первые входы последних в этом так те ничего не

30 поступает, поэтому напряжение на выг ходах элементов И равно О, Оно возникает только,в последующих тактах, когда одновременно с появлением импульса на одном из информационных вхо входов появится задержанный импульс на выходе триггера регистра 4 и через диодные цепи распределителя 7 поступит на первые входы соответствующих элементов И 8,

40 Согласно эпюрам 1 и 2 во втором такте появится импульс на (1-2) входе, В это же время появится импульс на выходе триггера регистра 4, так как на его К-вход поступит тот же импульс через элемент ИЛИ 1, формирователь 2 и вернет триггер Т. регистра 4 в исходное состояние. Выходное напряжение этого триггера через диодные распределители 7 откроет по первым входам элементы И 8 с номерами ниже i-ro в первом канале 5 и с номерами выше i-ro во втором канале 6, Следовательно, выходной импульс появится в канале 5, который селектирует участки спадов функции.

45

50

55

Выходные импульсы в канале 5 будут появляться не только до момента окончания участка спада иб, но и в

течение всего горизонтального участка бв. Это обусловлено там, что, если в соседних тактах измерен один и тот же уровень входного сигнала, то выходное напряжение появится в обоих каналах 5 и 6, как, например, на тактах 7 - 11 и 19 - 21 (эпюры 2 и 3) . Соседние импульсы на выходе каждого канала 5 и 6 сливаются в единый импульс, образуя временные ворота для прохождения тактовых импульсов с выхода формирователя 2 через элементы И 10.

Таким образом, в соответствии с законом чередования подъемов, спадов и горизонтальных участков параллельный двоичный код, поступающий на входы 1 - N, буде преобразовываться в последовательный троичный код на выходах аналов 5 преобразователя. На эпюре 4 представлена суммарная информация об исходной функции в троичном коде. Символы -1 появляются на участках спадов, символы О - на горизонтальных участках, а символы +1 - на участках подъемов.

Повышение технико-экономической эффективности предлагаемого преобразователя по сравнению с известньш обусловлено двумя факторами: сокращением объема аппаратуры благодаря совмещению ряда функций в одном преобразователе и сохранению качественных характеристик функционирования вне зависимости от наличия постоянной составляющей и величины ее случайного разброса в кодируемом сообщении, , 5

Формула изобретения

Преобразователь параллельного ичного кода в последовательный квазитроичный код, содержащий элемент ИЛИ, элементы И и регистр, отличающийся тем, что, с целью ,повьшения быстродействия преобразоваQ теля, в него введены формирователь импульсов и первый, второй селекторные каналы, каждый из которых выполнен на распределителе импульсов,группе элементов И, элементе ИЛИ и эле- менте И, выходы распределителя импульсов соединены с первыми входами соот- ветствуюпщх элементов И группы, выходы которых соединены с соответствующими входами элемента ИЛИ,выход кото- рого соединен с первом входом элемента И, входы элемента ИЛИ объединены с первыми входами одноименных элементов И, вторьши входами одноименных элементов И групп селекторных ка5 налов и являются входами преобразователя, выход элемента ИЛИ соединен через формирователь импульсов с вторыми входами элементов И, управляющим входом регистра и вторыми входами эле- ментов И селекторных каналов, выходы элементов И соединены с соответствующими -информационными входами регистра, выходы регистрасоединены с соответствующими входами распредели-т телей импульсов селекторных каналов, выходы элементов И селекторных каналов являются выходами преобразовате.г- ля.

0

0

Редактор Н. Егорова

Составитель М, Никуленков

Техред И,Попович Корректор С. Шекмар

Заказ 4055/56Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г„ Ужгород, ул. Проектная, 4

ta -V

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в трехпозиционный код | 1984 |

|

SU1317675A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

| Преобразователь двоичного кода в трехпозиционный код | 1985 |

|

SU1368996A1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1989 |

|

SU1633499A1 |

| Оптоэлектронный преобразователь перемещения в код | 1981 |

|

SU1005133A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для преобразования двоичной последовательности в блочный балансный троичный код | 1986 |

|

SU1324115A1 |

Изобретение относится к автома. Л тике, вычислительной технике и может использоваться в автономных системах преобразования и кодирования информации. Целью изобретения является- повышение быстродействия устройства. Устройство преобразует параллельный двоичный код единичного веса в последо. нательный троичный код. Устройство содержит элемент ИЛИ 1, формирователь 2 импульсов, элемент И 3, регистр 4 и селекторные каналы 5,6,каждый из ко- - торых выполнен на распределителе 7 импульсов, элементах И 8, 10 и элементе ИЛИ 9. 2 ил.

| Тутевич В.Н | |||

| Телемеханика-М.: Высшая школа, 1985, с | |||

| Приспособление для подачи воды в паровой котел | 1920 |

|

SU229A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU857973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-10—Подача