3, состоящий из регистра 5 сдвига и N-канального комбинационного сумматора (ККС) 6. При появлении значащего момента входного сигнала он выделяется в выделителе 2 в виде импульса с длительностью,равной периоду следования импульсов г-ра 1. Если тактовые импульсы опережают (отстают) по фазе значащие моменты входного сигнала, то на выходе формирователя 4 сохраняется (появляется) потенциал логического нуля (единицы) и число на выход ККС 6 будет равно (увели1

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации для тактовой синхронизации принимаемых информационных сигналов.

Цель изобретения - уменьшение времени вхождения в синхронизм при некратном двум значении отношения частот -импульсов задающего генератора и тактовых импульсов входного сигнала.

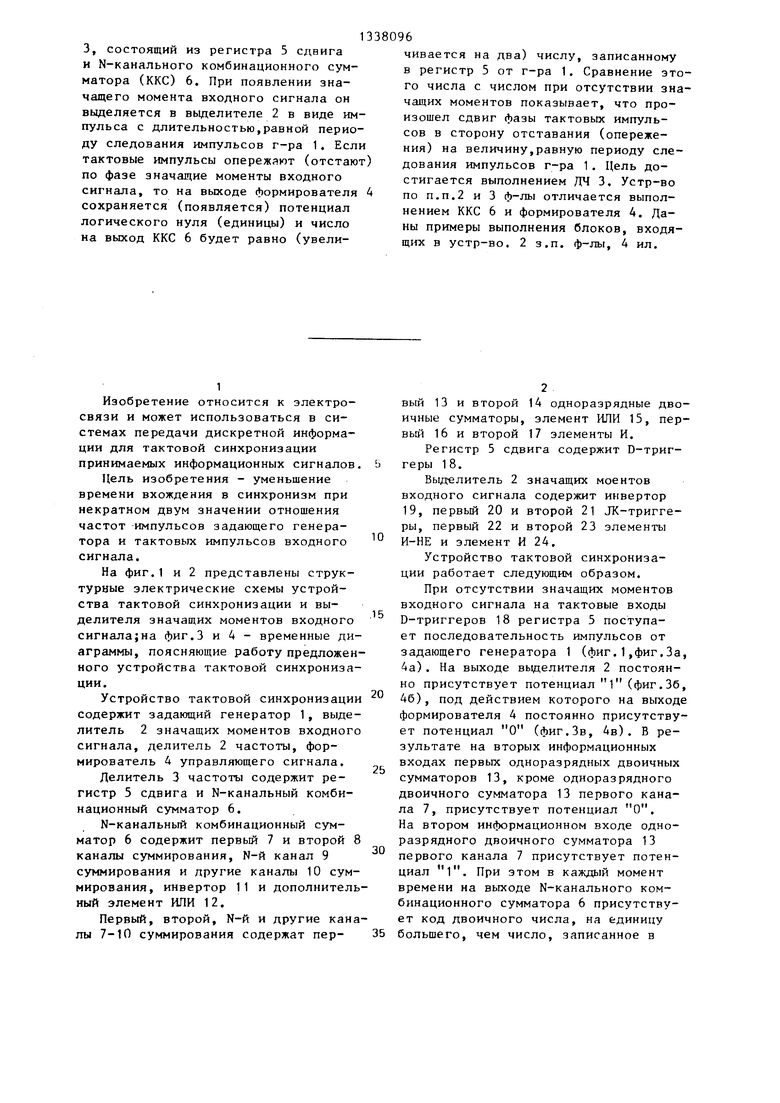

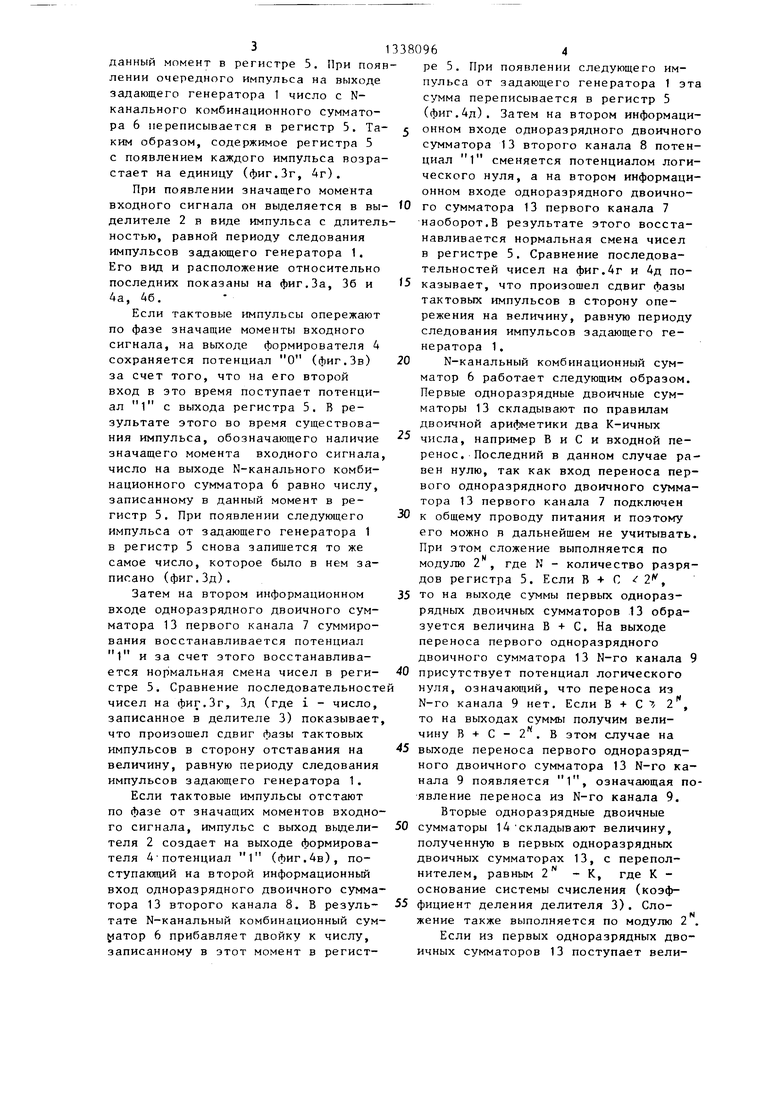

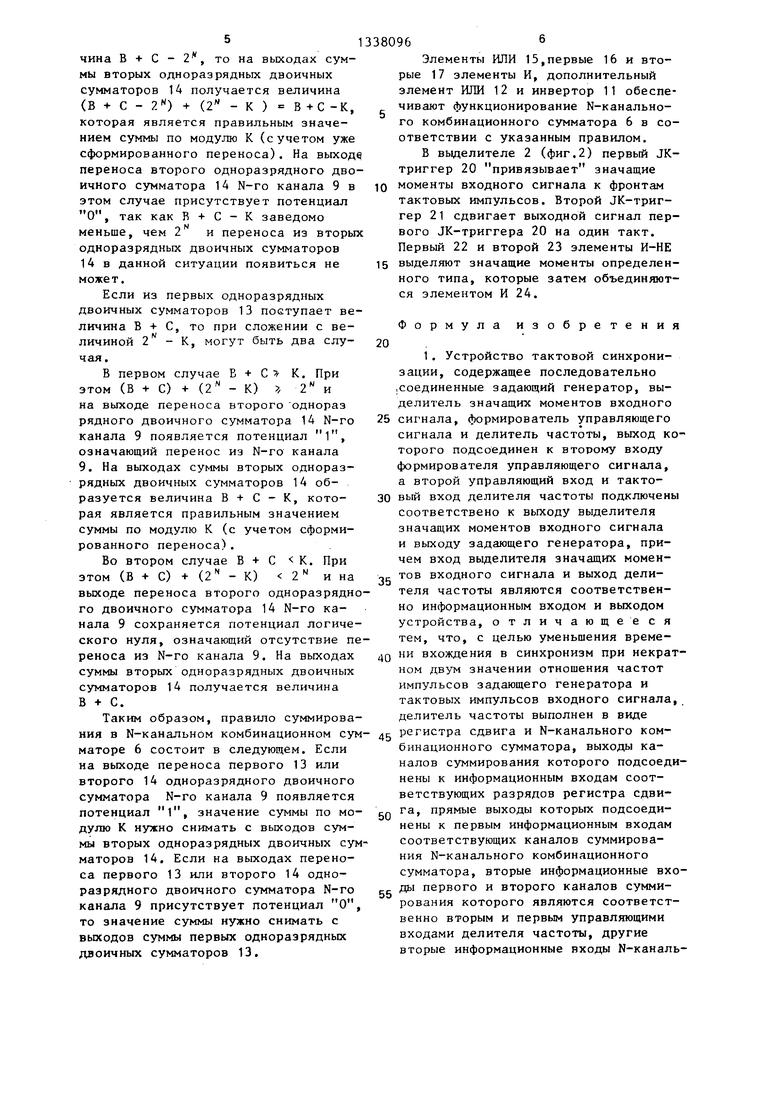

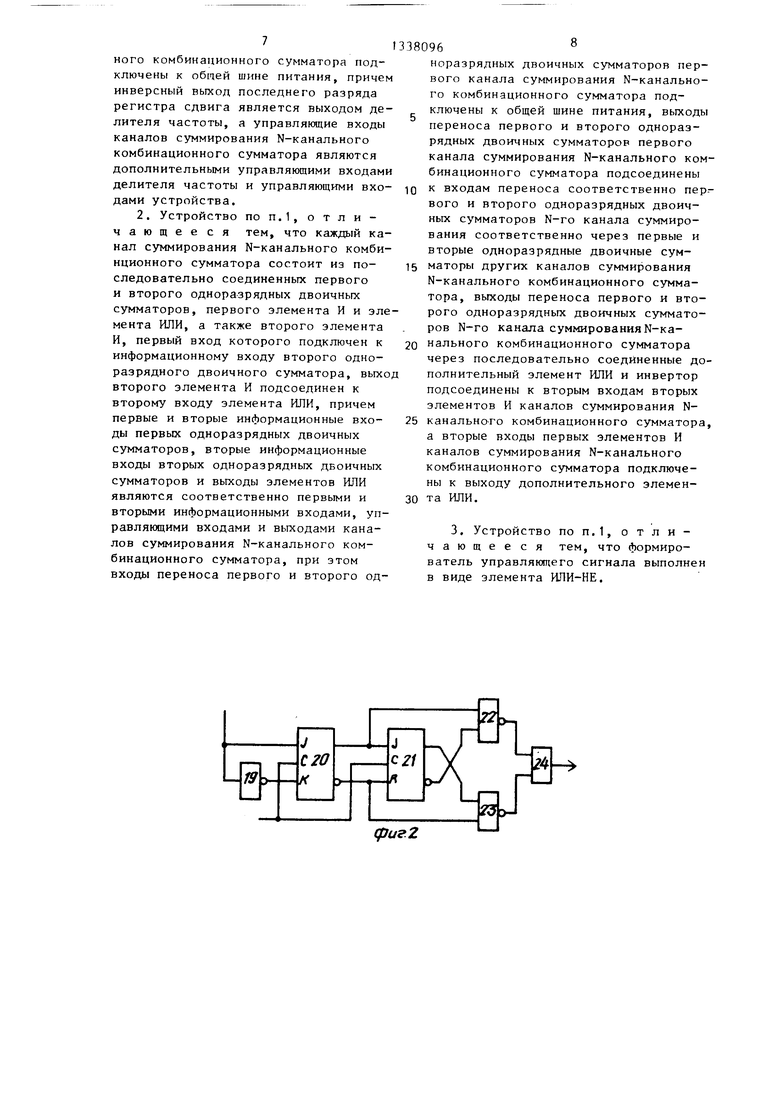

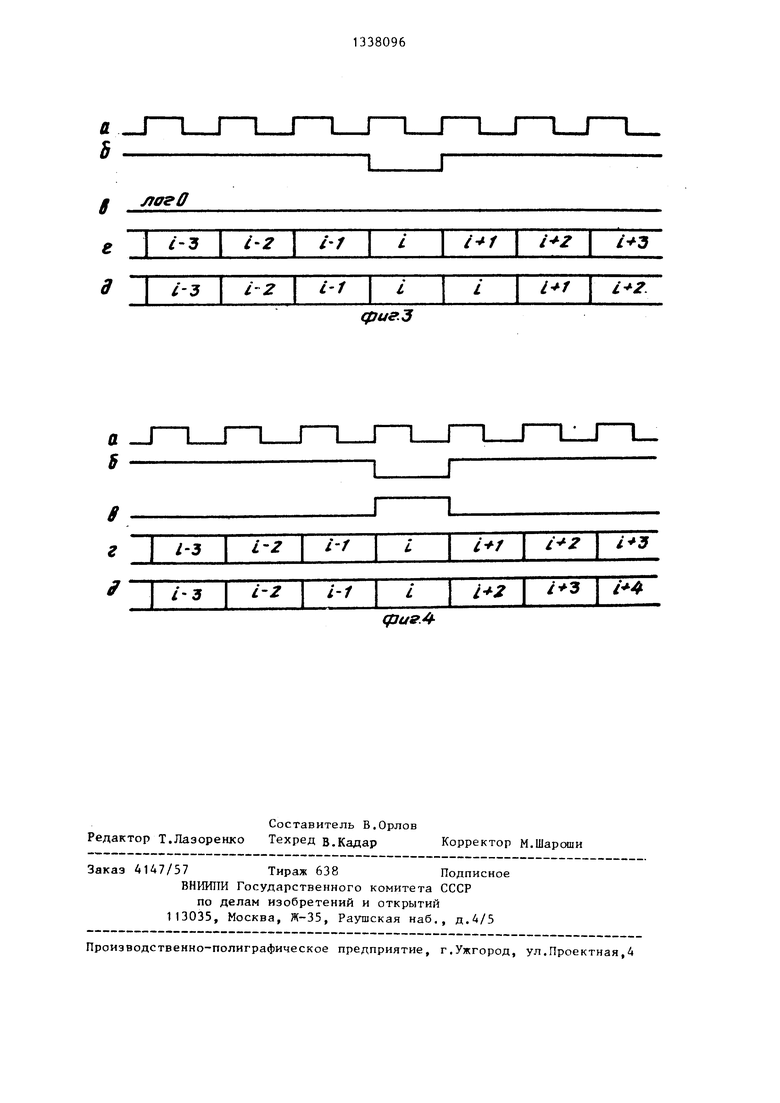

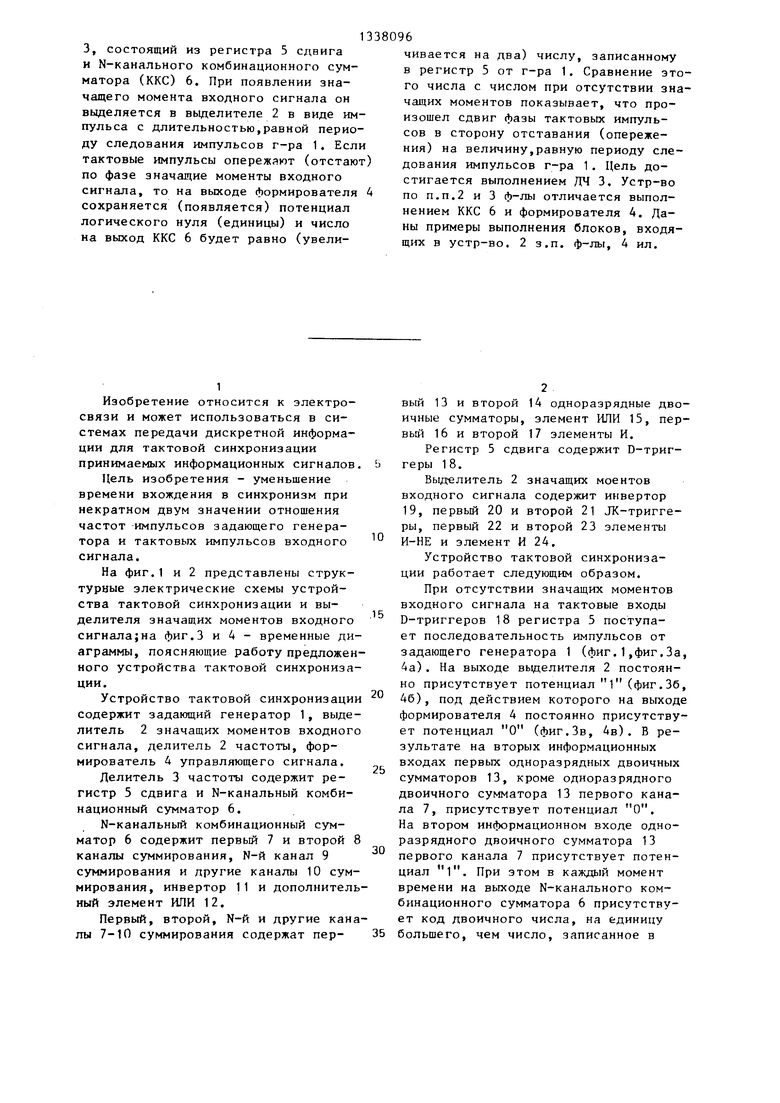

На фиг.1 и 2 представлены структурные электрические схемы устройства тактовой синхронизации и выделителя значащих моментов входного сигнала;на фиг.З и 4 - временные диаграммы, поясняющие работу предложенного устройства тактовой синхронизации.

Устройство тактовой синхронизации содержит задающий генератор 1, выделитель 2 значащих моментов входного сигнала, делитель 2 частоты, формирователь 4 управляющего сигнала.

Делитель 3 частоты содержит регистр 5 сдвига и N-канальный комбинационный сумматор 6.

N-канальный комбинационный сумматор 6 содержит первый 7 и второй 8 каналы суммирования, N-й канал 9 суммирования и другие каналы 10 суммирования, инвертор 11 и дополнительный элемент ИЛИ 12,

Первый, второй, N-й и другие каналы 7-10 суммирования содержат перчивается на два) числу, записанному в регистр 5 от г-ра 1. Сравнение этого числа с числом при отсутствии значащих моментов показывает, что произошел сдвиг фазы тактовых импульсов в сторону отставания (опережения) на величину,равную периоду следования импульсов г-ра 1, Цель достигается выполнением ДЧ 3. Устр-во по п,п.2 и 3 ф-лы отличается выполнением ККС 6 и формирователя 4. Даны примеры выполнения блоков, входящих в устр-во. 2 з.п. ф-лы, 4 ил.

0

5

0

5

0

5

вый 13 и второй 14 одноразрядные двоичные сумматоры, элемент ИЛИ 15, первый 16 и второй 17 элементы И.

Регистр 5 сдвига содержит D-триг- геры 18.

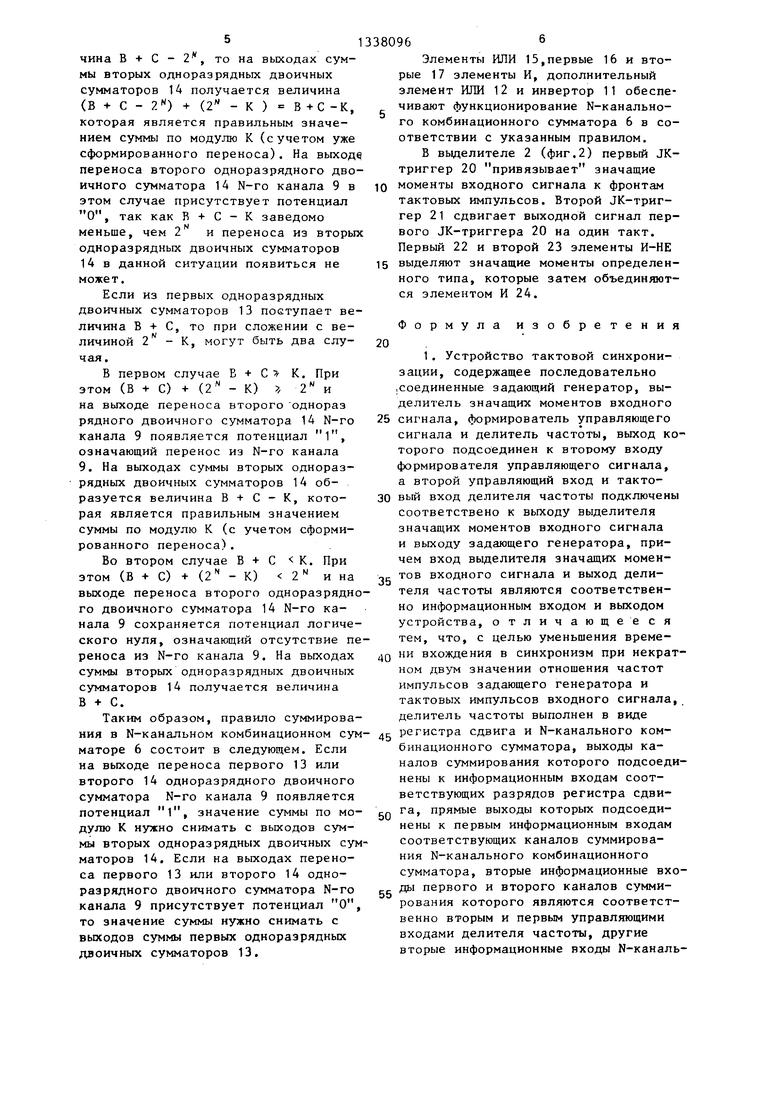

Выделитель 2 значащих моентов входного сигнала содержит инвертор 19, первый 20 и второй 21 JK-тригге- ры, первый 22 и второй 23 элементы И-НЕ и элемент И 24.

Устройство тактовой синхронизации работает следующим образом.

При отсутствии значащих моментов входного сигнала на тактовые входы D-триггеров 18 регистра 5 поступает последовательность импульсов от задающего генератора 1 (фиг.1,фиг,За, 4а). На выходе выделителя 2 постоянно присутствует потенциал 1 (фиг.Зб, 4б), под действием которого на выходе формирователя 4 постоянно присутствует потенциал О (фиг.Зв, 4в). В результате на вторых информационных входах первых одноразрядных двоичных сумматоров 13, кроме одноразрядного двоичного сумматора 13 первого канала 7, присутствует потенциал О. На втором информационном входе одноразрядного двоичного сумматора 13 первого канала 7 присутствует потенциал l. При этом в каждый момент времени на выходе N-канального комбинационного сумматора 6 присутствует код двоичного числа, на единицу большего, чем число, записанное в

данный момент в регистре 5. При поялении очередного импульса на выходе задающего генератора 1 число с N- канального комбинационного сумматора 6 переписывается в регистр 5. Таким образом, содержимое регистра 5 с появлением каждого импульса возрастает на единицу (фиг.Зг, 4г).

При появлении значащего момента входного сигнала он выделяется в выделителе 2 в виде импульса с длителностью, равной периоду следования импульсов задающего генератора 1. Его вид и расположение относительно последних показаны на фиг,За, Зб и Аа, Аб.

Если тактовые импульсы опережают по фазе значащие моменты входного сигнала, на выходе формирователя 4 сохраняется потенциал О (фиг.Зв) за счет того, что на его второй вход в это время поступает потенциал 1 с выхода регистра 5. В результате этого во время существования импульса, обозначающего наличие значащего момента входного сигнала число на выходе N-канального комбинационного сумматора 6 равно числу, записанному в данный момент в регистр 5. При появлении следующего импульса от задающего генератора 1 в регистр 5 снова запишется то же самое число, которое было в нем записано (фиг.Зд).

Затем на втором информационном входе одноразрядного двоичного сумматора 13 первого канала 7 суммирования восстанавливается потенциал 1 и за счет этого восстанавливается нормальная смена чисел в регистре 5. Сравнение последовательност чисел на фиг.Зг, Зд (где i - число, записанное в делителе 3) показывает что произошел сдвиг фазы тактовых импульсов в сторону отставания на величину, равную периоду следования импульсов задающего генератора 1.

Если тактовые импульсы отстают по фазе от значащих моментов входного сигнала, импульс с выход выделителя 2 создает на выходе формирователя 4-потенциал 1 (фиг.4в), поступающий на второй информационный вход одноразрядного двоичного сумматора 13 второго канала 8. В результате N-канальный комбинационный сум tJaTop 6 прибавляет двойку к числу, записанному в этот момент в регистре 5. При появлении следующего импульса от задающего генератора 1 эта сумма переписывается в регистр 5 (фиг.4д). Затем на втором информационном входе одноразрядного двоичного сумматора 13 второго канала 8 потенциал 1 сменяется потенциалом логического нуля, а на втором информационном входе одноразрядного двоичного сумматора 13 первого канала 7 наоборот.В результате этого восстанавливается нормальная смена чисел в регистре 5. Сравнение последовательностей чисел на фиг.4г и 4д показывает, что произошел сдвиг фазы тактовых импульсов в сторону опережения на величину, равную периоду следования импульсов задающего генератора 1.

N-канальный комбинационный сумматор 6 работает следующим образом. Первые одноразрядные двоичные сумматоры 13 складывают по правилам двоичной арифметики два К-ичных

числа, например В и С и входной перенос. Последний в данном случае равен нулю, так как вход переноса первого одноразрядного двоичного сумматора 13 первого канала 7 подключен

к общему проводу питания и поэтому его можно в дальнейшем не учитывать. При этом сложение выполняется по модулю 2 , где N - количество разрядов регистра 5. Если В С - 2,

то на выходе суммы первых одноразрядных двоичных сумматоров 13 образуется величина В + С. На выходе переноса первого одноразрядного двоичного сумматора 13 N-ro канала 9

присутствует потенциал логического нуля, означающий, что переноса из N-ro канала 9 нет. Если В + С / 2 , то на выходах суммы получим величину В -I- С - 2 .В этом случае на

выходе переноса первого одноразрядного двоичного сумматора 13 N-ro канала 9 появляется 1, означающая появление переноса из N-ro канала 9. Вторые одноразрядные двоичные

сумматоры 14 складывают величину, полученную в первых одноразрядных двоичных сумматорах 13, с перепол- нителем, равным 2 К, где К - основание системы счисления (коэффициент деления делителя 3). Слоо N

жение также выполняется по модулю 2 . Если из первых одноразрядных двоичных сумматоров 13 поступает вели5

чина В + С - 2, то на выходах суммы вторых одноразрядных двоичных сумматоров 14 получается величина (В -t- С - Z ) + (2 - К ) B-t-C-K, которая является правильным значением суммы по модулю К (с учатом уже сформированного переноса). На выход переноса второго одноразрядного двоичного сумматора 14 N-ro канала 9 в этом случае присутствует потенциал О, так как R + С - К заведомо меньше, чем 2 и переноса из вторы одноразрядных двоичных сумматоров 14 в данной ситуации появиться не может.

Если из первых одноразрядных двоичных сумматоров 13 поступает величина В + С, то при сложении с величиной 2 - К, могут быть два случая,

В первом случае В + С К. При этом (В + С) + (2 - К) . 2 и на выходе переноса второго однораз рядного двоичного сумматора 14 N-ro канала 9 появляется потенциал 1, означающий перенос из N-ro канала 9. На выходах суммы вторых одноразрядных двоичных сумматоров 14 образуется величина В + С - К, которая является правильным значением суммы по модулю К (с учетом сформированного переноса).

Во втором случае В + С К. При этом (В + С) + (2 - К) 2 и на выходе переноса второго одноразрядного двоичного сумматора 14 N-ro канала 9 сохраняется потенциал логического нуля, означающий отсутствие переноса из N-ro канала 9. На выходах суммы вторых одноразрядных двоичных сумматоров 14 получается величина В + С.

Таким образом, правило суммирования в N-канальном комбинационном сумматоре 6 состоит в следующем. Если на выходе переноса первого 13 или второго 14 одноразрядного двоичного сумматора N-ro канала 9 появляется потенциал 1, значение суммы по модулю К нужно снимать с выходов суммы вторых одноразрядных двоичных сумматоров 14. Если на выходах переноса первого 13 или второго 14 одноразрядного двоичного сумматора N-ro канала 9 присутствует потенциал О то значение суммы нужно снимать с выходов суммы первых одноразрядных двоичных сумматоров 13.

10

15

20

25

380966

Элементы ИЛИ 15,первые 16 и вторые 17 элементы И, дополнительный элемент ИЛИ 12 и инвертор 11 обеспечивают функционирование N-канально- го комбинационного сумматора 6 в соответствии с указанным правилом.

В выделителе 2 (фиг.2) первый JK- триггер 20 привязывает значащие моменты входного сигнала к фронтам тактовых импульсов. Второй JK-триг- гер 21 сдвигает выходной сигнал первого JK-триггера 20 на один такт. Первый 22 и второй 23 элементы И-НЕ выделяют значащие моменты определенного типа, которые затем объединяются элементом И 24.

Формула изобретения

1. Устройство тактовой синхронизации, содержащее последовательно .соединенные задающий генератор, выделитель значащих моментов входного сигнала, формирователь управляющего сигнала и делитель частоты, выход которого подсоединен к второму входу формирователя управляющего сигнала, а второй управляющий вход и тактовый вход делителя частоты подключены соответствено к выходу выделителя значащих моментов входного сигнала и выходу задающего генератора, причем вход выделителя значащих моментов входного сигнала и выход делителя частоты являются соответственно информационным входом и выходом устройства, отличающееся тем, что, с целью уменьщения времени вхождения в синхронизм при некратном двум значении отношения частот импульсов задающего генератора и тактовых импульсов входного сигнала, делитель частоты выполнен в виде регистра сдвига и N-канального комбинационного сумматора, выходы каналов суммирования которого подсоединены к информационным входам соответствующих разрядов регистра сдвига, прямые выходы которых подсоединены к первым информационным входам соответствующих каналов суммирования N-канального комбинационного сумматора, вторые информационные входы первого и второго каналов суммирования которого являются соответственно вторым и первым управляющими входами делителя частоты, другие вторые информационные входы N-каналь30

35

40

45

50

55

7

ного комбинационного сумматора подключены к общей шине питания, причем инверсный выход последнего разряда регистра сдвига является выходом делителя частоты, а управляющие входы каналов суммирования N-канального комбинационного сумматора являются дополнительными управляющими входами делителя частоты и управляющими входами устройства.

2. Устройство по П.1, отличающее ся тем, что каждый канал суммирования N-канального комби- нционного сумматора состоит из последовательно соединенных первого и второго одноразрядных двоичных сумматоров, первого элемента И и элемента ИЛИ, а также второго элемента И, первый вход которого подключен к информационному входу второго одноразрядного двоичного сумматора, выхо второго элемента И подсоединен к второму входу элемента ИЛИ, причем первые и вторые информационные входы первых одноразрядных двоичных сумматоров, вторые информационные входы вторых одноразрядных двоичных сумматоров и выходы элементов ИЛИ являются соответственно первыми и вторыми информационными входами, управляющими входами и выходами каналов суммирования N-канального комбинационного сумматора, при этом входы переноса первого и второго од38096°

норазрядных двоичных сумматоров первого канала суммирования N-канального комбинационного сумматора подключены к общей шине питания, выходы переноса первого и второго одноразрядных двоичных сумматоров первого канала суммирования N-канального комбинационного сумматора подсоединены

1Q к входам переноса соответственно первого и второго одноразрядных двоичных сумматоров N-ro канала суммирования соответственно через первые и вторые одноразрядные двоичные сум15 маторы других каналов суммирования N-канального комбинационного сумматора, выходы переноса первого и второго одноразрядных двоичных сут мато- ров N-ro канала суммирования N-ка20 нального комбинационного сумматора через последовательно соединенные дополнительный элемент ИЛИ и инвертор подсоединены к вторым входам вторых элементов И каналов суммирования N25 канального комбинационного сумматора, а вторые входы первых элементов И каналов суммирования N-канального комбинационного сумматора подключены к выходу дополнительного элемен30 та ИЛИ.

3. Устройство по П.1, о т л и - чающееся тем, что формирователь управлякнцего сигнала выполнен в виде элемента ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Устройство для деления | 1980 |

|

SU928344A1 |

Изобретение относится к электросвязи. Цель изобретения - уменьшение времени вхождения в синхронизм при некратном двум значении отношения частот импульсов задающего г-ра и тактовых импульсов входного сигнала. Устр-во содержит задаюий г-р 1, выделитель 2 значащих моментов входного сигнала, формирователь 4 управляющего сигнала и делитель частоты (ДЧ) i (Л со со 00 о со О5 фиг I

CpueZ

а Ъ

i е

а

фи.З

(f3u9.

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1980 |

|

SU886287A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство тактовой синхронизации | 1977 |

|

SU661833A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-15—Публикация

1985-07-16—Подача