изобретение относится к вычнсли- тепьной технике и может быть использовано ;для создания последовательно-параллельных преобразователей кодов.

Цель изобретения - упрощение устройства .

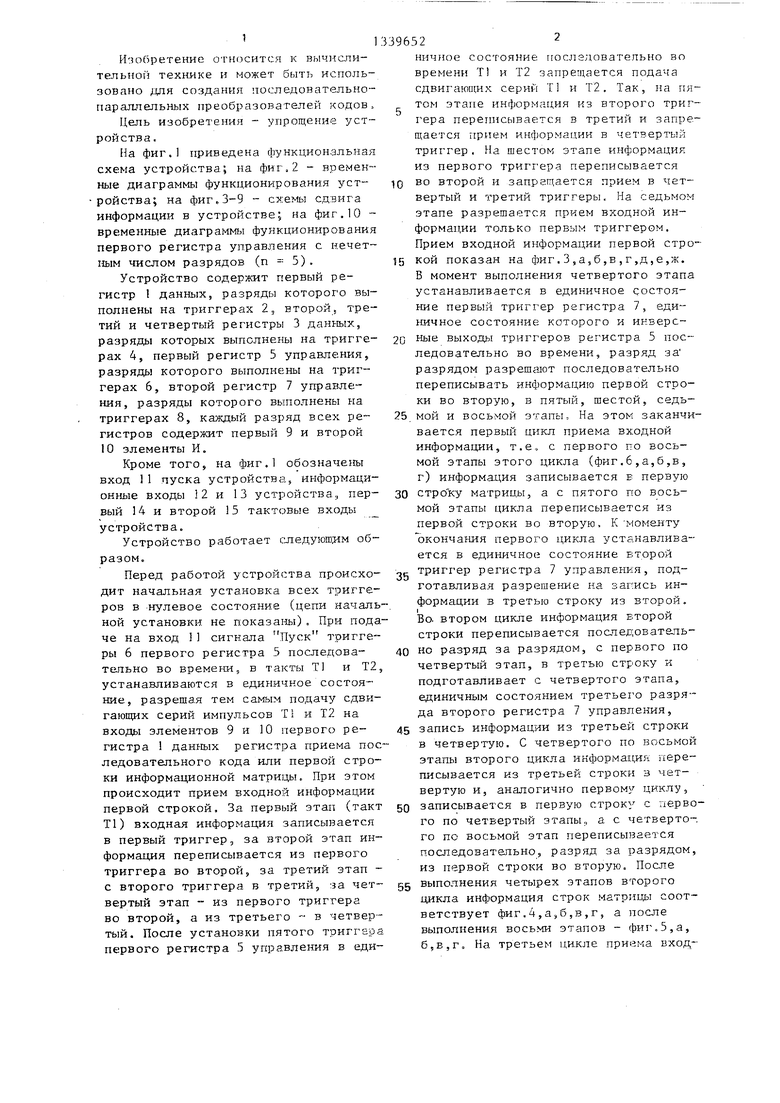

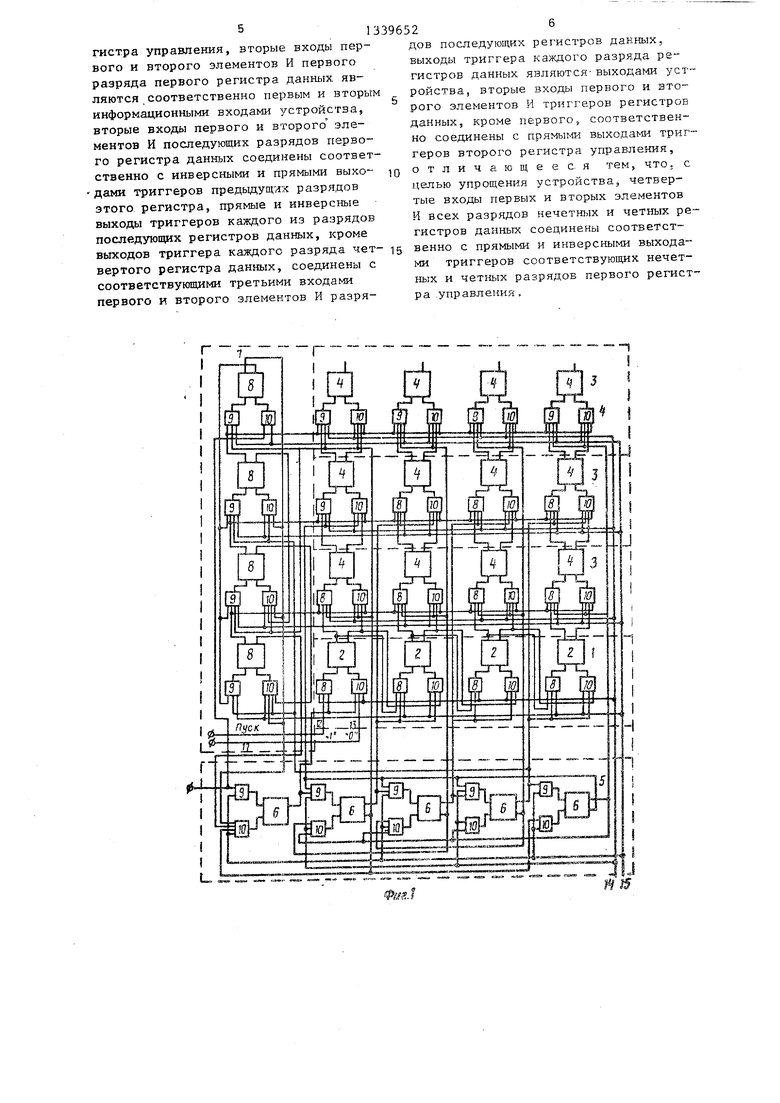

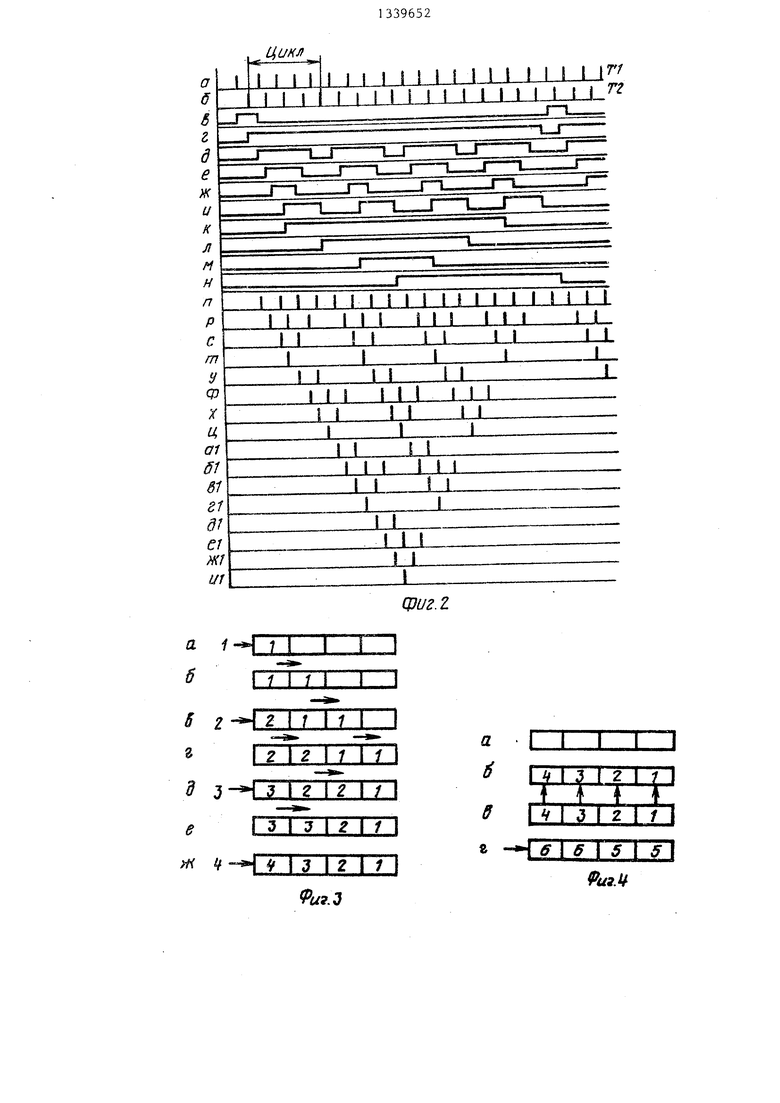

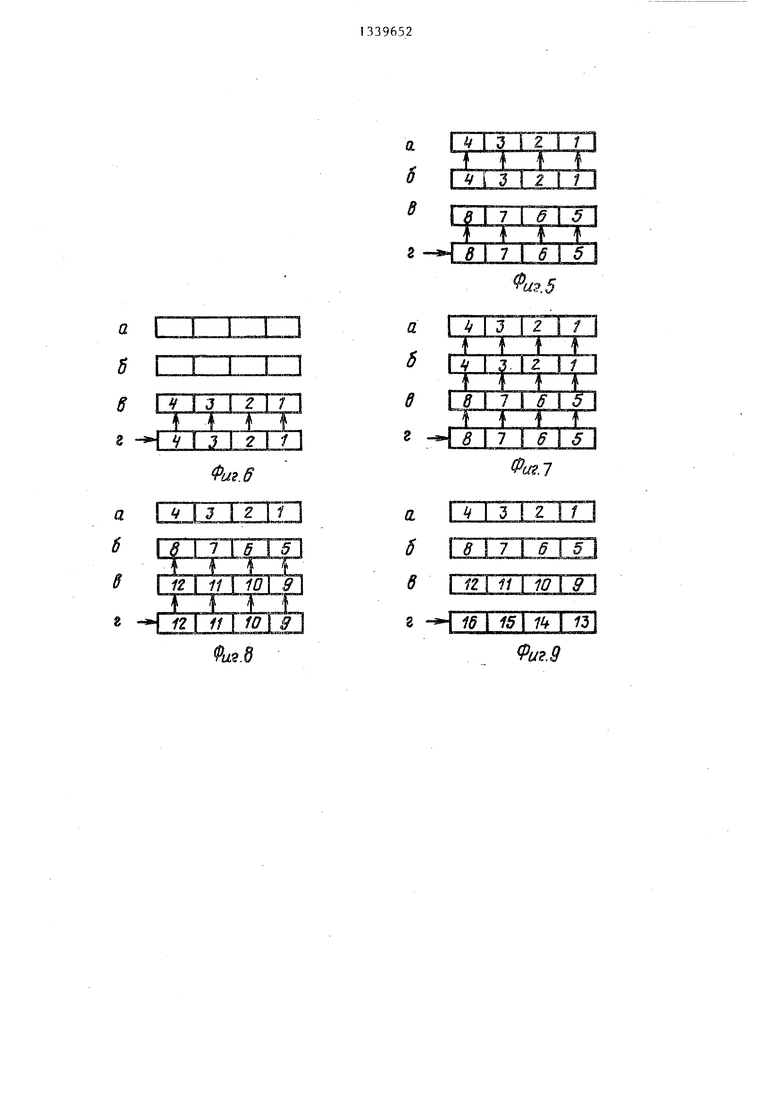

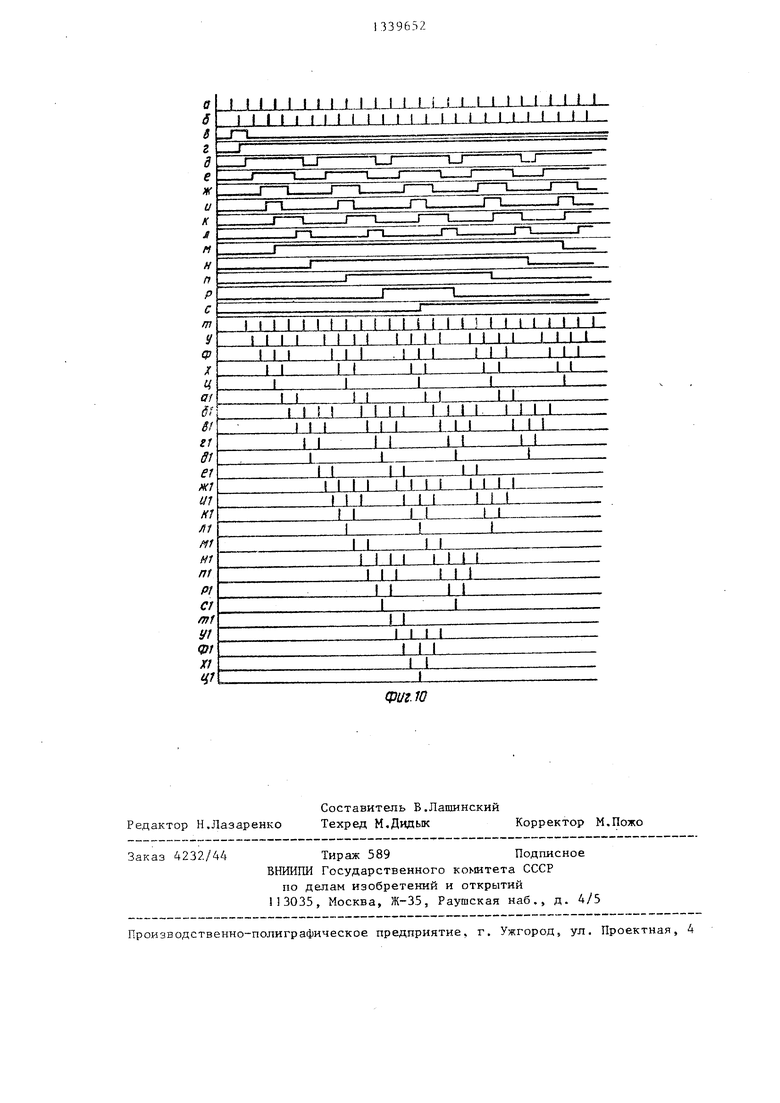

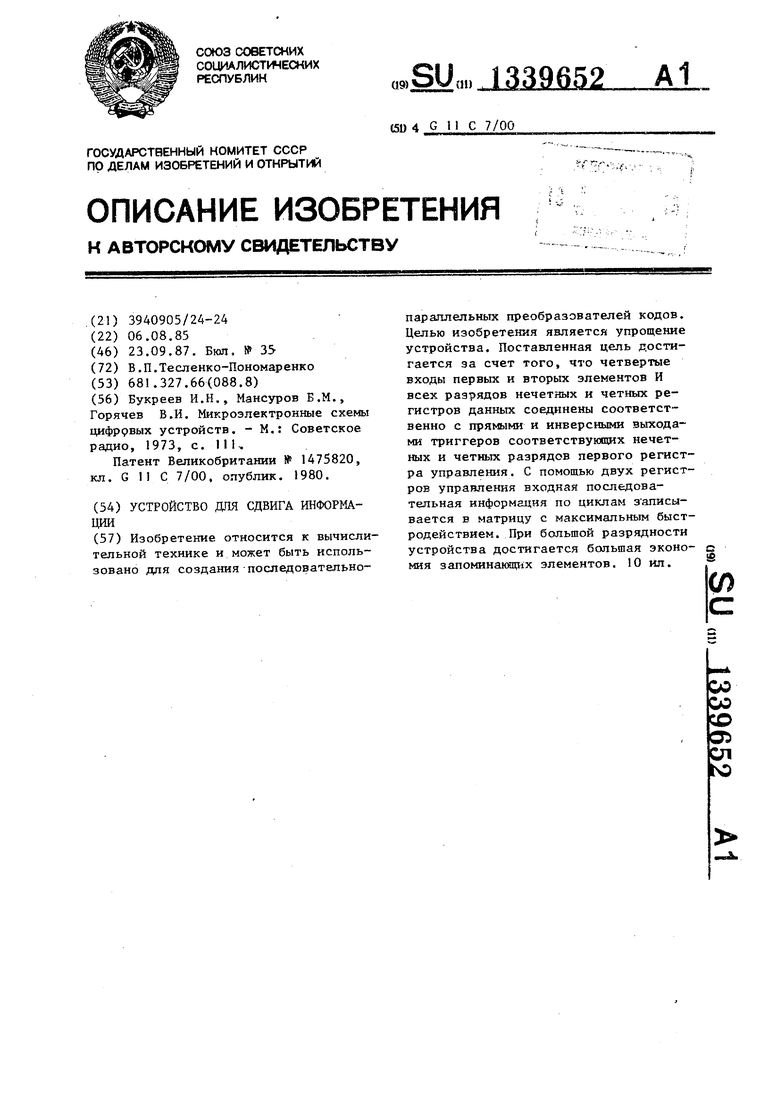

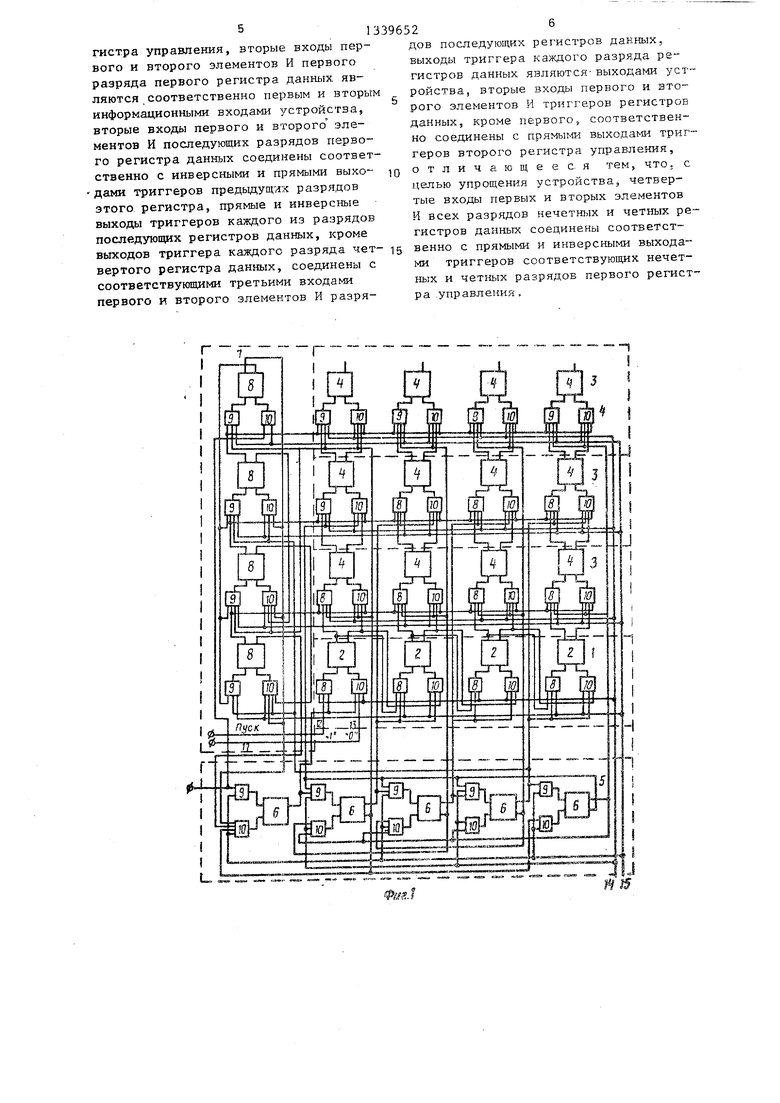

На фиг.1 приведена функциональная схема устройства; на фиг.2 - временные диаграммы функционирования устройства; на - схемы сдвига информации в устройстве; на фиг.10 - временные диаграммы функционирования первого регистра управления с нечетным числом разрядов (п 5) .

Устройство содержит первый регистр данных, разряды которого выполнены на триггерах 2, второй, третий и четвертый регистры 3 данных, разряды которых выполнены на триггерах 4, первый регистр 5 управления, разряды которого выполнены на триггерах 6, второй регистр 7 управления, разряды которого выполнены на триггерах 8, каждый разряд всех регистров содержит первый 9 и второй 10 элементы И,

Кроме того, на фиг.1 обозначены вход 11 пуска устройства, информационные входы 2 и 13 устройства., первый 14 и второй 15 тактовые входы устройства.

Устройство работает следуюш м образом.

Перед работой устройства происходит начальная установка всех триггеров в нулевое состояние (цепи начальной установки не показав) . При подаче на вход 1 сигнала Пз ск триггеры 6 первого регистра 5 последова- тапьно во времени, в такты Т1 и 12 устанавливаются в единичное состояние, разрешая тем самым подачу сдвигающих серий импульсов Т1 и Т2 на входы элементов 9 и 10 первого регистра данных регистра приема последовательного кода или первой строки информационной матр№з з1. При этом происходит прием входной информации первой строкой. За первый этап (такт Т1) входная информация записывается в первый триггер, за второй этап информация переписывается из первого триггера во второй, за третий этап - с второго триггера в третий, за четвертый этап -- из первого триггера во второй, а из третьего в четвертый. После установки пятого триггера первого регистра 5 управления в еди396522

ничиое состояние послаловательно во времени Т1 и Т2 запрещается подача сдвигающих серий Т1 и Т2. Так, на пя- J. том этапе, информация из второго триггера переписывается в третий и запрещается прием информации в четвертый триггер, На шестом этапе информация из первого триггера переписывается

19во второй и запрещается прием в четвертый и третий триггеры. На седьмом этапе разрешается прием входной информации только первым триггером. Прием входной информации первой стро15 кой показан на фиг.3,а,б,в,г,д,е,ж. Б момент выполнения четвертого этапа устанавливается в единичное состояние первый триггер регистра 7, единичное состояние которого и инверс20ные выходы триггеров регистра 5 последовательно во времени, разряд за разрядом разрешают последовательно переписывать информацию первой строки во вторую, в пятый, шестой, седь25 мой и восьмой этапы. На этом заканчивается первый цикл приема входной информации, т.е. с первого по восьмой этапы этого цикла (фиг.б,а,б,в, г) информация записывается в первую

30 строку матрицы, а с пятого по восьмой этапы цикла переписывается из первой строки во вторую, К моменту окончания первого цикла устанавливается в единичное состояние второй

„ триггер регистра 7 управления, подготавливая разрешение на запись информации в третью строку из второй. Во. втором цикле информация второй строки переписывается последователь40 но разряд за разрядом, с первого по четвертый этап, в третью строку и подготавливает с четвертого этапа, единичным состоянием третьего разряда второго регистра 7 управления,

45 запись информации из третьей строки в четвертую. С четвертого по восьмой этапы второго цикла информация переписывается из третьей строки з четвертую и, аналогично первому циклу,

50 записывается в первую строку с первого по четвертый этапы,, а с четверто-. го по восьмой этап переписывается последовательно, разряд за разрядом, из первой строки во вторую. После

55 выполнения четырех этапов второго цикла информация строк матрицы соответствует фиг.4,а,б,в,г, а 1осле выполнения восьми этапов - фиг.5,а, б, в, г о На. третьем цикле приема входНОН информации запрещается прием информации четвертой строкой; с первого по четвертый этап информация второй строки переписывается в третью, а с четвертого по восьмой этапы переписывается последовательно разряд за разрядом принятая информация первой строкой во вторую (фиг,3,а,б5В, г). На четвертом цикле входная инфор мация принимается только первой строкой фиг.9,а,б.BsF. Таким.образом, входная информация с помощью регистров 5 и 7 управления записывается в информационную матрицу (регистры 1 и 3 данных) Первый регистр 5 управления управляет приемом информации в первую строку, регистры 5 и 7 управления - в остальные строки.

Момент окончания сдвига определяется единичным состоянием последнего

триггера второго регистра 7 управления и единичным состоянием первого регистра 5 управления. Перед работой в нулевое состояние последний триггер второго регистра 7 управления устанавливается сигналом по шине Пуск, благодаря этому в устройстве отпадает необходимость отсчета времени приема входной информации. Аналогичным образом реализуется устройство вьщачи информации из матрицы памяти,

Формула изобретения

Устройство для сдвига информации, содержащее первый и второй регистры Управления и с первого по четвертый регистры данных, каждый разряд которых состоит из первого и второго элементов И, триггера, входы установки и сброса которого соединены с выходами первого и второго элементов И, причем первые входы первого и второго элемента И четных разрядов первого регистра управления и нечетных разрядов всех регистров данных соединены и являются первым тактовым входом устройства, а первые входы первого и второго элементов И нечетных разрядов первого и всех разрядов второго регистров управления и четных разрядов всех регистров данных соединены и являются вторым тактовьм входом устройства, прямой выход триггера каждого разряда, кроме последнего, в регистрах управления соединен с вторым входом первого элемента И последующего разряда, а прямой выход

Дов

5

0

триггера посиеднсго разряди в первом регистре управ-пепия соединен с вторым входом второго элемента И второго, третьего и четвертого разрядов, а прямой выход триггера последнего разряда во втором регистре управления соединен с вторым входом второго элемента И второго и третьего разряи четвертым входом второго элемента И первого разряда данного регистра, вторым входом второго элемента И первого разряда первого регистра управления, инверсные выходы триггеров второго, третьего и четвертого разрядов которого соединены с соответствующим третьим входом второго элемента И в предьщущих разрядах данного регистра, причем инверсный выход триггера второго разряда соединен с вторым входом второго элемента И пятого разряда данного регистра, инверсный выход триггера которого соединен с третьим входом первого

5 элемента И второго, третьего и четвертого разрядов первого регистра управления, четвертый вход второго элемента И первого разряда которого соединен с инверс-ным выходом тригге:ра

0 первого разряда второго регистра управления, инверсные выходы триггеров второго и третьего разрядов которого соединены с cooтвeтcтвyющи ш вторыми входами второго элемента И предьщущих разрядов данного регистра, а инверсный выход триггера четвертого разряда соединен с первым входом первого элемента И других разрядов второго регистра управления, второй

0 вход второго элемента И четвертого разряда которого и второй вход первого элемента И первого разряда первого регистра управления соединены и являются входом пуска устройства,

5 прямой выход триггера четвертого разряда первого регистра управления соединен с третьими входами первого и второго элементов И первого разряда, третьим входом второго элемента И, четвертым входом первого элемента И .

5

0

третьего разряда второго регистра управления инверсный вход триггера второго разряда первого регистра управления соединен с третьим входом первого элемента И четвертого разряда второго регистра управления и четвертыми входами первого и второго элементов И второго разряда второго регистра управления, вторые входы первого и второго элементов И первого азряда первого регистра данных явяются соответственно первым и вторым информационными входами устройства, вторые входы первого и второго элементов И последующих разрядов первого регистра данных соединены соответственно с инверсш,ми и прямыми выхо- 10 дами триггеров предьщущих разрядов этого регистра, прямые и инверсные выходы триггеров каждого из разрядов последующих регистров данных, кроме выходов триггера каждого разряда чет- 15 вертого регистра данных, соединены с соответствующими третьими входами первого и второго элементов И разрядов последующих регистров данных, выходы триггера каждого разряда регистров данных являются-выходами устройства, вторые входы первого и второго элементов И триггеров регистров данных, кроме первого, соответственно соединены с прямы1-ш выходами триггеров второго регистра управления, отличающееся тем, что. с целью упрощения устройства, четвертые входы первых и вторых элементов И всех разрядов нечетшлх и четных регистров данных соединены соответственно с прямыми и инверсными выходами триггеров соответствующих нечетных и четшлх разрядов первого регистра .управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный сдвигающий регистр | 1973 |

|

SU480115A1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1464183A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для вывода информации | 1984 |

|

SU1226438A1 |

| Устройство адресации к динамической памяти | 1987 |

|

SU1444785A1 |

| Устройство для сдвига информации | 1979 |

|

SU1005034A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1481901A1 |

Изобретение относится к вычислительной технике и может быть использовано для создания последовательнопараллельных преобразователей кодов. Целью изобретения является упрощение устройства. Поставленная цель достигается за счет того, что четвертые входы первых и вторых элементов И всех разрядов нечетных и четных регистров данных соединены соответственно с прямыми и инверсными выхода- ми триггеров соответствующих нечетных и четных разрядов первого регистра управления, С помощью двух регистров управления входная последовательная информация по циклам з аписы- вается в матрицу с максимальным быстродействием. При большой разрядности устройства достигается большая экономия запоминакшщх элементов. 10 йл. (О СО СО О5 ел

«j

Фа..1

f/.J

РизМ

а б

ПЮ

ff JYiJ} рг

. t , . . u

2 -4jJ-.iJL2I2 .

QJIJJJJJ

ХГДТЕП

rJL-.,jL,JL. L, СЭТИжСЮ

iZIEIIir

-nlJLLJLL/ Mj

гутгтггп

ULLJJ..1JLIJ

t Л 7 I flf 1

...

АЕ1ГП31

г5

04-JXr i±ii3Zctjtitia

iil

izi

L TjTia

чшоХш

fe.7

СПНХШ

Ежтгю

#

8 -НЖЕЖЕЖП.

Я г

| Букреев И.Н,, Мансуров Б.М., Горячев В.И, Микроэлектронные схемы цифррБых устройств | |||

| - М,: Советское радио, 1973, с | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1987-09-23—Публикация

1985-08-06—Подача