Изобретение относится к вычислительной технике и может быть использовано при построении цифровых систем обработки данных и цифровых управляющих систем на основе микроЭВМ,

Цель изобретения - расширение класса решаемых задач з а счет обес-

печения режимов работы с блоками памяти различных типов.

На фиг. I представлена блок-схема устройства; на фиг. 2 и 3 - функцио-- нальные схемь блока управления и буферного на фиг. 4 и 5 - блок-схемы алгоритмов записи и чтения

25

31501071

дного слова; на фиг, 6 и 7 - вреенные диаграммы циклов записи и чтеия одного слова.

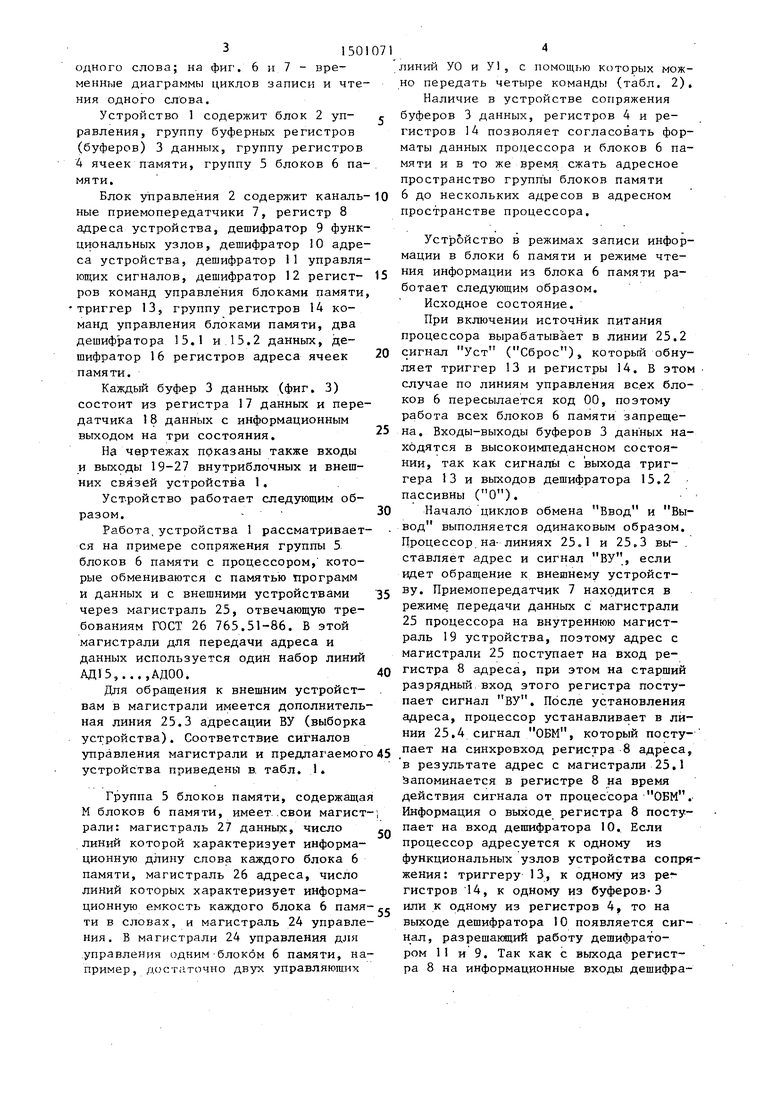

Устрор 1ство 1 содержит блок 2 уп- равления, группу буферных регистров (буферов) 3 данных, группу регистров 4 ячеек памяти, группу 5 блоков 6 памяти.

Блок управления 2 содержит каналь- 10 ные приемопередатчики 7, регистр 8 адреса устройства, дешифратор 9 функциональных узлов, дешифратор 0 адреса устройства, дешифратор 11 управляющих сигналов, дешифратор 12 регист- 15 ров команд управления блоками памяти, триггер 13, группу регистров 14 команд управления блоками памяти, два дешифратора 15.1 и 15.2 данных, дешифратор 16 регистров адреса ячеек 20 памяти.

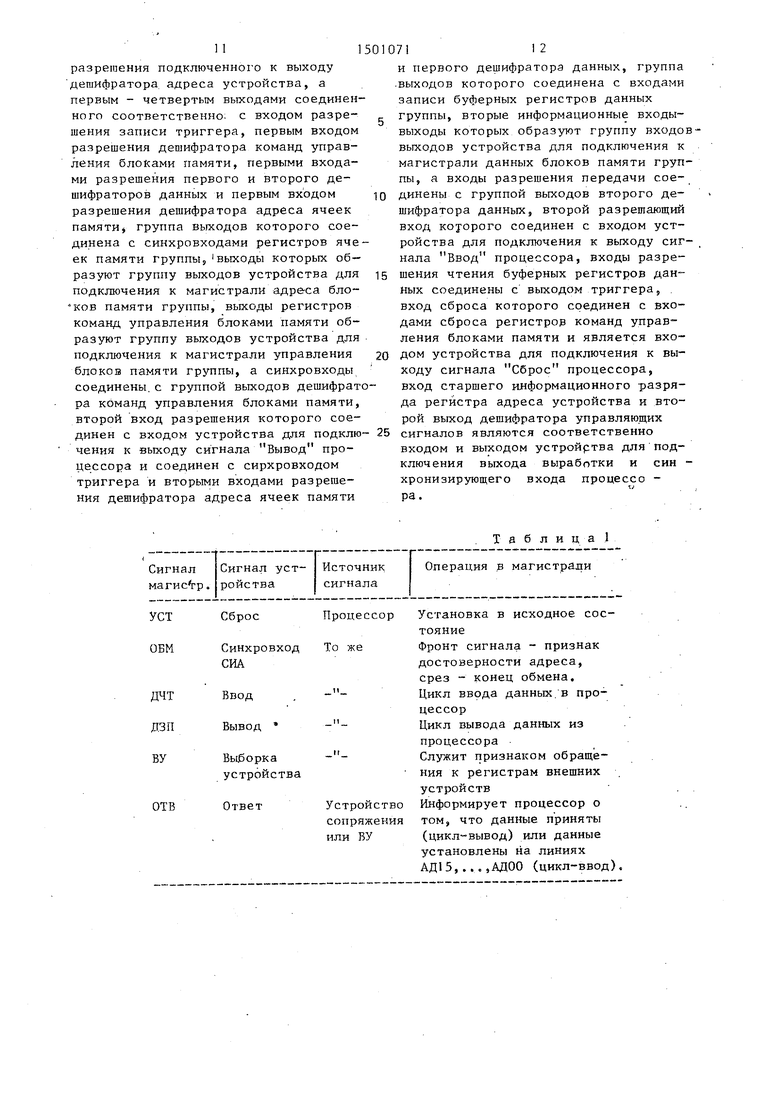

Каждый буфер 3 данных (фиг. 3) состоит из регистра 17 данных и передатчика 18 данных с информационным выходом на три состояния.

На чертежах показаны также входы и выходы 19-27 внутриблочных и внешних связей устройства 1. .

Устройство работает следзпощим образом.-

Работа,устройства 1 рассматривается на примере сопряжения группы 5 блоков 6 памяти с процессором, которые обмениваются с памятью программ и данных и с внешними устройствами 35 через магистраль 25, отвечающую требованиям ГОСТ 26 765.51-86. В этой магистрали для передачи адреса и данных используется один набор линий АД15,...,АДОО.40

Для обращения к внешним устройст- . вам в магистрали имеется дополнительная линия 25.3 адресации ВУ (выборка устройства). Соответствие сигналов управления магистрали и предлаг аемого 45 устройства приведены в. табл. 1.

Группа 5 блоков памяти, содержащая М блоков 6 памяти, имеет, .свои магист-; рали: магистраль 27 данных, число сп линий которой характеризует информационную длину слова каждого блока 6 памяти, магистраль 26 адреса, число линий которых характеризует информационную емкость каждого блока 6 памя-ее ти в словах, и магистраль 24 управления. В магистрали 24 управления для .управления одним-блоком 6 памяти, например, дост;1точно двух управляющих

5

0 5 0

0

5 0

. 5

п е

линий УО и У1, с помощью которых можно передать четыре команды (табл. 2),

Наличие в устройстве сопряжения буферов 3 данных, регистров 4 и регистров 14 позволяет согласовать форматы данных процессора и блоков 6 памяти и в то же время сжать адресное пространство групп ы блоков памяти 6 до нескольких адресов в адресном пространстве процессора.

Устройство в режимах записи информации в блоки 6 памяти и режиме чтения информации из блока 6 памяти работает следующим образом.

Исходное состояние.

При включении источник питания процессора вырабатывает в линии 25.2 сигнал Уст (Сброс), который обнуляет триггер 13 и регистры 14. В этом случае по линиям управления вс.ех блоков 6 пересылается код 00, поэтому работа всех блоков 6 памяти запрещена. Входы-выходы буферов 3 дан ных на- хЬдятся в высокоимпедансном состоянии, так как сигналь с выхода триггера 13 и выходов дешифратора 15,2 пассивны (О).

Начало циклов обмена Ввод и Вывод выполняется одинаковым образом. Процессор на- линиях 25„1 и 25,3 вы- . ставляет адрес и сигнал ВУ, если идет обращение к внешнему устройству. Приемопередатчик 7 находится в режиме передачи данных с магистрали 25 процессора на внутреннюю магистраль 19 устройства, поэтому адрес с магистрали 25 поступает на вход регистра 8 адреса, при этом на старший разрядный вход этого регистра поступает сигнал ВУ. После установления адреса, процессор устанавливает в линии 25,4 сигнал ОБМ, который поступает на синхровход регистра -8 адреса, в результате адрес с магистрали 25,1 Запоминается в регистре 8 на время действия сигнала от процессора ОБМ. Информация о выходе регистра 8 поступает на вход дешифратора 10. Если процессор адресуется к одному из функциональных узлов устройства сопряжения : триггеру 13, к одному из гистров 14, к одному из буферов-3 или к одному из регистров 4, то на выходе дешифратора 10 появляется сигнал, разрешакщий работу дешифратором 11 и 9. Так как с выхода регистра 8 на информационные входы дешифратора 9 поступает код адреса одного из функциональных узлов, то один из выходов этого дешифратора активизируется, разрешая работу одному из функциональных узлов (триггеру 13 или одному из дешифраторов 12, 15, 1, 15.2, 16). На этом адресная часть цикла любого обмена завершается. Цикл вывод.

Б этом цикле процессор после установки на магистрали сигнала ОБМ снимает с магистрали адрес и выставляет данные, предназначенные для вывода на магистраль. Эти данные через приемопередатчик 7 поступают на информационные входы функциональных узлов триггера 13, регистров 14, буферов 3 и гистров 4, После установления данных на линиях 25.1 процессор на линии 25.6 выдает сигнал ДЗП, который для устройства 1 являетс й сигналом Вывод. Этот сигнал поступает на вход дешифратора 11, так как работа этого дешифратора разрешена сигналом от дешифратора 10, то на его выходе появляется сигнал Ответ Кроме того, сигнал Вывод поступает на стробирующий вход триггера 13 и входы разрешения дешифраторов 12, 15.1 и 16. При этом произойдет следующее: если у дешифратора 9 активизирован выход разрешения триггера 13, то запись информации происходит в этот триггер (на его выходе появляется О или 1). Если активизирован один из выходов разрешения дешифраторов 12, 15.1, 16, то строб записи Появляется на одном из выходов-выбранного дешифратора 12, 15.1, 16, пр чем выбор выхода зависит от кода адреса на информационных входах этого . дешифратора, которьй поступает на информационные входы по группе младших разрядов адреса регистра 8. Этот .строб записи заносит информацию от процессора в соответствующий регистр или регистр буфера 3 данных. Процессор, получив сигнал Ответ, снимает сигнал ДЗП, устройство 1 снимает сигнал Ответ, так как сигнал Вывод устройства снят, после чего процессор снимает данные с магистрали и сигнал ОБМ. На этом цикл обмена вывод заканчивается.

Цикл ввод. В этом цикле процессор после установки в активное состояние dигнaлa ОБМ освобождает линии 25.1 адреса данных и вр.ютавляет на линии

0107 :

25.6 сигнал ДЧТ, который для устройства 1 является сигналом Ввод. Хотя в этом цикле может быть адреса- g ция к любому из регистров устройства 1, но считываются действительные данные только в том случае, если идет обращение к одному из буферов 3 данных. Рассмотрим этот случай. На вход

10 разрешения дешифратора 15.2 поступает сигнал от дешифратора 9 адреса функ-. циональных узлов, а на второй вход разрешения - сигнал Ввод, при этом активизируется тот выход дешифрато15 ра 15.2, код адреса которого находится на информационном входе этого дешифратора. Сигналом с активизированного выхода дешифратора 15.2 разрешается передача информации с ма20 гистрали данных блоков 6 памяти через соответствующий буфер 3 данных на вход приемопередатчика 7. В это же время сигнал Ввод.поступает на вход дешифратора 11, работа которо25 го разрешена сигналом с выхода дешифратора 10. Поэтому на выходе дешифратора 11 появляется сигнал Ответ и сигнал считывания приемопередатчика 7. По этому сигналу приемо30 передатчик 7 переключается на передачу информации с информационного входа на информационньй вход-выход устройства 1, поэтому данные с выхода одного из буферов 3 данных (тем

2g самым с части магистрали данных блоков 6 памяти) транслируются на магистраль процессора. Процессор, получив сигнал Ответ от устройства 1, считывает данные и снимает сигнал 40 ДТЧ, а следовательно, и сигнал

Ввод с магистрали. Далее устройство 1 снимает сигнал Ответ, приемопередатчик 7 переключается в исходное состояние, прекращается передача ин45 формации через буфер 3 данных. Процессор снимает сигнал ОБМ и на этом цикл обмена Ввод заканчивается.

В алгоритмах для циклов записи и 50 чтения одного слова блоков 6 памяти (фиг. 4 и 5) приняты обозначения:

X - константа или имя константы; (ЭХ - константа есть абсолютный

адрес; 55 (X) - содержимое ячейки или реги. стра X есть данные; (а)(Х) - содержимое ячейки или регистра X есть абсолютный адрес;

Rj - имя регистра с номером i. Для случая сопряжения устройства 1 с восемью блоками 6, емкостью по 64К 16-разрядных слов каждый узлы имеют адреса:

176000.-176036

.76040g 176042,

8

176044

в

Буферы данных 3 Триггер 13 Регистр 14 управления блоками памяти

Регистр 4 адреса ячеек памяти.

Коды команд управления блоками 6 памяти:

0Невыбор

1Чтение 2Запись

3Невыбор Комментарии к алгоритму.на фиг.4:

1- RO содержит начальный адрес даннь х в памяти процессора; R1 используется при обращении к устройству сопряжения 1; R2 содержит текущий адрес ячейки памяти блока 6 памяти,

2 B Rl занесен адрес нулевого буфера 3 данных,

3- одно слово из памяти процессора (16 бит) занесено в один из буферов 3 данных. Проведен инкремент адресов в регистрах RD и RI, При обмене словами инкремент адреса равен 2.

4- во все буферы данных занесена информация из памяти процессора.

5- выходы регистров буферов 3 данных подключены к магистрали данных блока 6 памяти. В R1 находится адрес регистра 4 адреса ячеек памяти

6- в регистр 4 адреса ячеек памяти занесен текзпций адрес ячейки памяти.

7- подана команда записи на время 50 мс.

8- команда записи снята, триггер 13 обнулен.

9- запись одного слова блока памяти, равного 256 бит, проведена.

Комментарии к алгоритму на фиг.5 5

1- RO содержит начальный а:дрес массива памяти процессора, куда счи тывается информация из блока 6 памяти. Р1 используется при обращении к

.буферам 3 данных. R2 содержит текущи адрес ячейки памяти блока 6 памяти.

2- в регистр 4 адреса ячеек памяти занесен адрес ячейки памяти;

в регистр 14 управления блоком памяти занесена команд чтения; в R1 занесен адрес ртупе.вого буфера 3 данных.

0

5

0

5

0

5

5

0

5

3- в память процессора осущест- влена пересылка части слова из блока

6 памяти (16 бит); адреса памяти процессора и буфер 3 данных инкременти- рованы.

4- команда чтения снята.

5- чтение одного слова блока памяти, равного 256 бит, проведено.

На временных диаграммах циклов записи и считывания одного слова (фиг. 6-и 7) обозначено: Т1,...,Т7, Т9,...5Т12 - циклы обмена Вывод, процессора; Т13,.Т14 - цикл обмена Ввод процессора; Т8 - цикл записи одного слова; Т15 - цикл считывания одного слова; t - время, необходимое для записи одного слова в ячейку памяти блока 6 памяти, Цикл памяти одного слова осуществляется следующим образом.

Циклы Т1,...,Т2 - последовательная запись информации в регистры 17 буферов 3 данных;

Цикл ТЗ - запись информации э триггер 13, т.е. включение сигнала чтения данных из регистров 17, По фронту сигнала Вывод данные заносятся в триггер 13, вследствие этого разрешается считывание из регистров 17 и информационное слово из регистров 17 поступает на магистраль 19 данных.

Циклы T4,,.jT5 - запись информации в р&гкстры 4 адреса, запись в устройство адреса выбранной ячейки блока 6 памяти. По фронту сигналов Вывод адрес поступает на.магистраль адреса блоков 6 памяти.

Цикл Т6 - запись информации в регистр 14, по фронту сигнала Вывод происходит установка команды эаписи на входах управления требуемого блока 6 памяти, С этого момента начитается запись в этот- блок, :

Процессор отсчитывает В1Лемя t, необходимое для записи одного слова в блок 6 памяти, если он вьтолнен на элементах памяти со временем записи большим, чем выполнения цикла обмена Вывод процессора.. Если блок 6 памяти.вьшолнен на ОЗУ, время не отсчитывается;

Цикл Т7 - запись информации В регистр 14 команд управления блоками памяти, по окончании времени t процессор снимает команду записи с

у150

входов управления соответствующего бло ка 5 памяти. Цикл записи одного слова Т8 заканчивается.

В цикле записи одного слова поря- док выполнения циклов обмена процессора Т1,...,Т5 может быть произвольным. Цикл ТЗ выполняется только один раз, перед запись первого слова.

Цикл считывания одного слова осу- ществляется следующим образом.

Циклы Т9,...,Т10 - запись информации в регистры А адреса, запись в устройство адреса выбранной ячейки памяти;

Цикл Т11 - запись информации в триггер 13 снимается сигнал разрешения чтения данных из регистров 17, выходы регистров 7 переводятся в третье состояние. Цикл Т11 выполня- ется только в том случае, если перед считыванием осуществлялись си в блок 6 памяти;

Цикл Т12 - запись информации в ре гистр 14 команд управления блоками памяти, по фронту сигнала Вывод на входах управления требуемого блок 6 памяти устанавливается команда чтение, после установки этой команды через время выборки, определяемое типо микросхем памяти блока 6 памяти, на магистрали данных блоков 6 памяти появляются считываемые данные, кото- рые поступают на входы передатчика, данных буферов 3 данных;

Циклы Т13,...,Т1А - последовательное считывание информационного слова с магистрали данных блоков 6 памяти через передатчики 18 данных буферов 3 данных,

В дальнейшем выборка очередного слова осуществляется процессором записью в устройство соответствующего адреса ячеек памяти, если считывание осуществляется из одного блока 6 па- мяти. Если считывание осуществляется из разных блоков 6 памяти, то после окончания очередного цикла считывания слова, процессор должен снимать команду чт.ения с управляющих входов блока 6 памяти, а после записи в устройство нового адреса ячейки памяти нового блока 6 памяти устанавливать команду чтения на входах управления этого блока 6 памяти.

При вьшолнении цикла считывания одного слова. Т15 порядок выполнения циклов обмена процессора Т9,,...,Т12,

10

а также циклов Т13,.,.,Т14 может быть произвольным,

Формула изобретения

Устройство для сопряжения процессора с группой блоков памяти, содержащее канальный приемопередатчик, регистр адреса, дешифратор адреса устройства и дешифратор управляющих сигналов, причем вход-выход канального приемопередатчика является входом-выходом устройства для подключения к адресно-информационной шине процессора, а вход считывания - соединен с первым выходом дешифратора управляющих сигналов, первый и второй входы которого являнЬтС-я соответствующими входами устройства для соединения с выходами сигналов Ввод и Вывод процессора, а третий вход подключен к выходу дешифратора адрес устройства, группой входов соединенного с группой выходов регистра адреса, вход которого соединен с выходом канального приемопередатчика, синхровход является входом устройства для подключения к синхронизирующим выходам процессора, отличающееся тем, что, с целью расширения класса решаемых задач за сче обеспечения режимов работы с блоками памяти различных типов, в него введены группа регистров команд управления блоками памяти, триггер, группа буферных регистров данных, дешифратор функциональных узлов, дешифратор команд управления блоками памяти, дешифратор адреса ячеек памяти, группа регистров ячеек памяти и два дешифратора данных, причем информационные входы регистров команд управления блоками памяти группы соединены с первыми информационными входами-выходами буферных регистров данных группы, информационными входами регистров адреса ячеек памяти группы, информационным входом триггера и выходом и информационным входом канального приемопередатчика, группа выходов регистра адреса устройства соединена с группами информационных входов дешифратора команд управления блоками памяти, дешифратора адреса ячеек памяти, первого, второго дешифраторов данных и дешиф- pa-iupa функциональных узлов, входом

разрешения подключенного к выходу дешифратора адреса устройства, а первым - четвертым выходами соединенного соответственно; с входом разрешения записи триггера, первым входом разрешения дешифратора команд управления блоками памяти, первыми входами разрешения первого и второго дешифраторов данных и первым входом разрешения дешифратора адреса ячеек памятиJ группа выходов которого соединена с синхровходами регистров ячеек памяти Группы, выходы которых образуют группу выходов устройства для подключения к магистрали адреса бло- ков памяти группы, выходы регистров команд управления блоками памяти образуют группу выходов устройства для подключения к магистрали управления блоков памяти группы, а синхровходы соединены.с группой выходов дешифратра команд управления блоками памяти, второй вход разрешения которого соединен с входом устройства для подклю- 25сигналов являются соответственно

чения к выходу сигнала Вывод про-входом и выходом устройства для подцессора и соединен с сирхровходомключения выхода выработки и сии триггера и вторыми входами разреше-хронизирующего входа процессо Кия дешифратора адреса ячеек памятира.

0107112

и первого дешифратора данных, группа ВЫХОДОВ которого соединена с входами записи буферных регистров данных

g группы, вторые информационные входы- выходы которых образуют группу входов- выходов устройства для подключения к магистрали данных блоков памяти группы, а входы разрешения передачи сое10 динены с группой выходов второго дешифратора данных, второй разрешаюш;ий вход которого соединен с входом устройства для подключения к выходу сигнала Ввод процессора, входы разре15 шения чтения буферных регистров данных соединены с выходом триггера, вход сброса которого соединен с входами сброса регистров команд управления блоками памяти и является вхо20 дом устройства для подключения к выходу сигнала Сброс процессора, вход старшего информационного разряда регистра адреса устройства и второй выход дешифратора управляющих

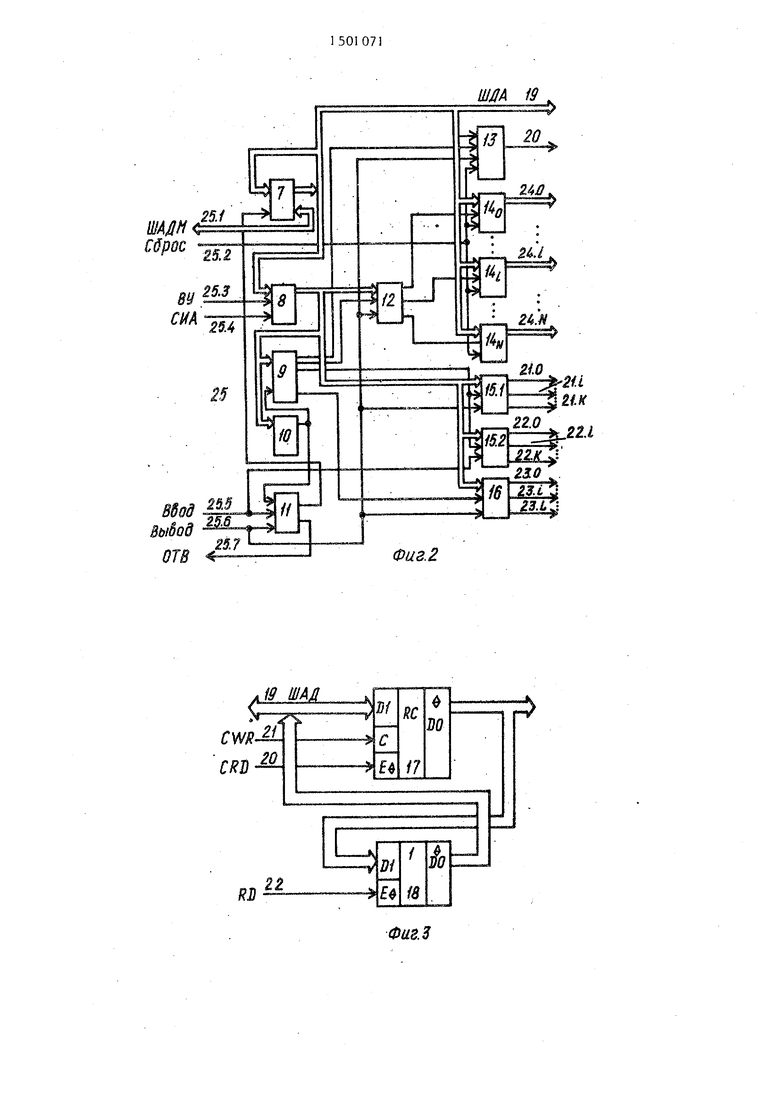

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для обмена информацией с общей шиной | 1984 |

|

SU1322301A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

Изобретение относится к вычислительной технике, предназначено для использования в составе микроЭВМ в качестве внешнего запоминающего устройства, в котором в качестве блоков памяти могут использоваться накопители различных типов: ОЗУ, ПЗУ, ППЗУ, РПЗУ, и наиболее широкое применение может найти в качестве энергонезависимого запоминающего устройства с возможностью многократной смены информации при использовании в блоках памяти ППЗУ и РПЗУ. Ция расширение класса решаемых задач за счет обеспечения режимов работы с блоками памяти различных типов. Это достигается тем, что в устройство, содержащее канальный приемопередатчик, регистр адреса устройства, дешифратор адреса устройства и дешифратор управляющих сигналов, введены дешифраторы функциональных узлов, команд управления блоками памяти и адреса ячеек памяти, два дешифратора буферных регистров данных, триггер, группа регистров команд управления блоками памяти, группа регистров адреса ячеек памяти и группа буферных регистров данных. Устройство осуществляет при помощи буферных регистров данных согласование форматов данных, при помощи регистров адреса ячеек памяти - согласование форматов адреса процессора и группы блоков памяти. Наличие триггера позволяет осуществить запись данных в группу ППЗУ, имеющих время записи по одному адресу больше, чем время цикла вывода процессора. Наличие двух дешифраторов буферных данных и дешифратор адреса ячеек памяти позволяет уменьшить адресное пространство, которое занимает группа блоков памяти в адресном пространстве процессора. 5 ил.,2 табл.

Т а б л и ц а 1

Код

Назначение команды

У1 УО

О Невыбор блока памяти (запрет блока памяти)

1 Чтение информации из блока памяти

О Запись информации в блок .памяти

. 1 Стирание информации - для блоков памяти на

основе ППЗУ с элек- - трическим стиранием и записью информации Запрет блока памяти - для блоков памяти на

основе ППЗУ с электрической записью и ультрафиолетовым стиранием информации

25 4

«о

5

Физ.2

Сношо

(i76042MO Запустить тайнер на 6peMfl 50 НС

@i176Q40)-0

С конец

Зо Зк

Фиг4

СЙшло )

/7Ш4: /у 2;

(Ri)-176000

@(РО)-ф(Р1) (RO)-iRQ)Z (Ri)-(

-р

Cs

{j(OHeu, Фиг. 5

ЙW5a. Ъ «ii S.f

| ,Авторское свидетельство СССР № 951315, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-05-25—Подача