11

Изобретение относится к вычислительной технике и может быть использовано при создании мнкроЭВК.

Цель изобретения - снижение аппаратных затрат.

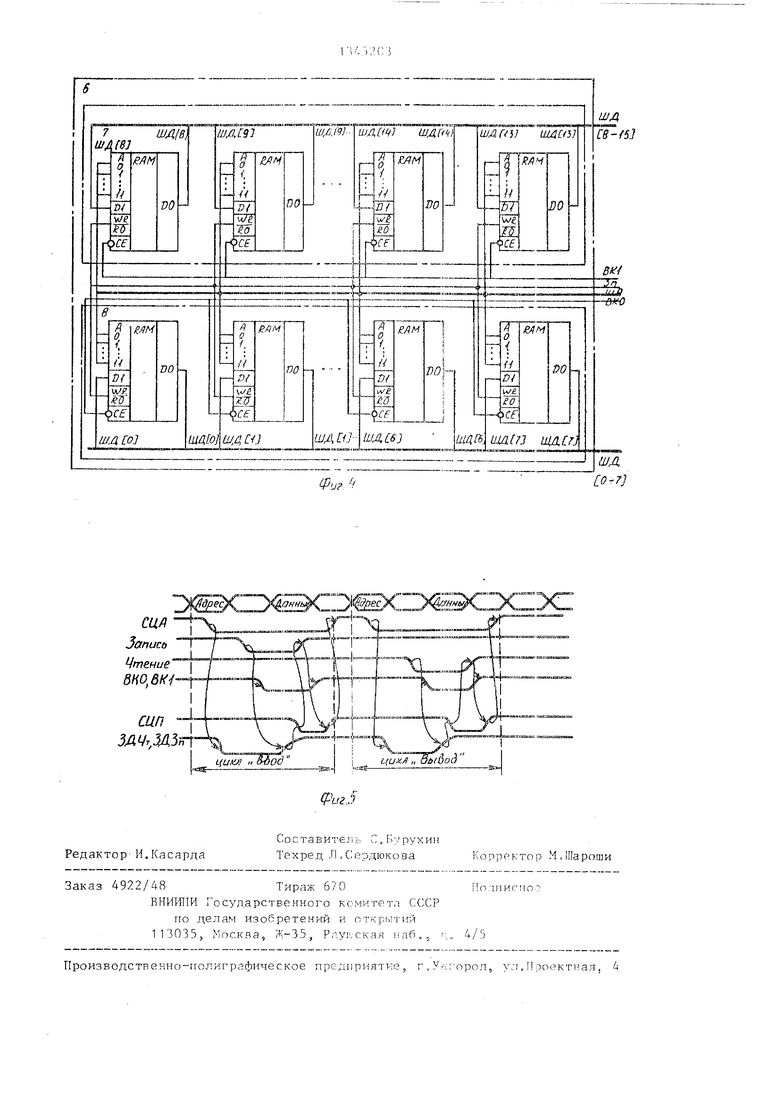

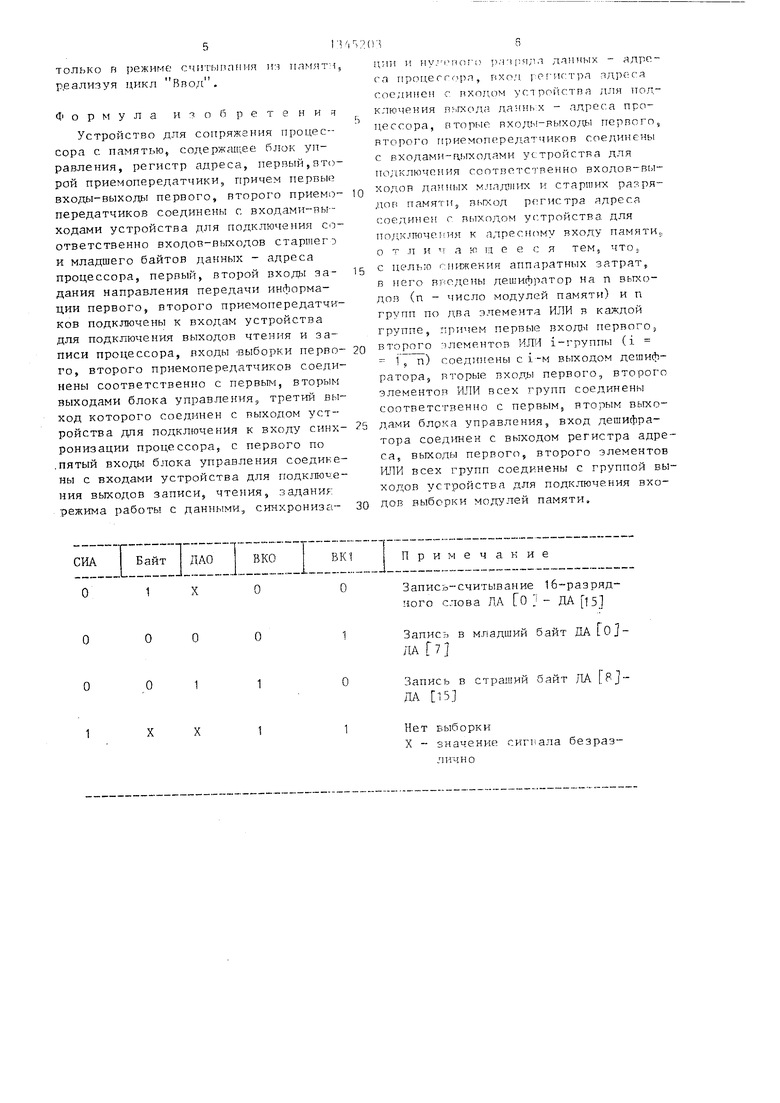

На фиг, 1 приведена структурная с:хема устройства, подсоединепиого, например, к магистрали Общая микроэвм Электроника-60,, совместно с п модулями оперативной памяти; на фиг, 2 - структурная схема одного кз вариантов реализации блока управления (на основе ИМС КР588ВГ2);, на фиг, 3 - структурная схема одного з вариантов реализации магистрального приемопередатчика (на основе ИМС КР588ВА1), на фиг, 4 - функциональная схема одного из вариантов модуля оперативной памяти емкостью КхТб (на основе ИМС КР537РУ2А)5 на фиг, 5 - временная диаграмма работы устройства

Устройство для сопряжения процессора с памятью содержит (фиг,, 1) блок 1 управленияS дешифратор 2, первьш,

второй приемопередатчики 3-1,. 3-2,

t

регистр 4 адреса, 2п элементов ИЛИ 5

п модулей 6 оперативкой памяти, в состав каждого из которых входят блоки хранения старших 7 и млa зfIИX 8 байтов,

Блок 1 управления предназначен для управления работой устройства ством формирования сигналов выборки блока хранения младш1 гх или старших байтов в модуле памяти, соответственно ВКО и ВК1, а также сигнала синхронизации пассивного устройства (СИП) на основе управляющей информации, поступающей от процессора,

Дещифратор 2 служит для определ(- ния модуля памяти, к которому производится обращение, и управления передачей в него сигналов выборки ВКО и БК1 от блока 1 , Данный блок предст,1В- ляет собой дешифратор с инверсными выходами по количе ству подключаемых модулей памяти.

Двунаправленные приемопередатчики 3-1, 3-2 предназначены для передачи информации посредством гаины данных (ШД) , либо из магистрали в , либо в обратном направлениио 1 егисгр 4 адреса предназначен для запоминания коДа адреса, по которому произзо- дится обращение к памяти, и установки его посредством шины адреса (ША) на адресных моду- 1йй памяти. Элементы ИЛИ 5 служат для передачи уп0

52

5

О

5 0

5

g

m2

р, 1вляю1 и1 : сиг и я icif и BKI от б.пока 1 то. плсо п тпт Mojvyjib n,TMHTMj к которому П)011чпод ггся обрлщг-Р.ие. Модули 6 памяти иредна- начены для хранения кодов. Б:гоки хранг:1 ия старипта 7 и младших 8 байтов слу;кат для хранения, соответстпеино, 8-15 и 0-7 разрядов, записанн1,1х в модуль 6 памяти 16-разрядных слов,

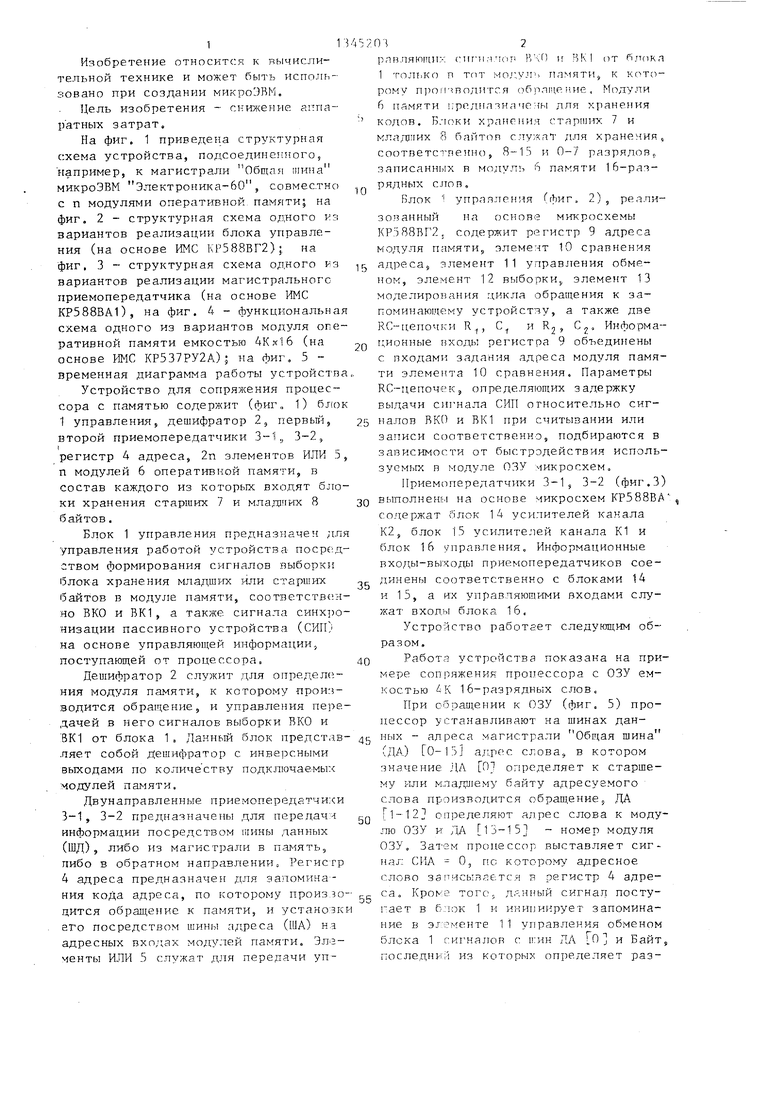

Влок упраяттения (фиг. 2), реали- зо занный на основе микросхемы КР588ВГ2; содержит регистр 9 адреса модуля памяти, элемент 10 сравнения адреса, элемент 11 управления обменом, элемент 12 выборки, элемент 13 моделиро1 ания цикла обращения к за- поминаю1.дему устройству, а также две RC-цепочки R, С и Rj, С, Информа- г;ион}1ые входы регистра 9 об1-,единены с входами задания адреса модуля памяти элемента 10 сравнения. Параметры RC-цепочек, определяющих задержку выдачи сигнала СИП относительно сигналов ВКО и ВК1 при считывании или записи соответственно, подбираются в зависимости от быстродействия используемых в модуле ОЗУ микросхем.

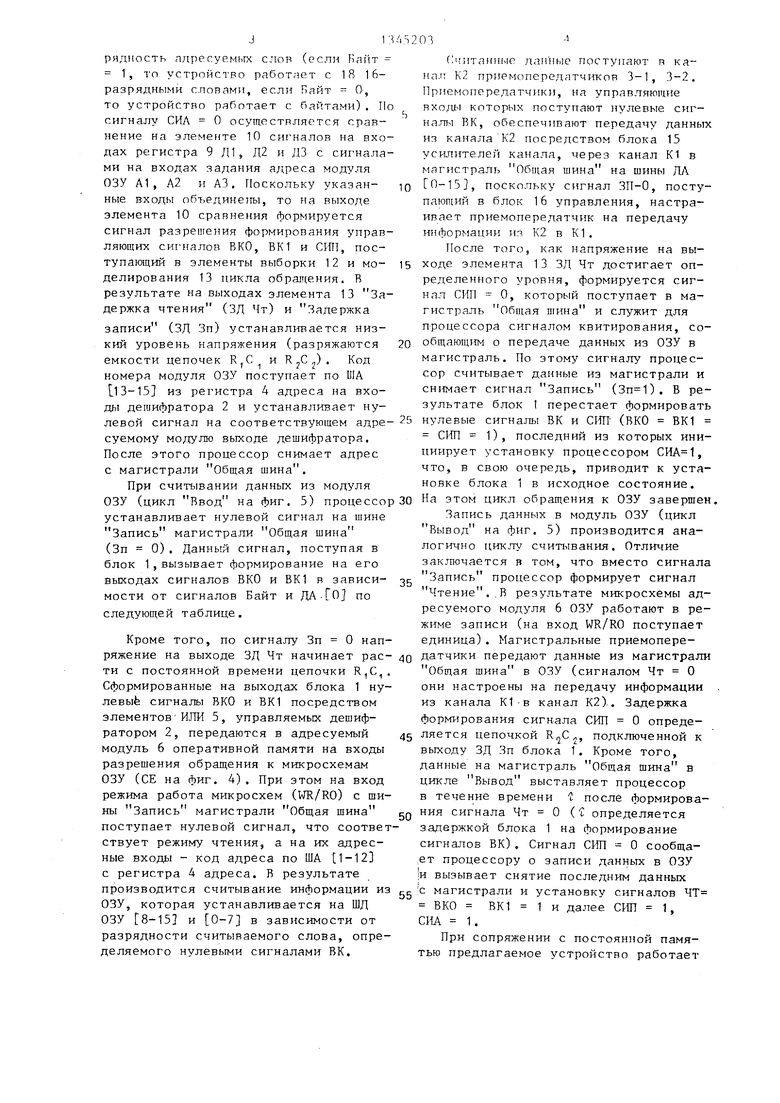

Приемопередатчики 3-1, 3-2 (фиг,3) выполнены на основе микросхем КР588ВА , содержат блок 14 усилителей канала К2, блок 15 усилителей канала К1 и блок 16 управления. Информационные входы-выходы приемопередатчиков соединены соответственно с блоками 14 и 15, а и х управляющими входами служат входы блока 16.

Устройство работает следуюп);им образом.

Работа устройства показана на примере Сопряжения процессора с ОЗУ емкостью К 16-разрядных слов.

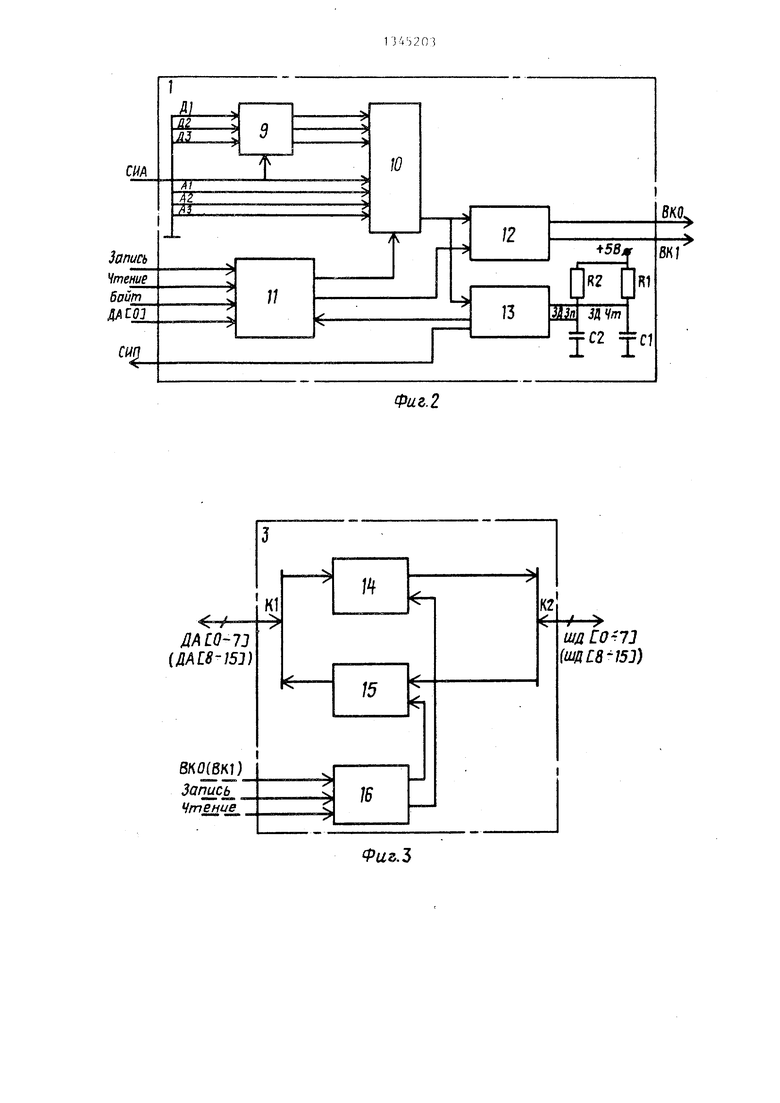

При обраи1ении к ОЗУ (фиг, 5) процессор устанавливают на шинах данных - адреса магистрали Общая шина (ДА.) 0-15 адрес , в котором значение ДА 01 определяет к старшему или младшему байту адресуемого слова производится обращение, ДА 1-12 определяют адрес слова к модулю ОЗУ и ДА 13-15 - номер модуля ОЗУ, Затем процессор выставляет сигнал СИА О, по которому адресное слово за тисывается в регистр 4 адреса. Кроме ТОГО; д,яняый сигнал поступает в 6:ioK 1 и ини1 иирует запоминание в эх ементе 1 1 управления обменом блока 1 сигналог с кии ДА П и Байт, последний из которых определяет раз

JГЗ

рядность лдресуемых слов (если RniiT 1, то устройство работает с 18 16- разрядными словами, если Байт О, то устройство работает с байтами). По сигналу СИЛ О осуществляется сравнение на элемер{те 10 сиг налов на входах регистра 9 Д1, Д2 и ДЗ с сигналами на входах задания адреса модуля ОЗУ А1 , Л2 и A3, Поскольку указан- ные входы объединены, то на выходе элемента 10 сравнения формируется сигнал разрешения формирования управляющих сигналов ВКО, ВК1 и СРШ, поступающий в элементы выборки 12 и мо- делирования 13 цикла обршдения. В результате на выходах элемента 13 Задержка чтения (ЗД Чт) и Задержка

записи (ЗД Зп) устанавливается низкий уровень напряжения (разряжаются емкости цепочек R,C и . Код номера модуля ОЗУ поступает по ША 13-15 из регистра 4 адреса на входы дешифратора 2 и устанавливает нулевой сигнал на соответствующем адре- суемому модулю выходе дешифратора. После этого процессор снимает адрес с магистрали Общая шина.

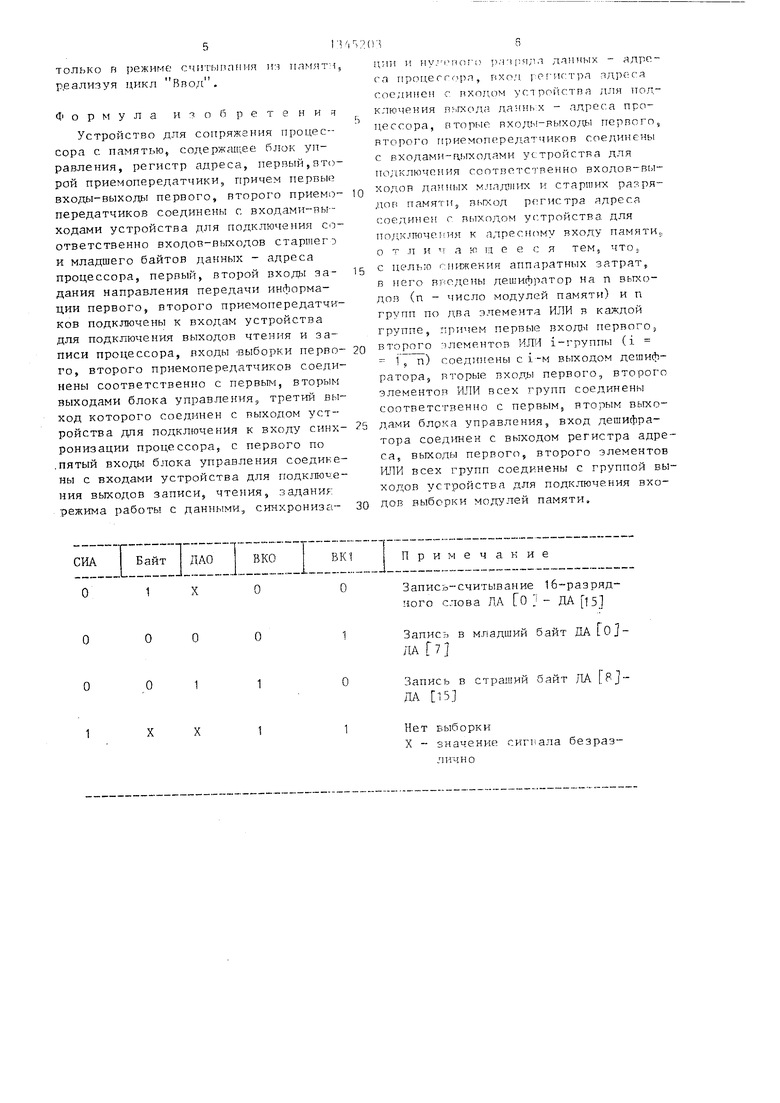

При считывании данных из модуля ОЗУ (цикл Ввод на фиг. 5) процессо устанавливает нулевой сигнал на шине Запись магистрали Общая шина (Зп 0). Данный сигнал, поступая в блок 1 , вызывает формирование на его выходах сигналов ВКО и ВК1 в завися- мости от сигналов Байт и ДА-ГО по следующей таблице.

Кроме того, по сигналу Зп О напряжение на выходе ЗД Чт начинает рас- ти с постоянной времени цепочки Сформированные на выходах блока 1 нулевые сигналы ВКО и ВК1 посредством элементов ИЛИ 5, управляемых дешифратором 2, передаются в адресуемый модуль 6 оперативной памяти на входы разрешения обращения к микросхемам ОЗУ (СЕ на фиг. 4). При этом на вход режима работа микросхем (WR/RO) с шины Запись магистрали Общая шина поступает нулевой сигнал, что соответствует режиму чтения, а на их адресные входы - код адреса по ША 1-12 с регистра 4 адреса. Б результате производится считывание информации из ОЗУ, которая устанавливается на ШД ОЗУ 8-153 и 0-7 в зависимости от разрядности считываемого слова, определяемого нулевьпчи сигналами ВК,

2

5

0 5

0 5

0 5 g g

03 I

c:i HTaHni.ie данные поступают в канал К2 приемопередатчиков 3-1, 3-2. Приемопередатчики, на управляющие входы которых поступают нулевые сигналы ВК, обеспечивают передачу данных из канала К2 посредством блока 15 усилителей канала, через канал К1 в aгиcтpaль Общая шина на шины ДА ГО-15, поскольку сигнал ЗП-0, поступающий в блок 16 управления, настраивает приемопередатчик на передачу информации из К2 в К1.

После того, как напряжение на выходе элемента 13 ЗД Чт достигает определенного уровня, формируется сигнал СИП О, который поступает в магистраль Общая шина и служит для процессора сигналом квитирования, сообщающим о передаче данных из ОЗУ в магистраль. По этому сигналу процессор считывает данные из магистрали и снимает сигнал Запись (), В результате блок 1 перестает формировать нулевые сигналы ВК и СШ (ВКО ВК1 СИП 1), последний из которых инициирует установку процессором , что, в свою очередь, приводит к установке блока 1 в исходное состояние. На этом цикл обращения к ОЗУ завершен.

Запись данных в модуль ОЗУ (цикл Вывод на фиг. 5) производится аналогично циклу считывания. Отличие заключается в том, что вместо сигнала Запись процессор формирует сигнал Чтение.,В результате микросхемы адресуемого модуля 6 ОЗУ работают в режиме записи (на вход WR/RO поступает единица). Магистральные приемопередатчики передают данные из магистрали Общая шина в ОЗУ (сигналом Чт О они настроены на передачу информации из канала К1-в канал К2).. Задержка формирования сигнала СИП О определяется цепочкой , подключенной к выходу ЗД Зп блока 1. Кроме того, данные на магистраль Общая шина в цикле Вывод выставляет процессор в течение времени 1 после формирования сигнала Чт О (1 определяется задержкой блока 1 на формирование сигналов ВК). Сигнал СИП О сообща- ,ет процессору о записи данных в ОЗУ ;И вызывает снятие последним данных с магистрали и установку сигналов ЧТ ВКО ВК1 1 и далее СШ 1, СНА 1.

При сопряжении с постоянной памятью предлагаемое устройство работает

только в режиме считыпап1-1я из памяти р.еализуя цикл Вво/i,

«Ji о р м у л а изобретения

Устройство для сопряжения процессора с памятью, содержгицее блок управления, регистр адреса, первый,второй приемопередатчики, причем первые входы-выходы первого, второго приемо- передатчиков соединены с входами-вы-- ходами устройства для подключения соответственно входов-выходов старшего и младшего байтов данных - адреса процессора, первый, второй входы за- Дания направления передачи информации первого, второго приемопередатчиков подключены к входам устройства для подключения выходов чтения и записи процессора, входы озыборки перво- го, второго приемопередатчиков соединены соответственно с первым, вторым выходами блока управления, третий выход которого соединен с выходом устройства для подключения к входу синх- ронизации процессора, с первого по .пятый ВХОД111 блока управления соединены с входами устройства для подключения выходов записи, чтения, задания: режима работы с данными, синхрониза-

ции и иу. ч гки о р,чч :я;1л данных - адре- га Г1роцегг(-;,рп, пхо.ч. ppr-nfirpa адргк-а соединен с нходом устройстпа для подключения выхода - адреса процессора, вторые входы-выхо; Ь1 первого, второго приемопередатчиков соединены с входами-г ыходами устройства для подключения соответственно входов-вгл- ходов мла.д)1их н старших разрядов памяти, вькод регистра адреса соединен с выходом устройства для по/зключения к адресному входу памяти,, о т л и м л ю 1ц е е с я TeMj что,, с целые снр-шения аппаратных затрат, в него влсдены дешифратор на п выходов (п - число модулей памяти) и п групп по два элемента ИЛИ в каждой группе, причем первые Bxoniii первого; второго г лементов ИЛИ i-группы (i 1, п) соединены с i-м выходом дешифратора, вторые вход,ы первого, второго элементоп ИЛИ всех групп соединены соответственно с первым, вторым выходами блока управления, вход дешифратора соед1шен с выходом регистра адреса, выходы первого, второго элементов ИЛИ всех групп соединены с группой выходов устройства для подключения входов выборки модулей памяти.

X - значение безразлично

Фаг,.2

Фиъ.Ъ

сип

ДД гЛДЗйРедактор И.Касарда

С о с т а в и т е л ь С . i у р у х и и Техред .П , С е р д ю к о в а

Заказ 4922/48Тираж 670

ВНИИПИ Государственного комитета СССР

по делам изобретена и открытий 113035, Москва, Ж-35., Рл.у1:.ская иаб.„ г.„ 4/5

Производствекно-полиграфическое предприятие, г.Удг орол, y. iЛЬэоектная. 4

К о р р р к т о р М . lila рош и

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С ПАМЯТЬЮ | 1991 |

|

RU2018941C1 |

| Управляющая вычислительная система | 1986 |

|

SU1451711A1 |

| Устройство для обмена информацией между персональной ЭВМ и управляющим вычислительным комплексом | 1991 |

|

SU1838819A3 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании микроЭВМ. Целью изобретения является снижение аппаратных затрат. Устройство содержит блок 1 управления, дешифратор 2, первьй, второй приемопередатчики 3-1, 3-2, регистр 4 адреса, п групп по два элемента ИЛИ 5, Устройство обеспечивает сопряжение процессора с памятью, состоящей из п модулей, используя один блок управления, один регистр адреса и два магистральных приемопередатчика, в то время как в базовом устройстве применяются п блоков управления, п регистров адреса и 2п приемопередатчиков. 5 ил., 1 табл. с S (Л 00 4 СП ND О СО

| Устройство для сопряжения основной памяти с процессором | 1977 |

|

SU736105A1 |

| Устройство для связи процессора с оперативной памятью | 1978 |

|

SU750489A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коннов Е.В., Тихомиров С.Н., Черняховский Д.Н., Шиллер В.А, Модуль ОЗУ с унифицированным интерфейсом на основе БИС серии КР 588 | |||

| - Электронная промьшленность, 1983, вып | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1987-10-15—Публикация

1986-04-21—Подача