10

. 1359782

Изобретение относится к вычислительной технике и предназначено для использования в качестве модуля однородной вычислительной структуры, ориентированной на цифровую обработку сигналов.

Цель изобретения - повышение быстродействия .

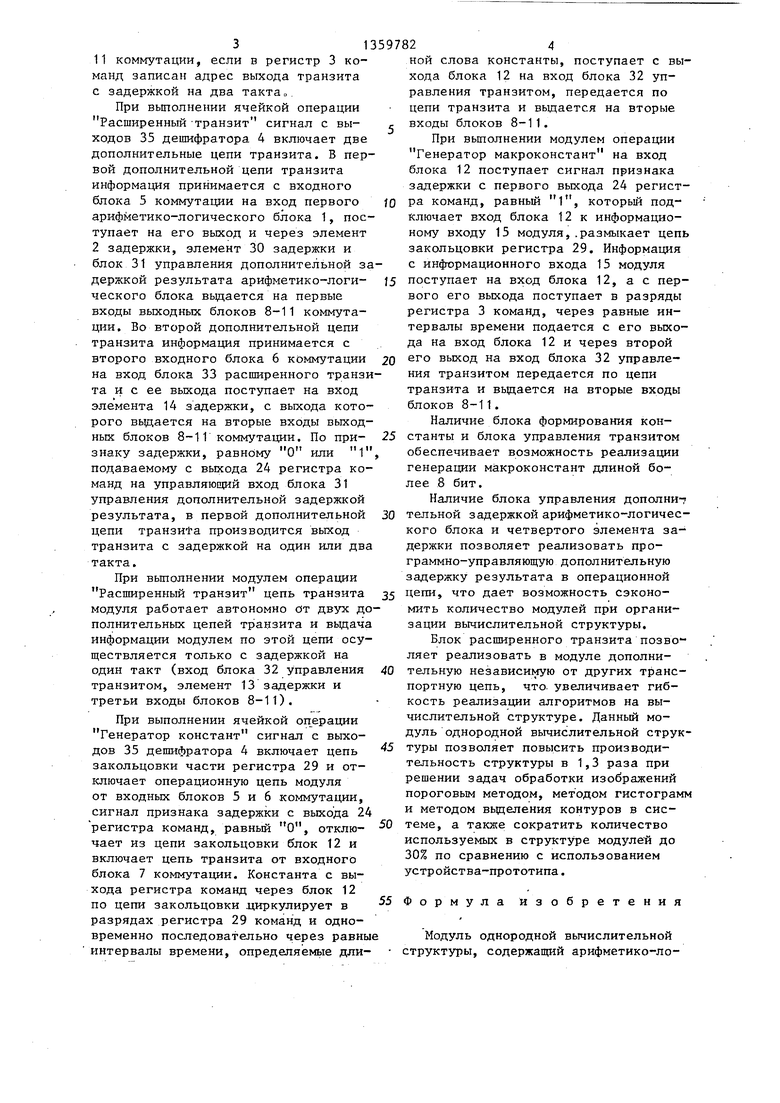

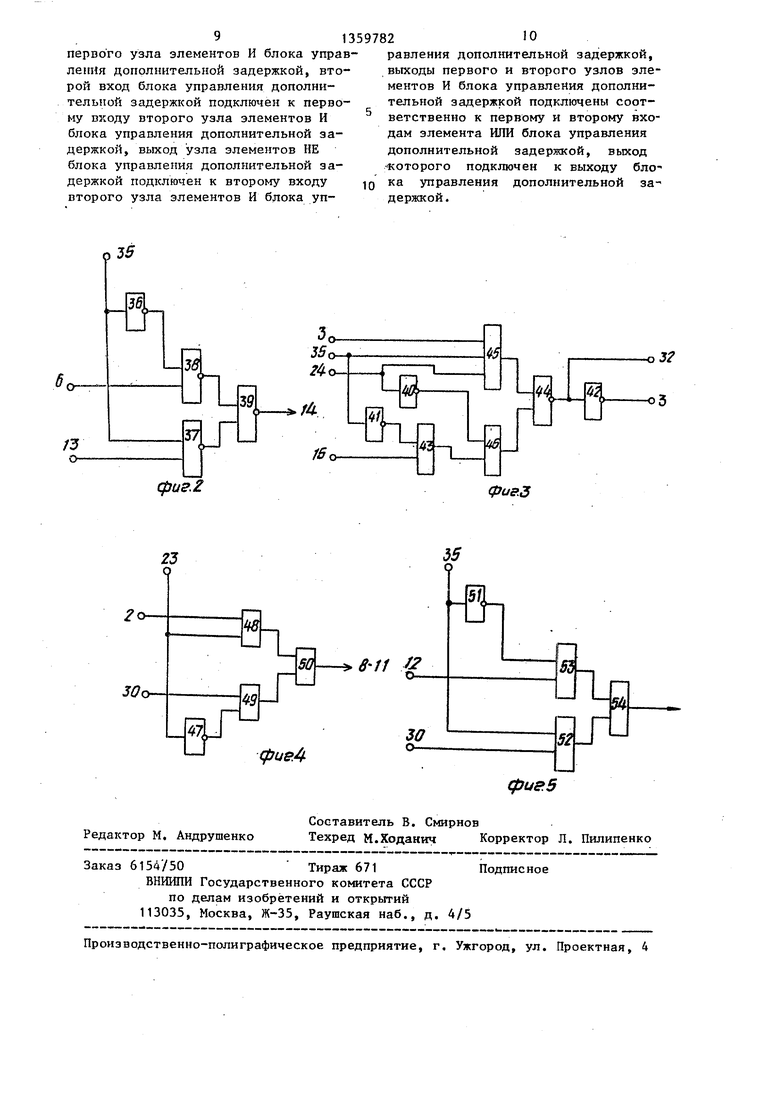

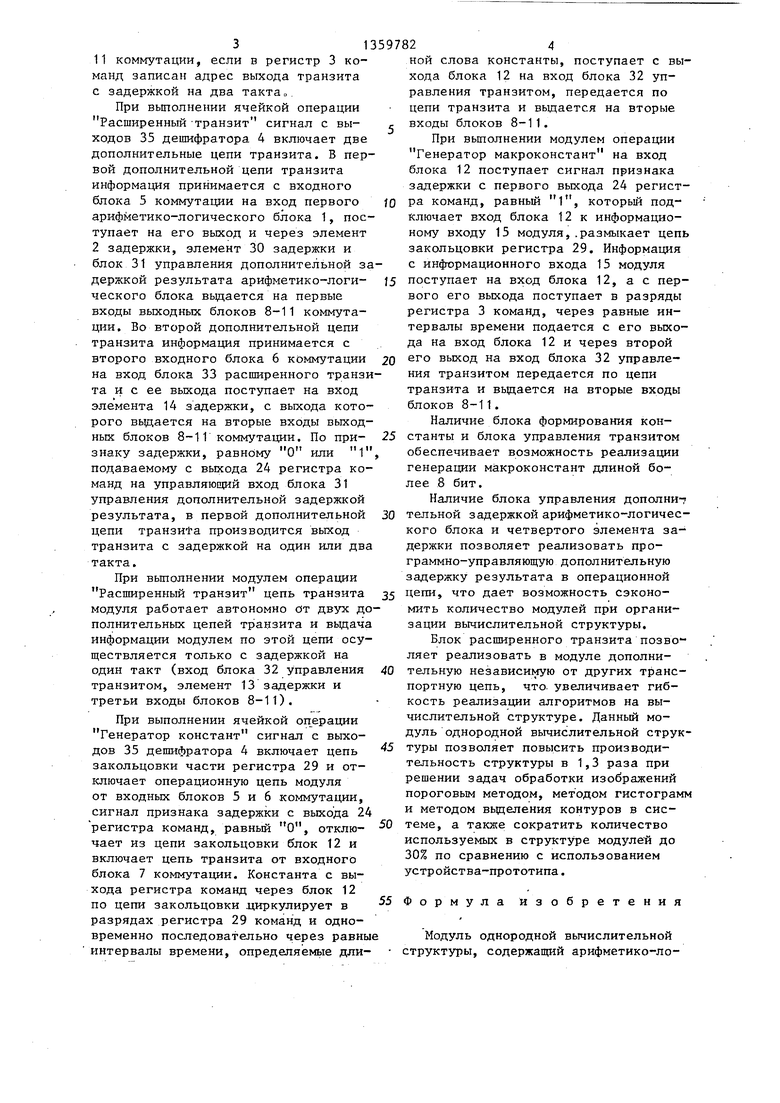

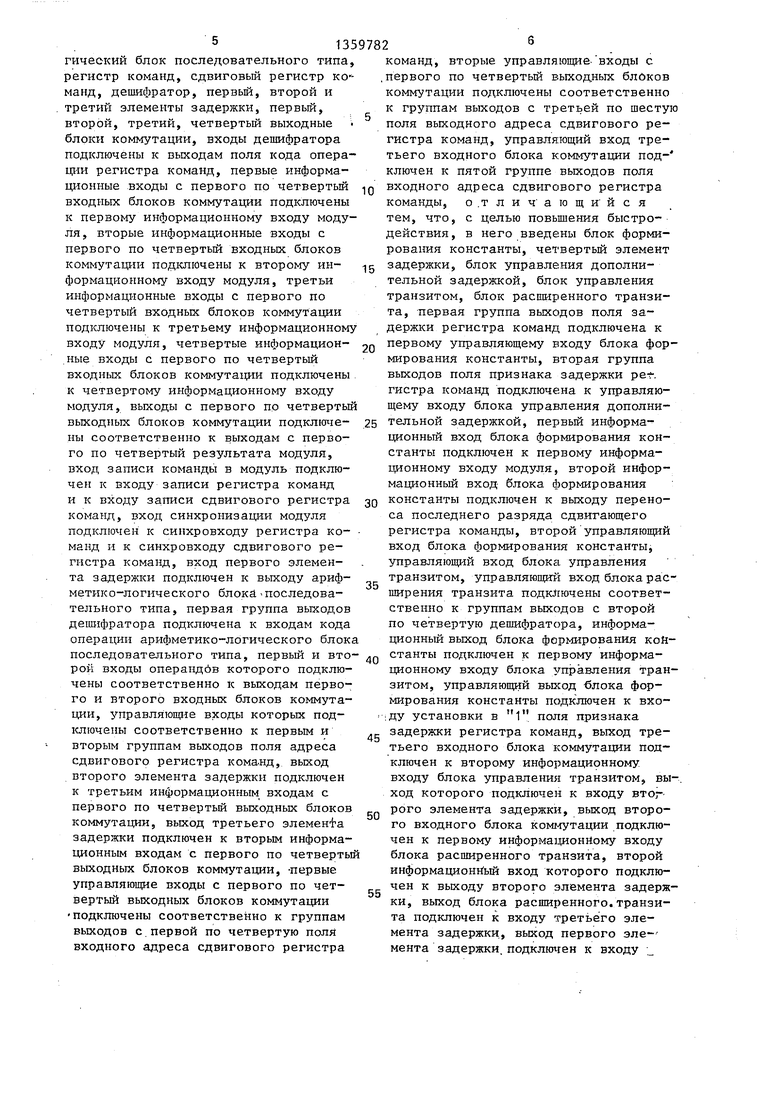

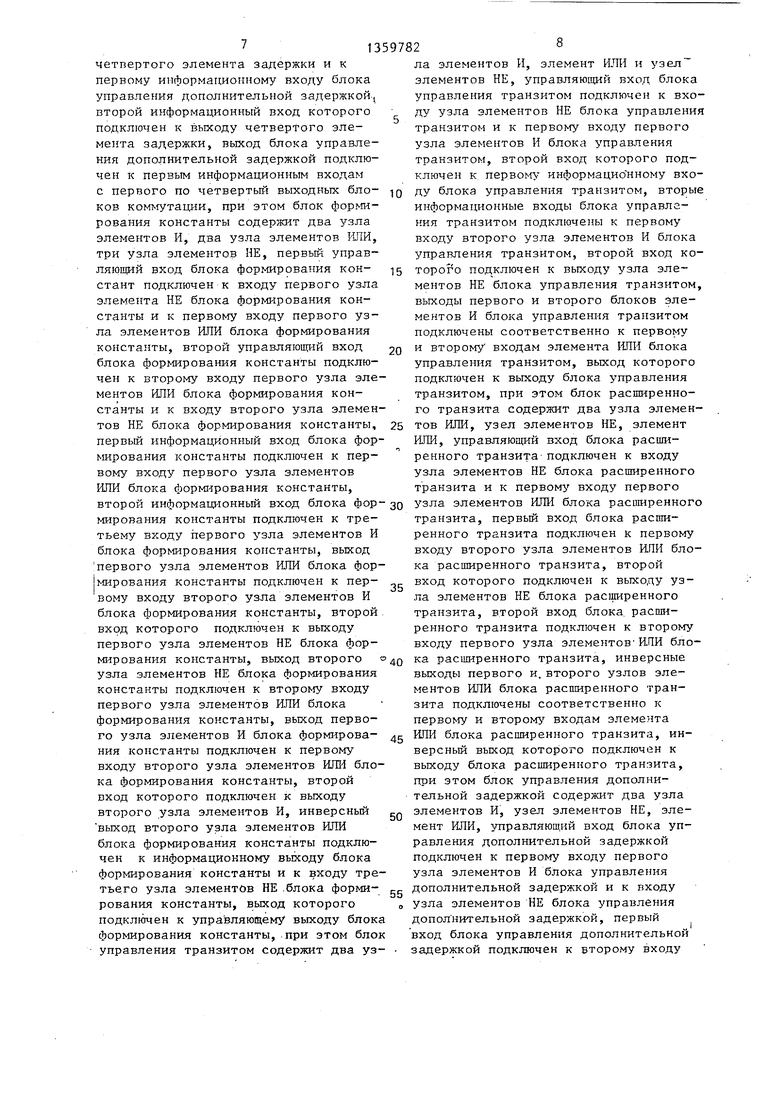

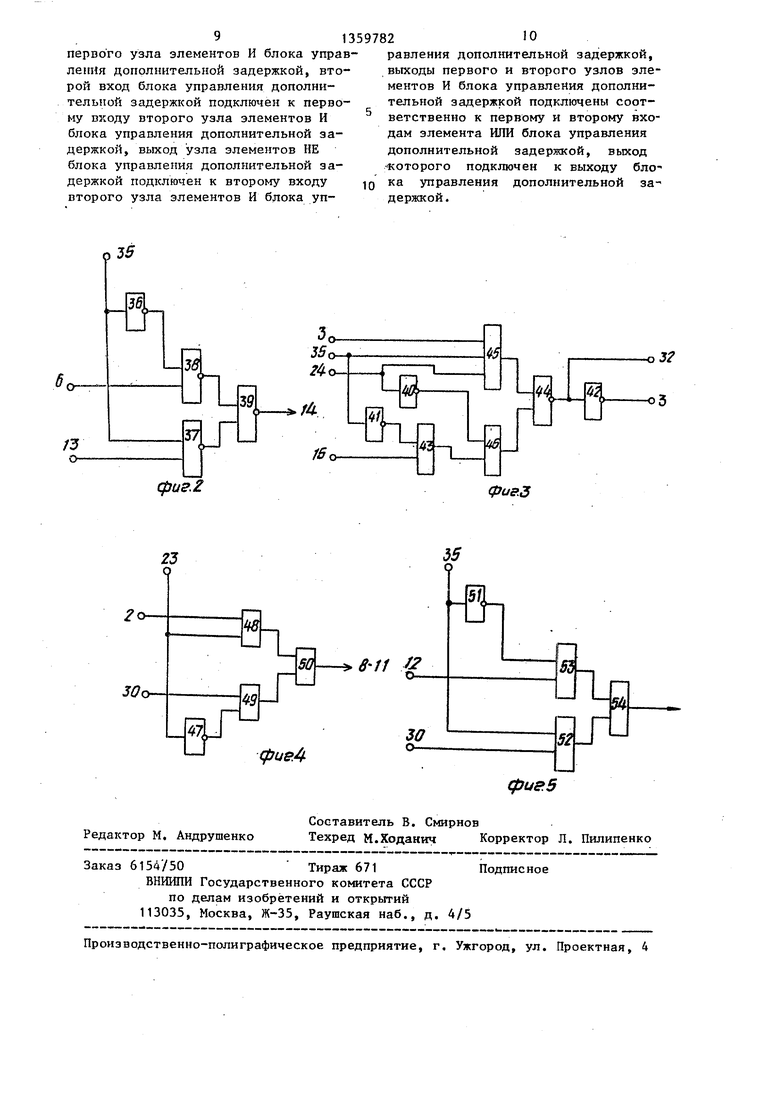

Па фиг.1 представлена блок-схема модуля однородной вычислительной- структуры; на фиг.2 - схема блока расш-фенпого транзита; на фиг.З - блок формирования константы; на фиг.4 - схема блока управления допол--)5 нительной задержкой; на фиг,5 - схема блока управления транзитом.

Модуль однородной вычислительной структуры содерлшт арифметико-логический блок 1 последовательного типа,20 мы, равный О, и модуль переходит, шервый элемент 2 задержки, регистр 3 в режим выполнения операций. ДешифУстройство работает следующим оо- разом.

Перед началом решения задачи производится запись команды в регистры 3 и 29. Код ;соманды состоит из кода операции, признака задержки адресов входов первого и второго чисел ариф- метико-логичес.кого элемента, адреса входа транзита, адреса выхода арифметико-логического блока и адресов выходов транзита с задержкой на одий такт и два такта. Код команды вводится через вход 27 модуля.

После окончания с1-1гнала, разрешающего ввод nporpaMNbi, код команды запоминается в регистре 3 команд, после чего на вход 28 ячейки подается сигнал управления вводом програм- ..-. t t ,

, дешифратор 4, первый, второй третий 1зходные блоки 5,6 и 7 комьтута ции, первый - четвертый 8-1 1 выход- ные блоки коммутации, блок 12 форми- ровапия константы, второй элемент 13 задержки, третий элемент 14 задержки первый-четвертьм 15-18 информационные входы, первый-четвертый выходы 19-22 результата, поле 23 кода ко- манд регистра 3, поле 24 признака задержки регистра 3, поле 25 адреса входного блока коммутации, поле 26 адреса выходного блока коммутации, вход 27 записи команды, вход 28 син- хропизацпи, сдвиговый регистр 29 команд, четвертьш элемент 30 задержки, блок 31 управления дополнительной задержкой, блок 32 управления транзи- ;том, блок 33 расширенного транзита, выходы 34 и 35 кода команды и кода константы соответственно дешифратора 4, при этом блок 33 расширенного транзггга содержит узел 36 элементов НЕ, первый и второй узлы 37 и 38. элементов 1ПИ, элемент РШИ 39; блок 12 формирования константы содержит первый узел 40 элементов НЕ, второй и третий узлы 41 и 42 элементов НЕ, первый и второй узлы 43 и 44 элемен- тов I-fflH, первый и второй узлы 45 и 46 элементов И; блок 31 управления дополнительной задержкой содер- iT узел 47 элементов НЕ, первый и второй узлы 48 и 49 : лементов И, элемент КПП 50; блок 32 управления транзитом содержит узел 51 элементов НЕ, первый и второй узлы 52 и 53 элементов И, элемент ИЛИ 54.

мы, равный О, и модуль переходит, в режим выполнения операций. ДешифУстройство работает следующим оо- разом.

Перед началом решения задачи производится запись команды в регистры 3 и 29. Код ;соманды состоит из кода операции, признака задержки адресов входов первого и второго чисел ариф- метико-логичес.кого элемента, адреса входа транзита, адреса выхода арифметико-логического блока и адресов выходов транзита с задержкой на одий такт и два такта. Код команды вводится через вход 27 модуля.

После окончания с1-1гнала, разрешающего ввод nporpaMNbi, код команды запоминается в регистре 3 команд, после чего на вход 28 ячейки подается сигнал управления вводом програм- ..-. t t ,

5 0 5 g 5

5

0

ратор 4 настраивает ячейку на выпол- нениё операций согласно записанно1-гу в регистр 3 команд коду операций.

. На выход 24 регистра команд выводится занесенный в реггистр 3 команд признак задержки в виде О или 1, В случае 1 на выходе 24 регистра команд блока 31 управления дополни-, тельной задержкой результата арифметико-логического блока включается в операционную цепь элемент 30 задержки. При наличии О на выходе 24 регистра команд информация с выхода элемента 2 заде1эжки поступает На вход блока 31 управления дополнительной задержкой результата арифметико-логического блока и далее на первые ВХОДЫ- выходные блоков 8-11 коммутации.

Выходы 25 и 26 регистра команд осуществляют выбор направления приема и выдает информации ячейкой по операционной цепи и цепи транзита. В зависимости от кода операции, записанного в регистр 3 команд, цепь транзита может работать автономно от операционной сети, осуществляя передачу информации с блока 7 через блок 32 управления транзитом, элемент 13 задержки и третьи входы выходных блоков 8-11 коммутации, если в регистр 3 команд записан адрес выхода транзита с задержкой на один такт, или после второго элемента 13 задержки на второй вход блока 33 расширенного транзита с ее выхода на элемент 14 задержки и с его выхода на вторые входы выходных блоков 811 коммутации, если в регистр 3 команд записан адрес выхода транзита с задержкой на два такта.

При выполнении ячейкой операции Расширенный -транзит сигнал с вы- ходов 35 дешифратора 4 включает две дополнительные цепи транзита. В первой дополнительной цепи транзита информация принимается с входного блока 5 коммутации на вход первого арифметико-логического блока 1, поступает на его выход и через элемент 2 задержки, элемент 30 задержки и блок 31 управления дополнительной задержкой результата арифметико-логи- ческого блока вьщается на первые входы выходных блоков 8-11 коммутации. Во второй дополнительной цепи транзита информация принимается с второго входного блока 6 коммутации на вход блока 33 расширенного транзита и с ее выхода поступает на вход элемента 14 задержки, с выхода которого вьщается на вторые входы выходных блоков 8-11 коммутации. По при- знаку задержки, равному О или 1 подаваемому с выхода 24 регистра команд на управляющий вход блока 31 управления дополнительной задержкой результата, в первой дополнительной цепи транзита производится выход транзита с задержкой на один или два такта.

При вьшолнении модулем операции Расширенный транзит цепь транзита модуля работает автономно от двух дополнительных цепей транзита и вьщача информации модулем по этой цепи осуществляется только с задержкой на один такт (вход блока 32 Управления транзитом, элемент 13 задержки и третьи входы блоков 8-11).

При выполнении ячейкой операции Генератор констант сигнал с выходов 35 дешифратора 4 включает цепь закольцовки части регистра 29 и отключает операционную цепь модуля от входных блоков 5 и 6 коммутации, сигнал признака задержки с выхода 24 регистра команд, равный О, отклю- чает из цепи закольцовки блок 12 и включает цепь транзита от входного блока 7 коммутации. Константа с выхода регистра команд через блок 12 по цепи закольцовки циркулирует в разрядах регистра 29 команд и одновременно последовательно через равны интервалы времени, определяемые длиной слова константы, поступает с выхода блока 12 на вход блока 32 управления транзитом, передается по цепи транзита и выдается на вторые входы блоков 8-11.

При вьшолнении модулем операции Генератор макроконстант на вход блока 12 поступает сигнал признака задержки с первого выхода 24 регистра команд, равный 1, которьй подключает вход блока 12 к информацио- ному входу 15 модуля,.размыкает цеп закольцовки регистра 29. Информация с информационного входа 15 модуля поступает на вход блока 12, ас первого его выхода поступает в разряды регистра 3 команд, через равные интервалы времени подается с его выхода на вход блока 12 и через второй его выход на вход блока 32 управления транзитом передается по цепи транзита и вьщается на вторые входы блоков 8-11.

Наличие блока формирования константы и блока управления транзитом обеспечивает возможность реализации генерации ма.кроконстант длиной более В бит.

Наличие блока управления дополнительной задержкой арифметико-логического блока и четвертого элемента задержки позволяет реализовать программно-управляющую дополнительную задержку результата в операционной цепи, что дает возможность сэкономить количество модулей при организации вычислительной структуры.

Блок расширенного транзита позволяет реализовать в модуле дополнительную независимую от других транспортную цепь, что увеличивает гибкость реализации алгоритмов на вычислительной структуре. Данный модуль однородной вычислительной структуры позволяет повысить производительность структуры в 1,3 раза при решении задач обработки изображений пороговым методом, методом гистограм и методом вьщеления контуров в системе, а также сократить количество используемых в структуре модулей до 30% по сравнению с использованием устройства-прототипа.

Формула изобретения

Модуль однородной вычислительной структуры, содержащий арифметико-логический блок последовательного типа, регистр команд, сдвиговьш регистр команд, дешифратор, первьй, второй и третий элементы задержки, первый, второй, третий, четвертый выходные блоки коммутации, входы дешифратора подключены к выходам поля кода операции регистра команд, первые информационные входы с первого по четвертый входных блоков коммутации подключены к первому информационному входу модуля, вторые информационные входы с первого по четвертый входных блоков KOMMyTaqtni подключены к второму информационному входу модуля, третьи информационные входы с первого по четвертый входньк блоков коммутации подключены к третьему информационному входу модуля, четвертые информацион- ,ные входы с первого по четвертый входных блоков коммутации подключены к четвертому информационному входу модуля, выходы с первого по четвертый выходных блоков коммутации подключены соответственно к выходам с первого по четвертый результата модуля, вход записи команды в модуль подключен к входу записи регистра команд и к входу записи сдвигового регистра команд, вход синхронизации модуля подключен к синхровходу регистра ко- манд и к синхровходу сдвигового регистра команд, вход первого элемента задержки подключен к выходу арифметико-логического блока-последовательного типа, первая группа выходов дешифратора подключена к входам кода операции арифметико-логического блок

последовательного типа, первый и вто- Q станты подключен к первому информарой входы операндбв которого подключены соответственно к выходам первого и второго входных блоков коммутации, управляющ11е входы которых под- ютючены соответственно к первым и вторым группам выходов поля адреса сдвигового регистра команд, выход второго элемента задержки подключен к третьим информационным, входам с первого по четвертый выходных блоков коммутации, выход третьего элемента задержки подключен к вторым информационным входам с первого по четвертый выходных блоков коммутации, -первые управляющие входы с первого по четвертый выходных блоков коммутации подключены соответственно к группам выходов с первой по четвертую поля входного адреса сдвигового регистра

ционному входу блока управления тран зитом, управляющий вьпсод блока формирования константы подключен к вхо- ;ДУ установки в 1 поля признака

45

50

55

задержки регистра команд, выход третьего входного блока коммутации подключен к второму информационному входу блока управления транзитом, вы ход которого подключен к входу втог- рого элемента задержки, выход второго входного блока коммутации подключен к первому информа тионному входу блока расширенного транзита, второй информацнонйый вход которого подключен к выходу второго элемента задерж ки, выход блока расширенного.транзита подключен к входу третьего элемента задержки,, выход первого эле- мента задержки, подклюгсен к входу

5

0

5

0

5

команд, вторые управляющие, входы с .первого по четвертый выходных блоков коммутации подключены соответственно к группам выходов с третьей по шестую поля выходного адреса сдвигового регистра команд, управляющий вход третьего входного блока коммутации под- ключен к пятой группе выходов поля входного адреса сдвигового регистра команды, о.тлич ающийся тем, что, с целью повышения быстродействия, в него введены блок формирования константы, четвертьй элемент задержки, блок управления дополнительной задержкой, блок управления транзитом, блок расширенного транзита, первая группа выходов поля задержки регистра команд подключена к первому управляющему входу блока формирования константы, вторая группа выходов поля признака задержки pef. гистра команд подключена к управляющему входу блока управления дополнительной задержкой, первьм информационный вход блока формирования константы подключен к первому информационному входу модуля, второй информационный вход блока формирования константы подключен к выходу переноса последнего разряда сдвигающего регистра , второй управляющий вход блока формирования константы, управляющий вход блока управления транзитом, управпяюЕцун вход блока расширения транзита подключены соответственно к группам выходов с второй по четвертую дешифратора, информационный выход блока формирования койстанты подключен к первому информационному входу блока управления транзитом, управляющий вьпсод блока формирования константы подключен к вхо- ;ДУ установки в 1 поля признака

задержки регистра команд, выход третьего входного блока коммутации подключен к второму информационному входу блока управления транзитом, вы-, ход которого подключен к входу втог- рого элемента задержки, выход второго входного блока коммутации подключен к первому информа тионному входу блока расширенного транзита, второй информацнонйый вход которого подключен к выходу второго элемента задержки, выход блока расширенного.транзита подключен к входу третьего элемента задержки,, выход первого эле- мента задержки, подклюгсен к входу

7

четвертого элемента задержки и к первому информационному входу блока управления дополнительной задержкой, второй информационный вход которого подключен к выходу четвертого элемента задержки, выход блока управления дополнительной задержкой подключен к первым информационным входам с первого по четвертый выходных блоков ком гутации, при этом блок формирования константы содержит два узла элементов И, два узла элементов ШТИ, три узла элементов НЕ, первый управляющий вход блока формирования констант подключен к входу первого узла элемента НЕ блока формирования константы и к первому входу первого узла элементов ИЛИ блока формирования константы, второй управляющий вход блока формирования константы подключен к второму входу первого узла элементов ИЛИ блока формирования константы и к входу второго узла элементов НЕ блока формирования константы, первый информационный вход блока формирования константы подключен к первому входу первого узла элементов ИЛИ блока формирования константы.

35

второй информационный вход блока фор- зо Узла элементов ИЛИ блока расширенного мирования константы подключен к третьему входу первого узла элементов И блока формирования копстанты, выход первого узла элементов ЮТИ блока фор- мирования константы подключен к первому входу второго узла элементов И блока формирования константы, второй вход которого подключен к выходу первого узла элементов НЕ блока формирования константы, выход второго 040 узла элементов НЕ блока формирования константы подключен к второму входу первого узла элементов ИЛИ блока формирования константы, выход первого узла элементов И блока формирова- в ния константы подключен к первому входу второго узла элементов ИЛИ блока формирования константы, второй вход которого подключен к выходу второго узла элементов И, инверсный выход второго узла элементов ИЛИ блока формирования константы подключен к информационному выходу блока формирования константы и к входу третьего узла элементов НЕ .блока формирования константы, выход которого подключен к управляющему выходу блока формирования константы, при этом блок управления транзитом содержит два уз50

55

транзита, первый вход блока pacnni- ренного транзита подключен к первому входу второго узла элементов ИПИ блока расширенного транзита, второй вход которого подключен к выходу узла элементов НЕ блока расширенного транзита, второй вход блока, pactm-i- ренного транзита подключен к второму входу первого узла элементов ИПИ блока расширенного транзита, инверсные выходы первого и. второго узлов элементов ИЛИ блока расширенного транзита подключены соответственно к первому и втором входам элемента ИЛИ блока расширенного транзита, инверсный выход которого подключен к выходу блока расширенного транзита, при этом блок управления дополнительной задержкой содержит два узла элементов И, узел элементов НЕ, элемент ИЛИ, управляющий вход блока управления дополнительной задержкой подключен к первому входу первого узла элементов И блока управления дополнительной задержкой и к входу узла элементов НЕ блока управления дополнительной задержкой, первый вход блока управления дополнительной задержкой подключен к второму входу

10

2559782«

ла элементов И, элемент HJHi и узел элементов НЕ, управляющий вход блока управления транзитом подключен к входу узла элементов НЕ блока управления транзитом и к первому входу первого узла элементов И блока управления транзитом, второй вход которого подключен к первому информационному входу блока управления транзитом, вторые информационные входы блока управления транзитом подключены к первому входу второго узла элементов И блока управления транзитом, второй вход которого подключен к выходу узла элементов НЕ блока управления транзитом, выходы первого и второго блоков элементов И блока управления транзитом подключены соответственно к первому и второму входам элемента 1ШИ блока управления транзитом, выход которого подключен к выходу блока управления транзитом, при этом блок расширенного транзита содержит два узла элементов ИЛИ, узел элементов НЕ, элемент ИЛИ, управляющий вход блока расширенного транзита-подключен к входу узла элементов НЕ блока распшренного транзита и к первом, входу первого

15

20

5

о Узла элементов ИЛИ блока расширенного 0 в

0

5

транзита, первый вход блока pacnni- ренного транзита подключен к первому входу второго узла элементов ИПИ блока расширенного транзита, второй вход которого подключен к выходу узла элементов НЕ блока расширенного транзита, второй вход блока, pactm-i- ренного транзита подключен к второму входу первого узла элементов ИПИ блока расширенного транзита, инверсные выходы первого и. второго узлов элементов ИЛИ блока расширенного транзита подключены соответственно к первому и втором входам элемента ИЛИ блока расширенного транзита, инверсный выход которого подключен к выходу блока расширенного транзита, при этом блок управления дополнительной задержкой содержит два узла элементов И, узел элементов НЕ, элемент ИЛИ, управляющий вход блока управления дополнительной задержкой подключен к первому входу первого узла элементов И блока управления дополнительной задержкой и к входу узла элементов НЕ блока управления дополнительной задержкой, первый вход блока управления дополнительной задержкой подключен к второму входу

первого узла элементов И блока управления дополнительной задержкой, второй вход блока управления дополнительной задержкой подключен к первому входу второго узла элементов И блока управления дополнительной задержкой, выход узла элементов НЕ блока управления дополнительной задержкой подключен к второму входу второго узла элементов И блока уп

равления дополнительной задержкой, выходы первого и второго узлов элементов И блока управления дополнительной задержкой подключены соответственно к первому и второму входам элемента ИЛИ блока управления дополнительной задержкой, выход «оторого подключен к выходу блока управления дополнительной за держкой.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Ячейка однородной вычислительной среды | 1987 |

|

SU1594519A1 |

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Векторно-потоковое операционное устройство | 1989 |

|

SU1734100A1 |

| Процессор | 1977 |

|

SU691858A1 |

Изобретение относится к вычислительной технике и предназначено для использования в качестве модуля одно28 родной вычислительной структ фы, ориентированной на цифровую обработ- ку сигналов. Цель изобретения - ловы- шение быстродействия устройства. Указанная дель достигается тем, что в устройство, содержащее арифметико-логический блок 1 последовательного типа, регистр 3 команд, сдвиговый регистр 29 команд, дешифратор 4, три элемента задержки 2,13 и 14, четьфе выходных блока 8-11 коммутации, три входных блока 5-7 коммутации, введены блок 12 формирования константы, чет- вертьш элемент задержки 30, блок 31 управления дополнительной задержкой, блок 32 управления транзитом и блок 33 расширения транзита с соответствующими связями. 5 ил. , . п S 16 -4 3 if СО СП ;О 00 ГчЭ 20

«4

о J/ 3

Физ.г

фие.З

фие.4

в 11

Редактор М, Андрушенко

фие5

Составитель В. Смирнов

Техред М.Ходанич Корректор Л. Пилипенко

Заказ 6154750 Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| Авторское свидетельство СССР № 684986, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-15—Публикация

1984-09-11—Подача