Изобретение относится к импульсной технике и может быть использовано пр.и построении микросхем ЭСЛ-типа

Целью изобретения является повыше- ние быстродействия.

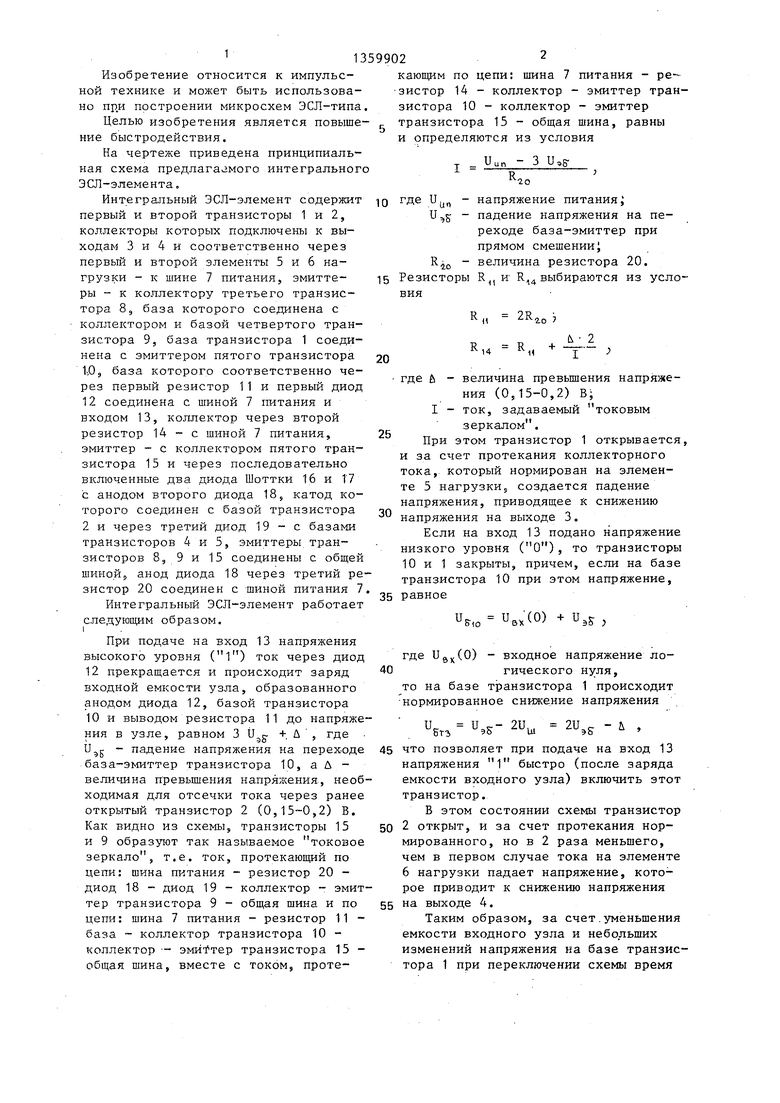

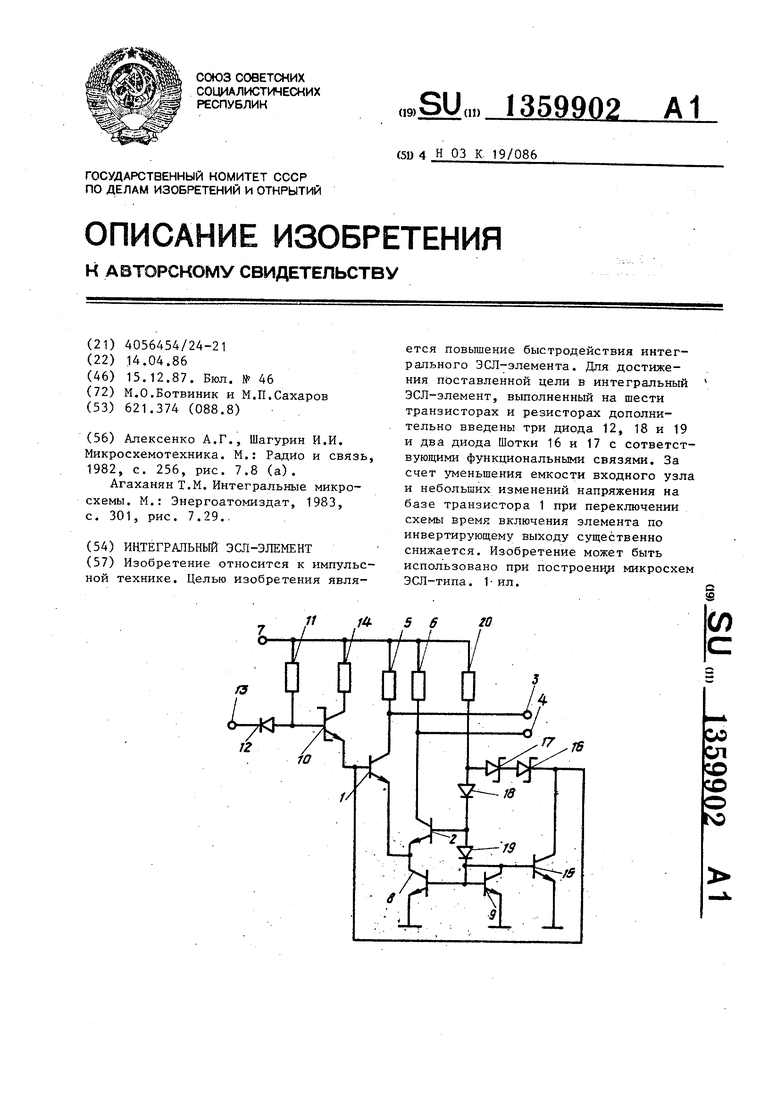

На чертеже приведена принципиальная схема предлага змого интегрального ЭСЛ-элемента.

Интегральный ЭСЛ-элемент содержит первый и второй транзисторы 1 и 2, коллекторы которых подключены к выходам 3 и 4 и соответственно через первый и второй элементы 5 и 6 нагрузки - к шине 7 питания, эмитте- ры - к коллектору третьего транзистора 8, база которого соединена с коллектором и базой четвертого транзистора 9, база транзистора 1 соединена с эмиттером пятого транзистора liO, база которого соответственно через первый резистор 11 и первый диод 12 соединена с шиной 7 питания и входом 13, коллектор через второй резистор 14 - с шиной 7 питания, эмиттер - с коллектором пятого транзистора 15 и через последовательно включенные два диода Шоттки 16 и 17 с анодом второго диода IS, катод которого соединен с базой транзистора 2 и через третий диод 19 - с базами транзисторов 4 и 5, эмиттеры транзисторов 8, 9 и 15 соединены с общей шинойJ анод диода 18 через третий резистор 20 соединен с шиной питания 7

Интегральный ЭСЛ-элемент работает

следующим образом.

I

При подаче на вход 13 напряжения высокого уровня (1) ток через диод 12 прекращается и происходит заряд входной емкости узла, образованного анодом диода 12, базой транзистора 10 и выводом резистора 11 до напряжения в узле, равном 3 . +. U , где - падение напряжения на перех-оде база-эмиттер транзистора 10, а Д - величина превьш1ения напряжения, необходимая для отсечки тока через ранее открытый транзистор 2 (0,15-0,2) В. Как видно из схемь, транзисторы 15 и 9 образуют так назы.ваемое токовое зеркало, т.е. ток, протекающий по цепи; шина питания - резистор 20 - диод 18 - диод 19 - коллектор - эмиттер транзистора 9 - общая шина и по цепи: шина 7 питания - резистор 11 - база коллектор транзистора 10 - коллектор - эмиттер транзистора 15 - общая шина, вместе с током, проте

кающим по цепи: шина 7 питания - ре- зистор 14 - коллектор - эмиттер транзистора 10 - коллектор - эмиттер транзистора 15 - общая шина, равны и определяются из условия

т - Uun - 3 U,g

J- 5

10

и,„

и,

чо

-напряжение питания

-падение напряжения на переходе база-эмиттер при прямом смешенииJ

-величина резистора 20.

Резисторы R,, и R, выбираются из условия

2R

2.0

н

R.

2

;

где U - величина превьш1ения напряжения (0,15-0,2) В;

I - ток, задаваемый

зеркалом. При этом транзистор 1

токовым

открывается,

и за счет протекания коллекторного тока, который нормирован на элементе 5 нагрузки, создается падение напряжения, приводящее к снижению напряжения на выходе 3.

Если на вход 13 подано напряжение низкого уровня (О), то транзисторы 10 и 1 закрыты, причем, если на базе транзистора 10 при этом напряжение, равное

и,о и.х(О)

+ и

э5- )

где Ug(O) - входное напряжение логического нуля,

то на базе транзистора 1 происходит нормированное снижение напряжения

.-2иц.

2U

э&

- Ь

что позволяет при подаче на вход 13 напряжения 1 быстро (после заряда емкости входного узла) включить этот транзистор.

В этом состоянии схемы транзистор 2 открыт, и за счет протекания нормированного, но в 2 раза меньшего, чем в первом случае тока на элементе 6 нагрузки падает напряжение, которое приводит к снижению напряжения на выходе 4.

Таким образом, за счет.уменьшения емкости входного узла и небольших изменений напряжения на базе транзистора 1 при переключении схемы время

включения элемента по инвертирующему выходу существенно снижается.

Фор м у ла изобрете н.и я

Интегральный ЭСЛ-элемент, содержащий шесть транзисторов, три резистора, коллекторы первого и второго транзисторов подключены к выходам и соответственно через первый и второй элементы нагрузки - к шине питания, эмиттеры соединены с коллектором третьего транзистора, база которого соединена с коллектором и базой четвертого, транзистора, база первого транзистора соединена с эмиттером пятого транзистора, первый вывод первого резистора соединен с шиной питания, отличающийся тем, что, с целью повышения быстродейстРедактор Т.Парфенова

Составитель А.Янов Техред И.Попович

3aifa3 6164/56 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и о гкрытий 113035, Москва, Ж-35, Раушская наб., д; 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0

5

0

ВИЯ, введены три диода и два диода Шоттки, второй вывод первого резистора соединен с базой пятого транзистора и через первый диод - с входом, коллектор пятого транзистора через второй резистор соединен с шиной питания, эмиттер - с коллектором шестого транзистора и через два последовательно соединенных диода Шоттки подключен к аноду второго диода, катод которого соединен с базой второго транзистора и анодом третьего диода, катод которого соединен с ба- зами- ,четвертого и шестого транзисторов, эмиттеры которых соединены с общей шиной и эмиттером третьего транзистора, анод второго диода через третий резистор соединен с шиной питания.

Корректор М .Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Схема согласования уровней ТТЛ-ЭСЛ | 1985 |

|

SU1309301A1 |

| Интегральный ЭСЛ-элемент | 1988 |

|

SU1531209A1 |

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Эмиттерно-связанный элемент | 1988 |

|

SU1629985A1 |

| Логический элемент "Исключающее ИЛИ" | 2022 |

|

RU2792407C1 |

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» | 2022 |

|

RU2795286C1 |

| Мажоритарный элемент | 1986 |

|

SU1378049A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

Изобретение относится к импульсной технике. Целью изобретения является повышение быстродействия интегрального ЭСЛ-элемента. Для достижения поставленной цели в интегральный ЭСЛ-элемент, выполненный на шести транзисторах и резисторах дополнительно введены три диода 12, 18 и 19 и два диода Шотки 16 и 17 с сответст- вующими функциональными связями. За счет уменьшения емкости входного узла и небольших изменений напряжения на базе транзистора 1 при переключении схемы время включения злемента по инвертирующему выходу существенно снижается. Изобретение может быть использовано при построенц микросхем ЭСЛ-типа. 1- ил. f2 5 б I - / га со

| Алексенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с | |||

| Ножевой прибор к валичной кардочесальной машине | 1923 |

|

SU256A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Агаханян Т.Н | |||

| Интегральные микросхемы | |||

| М.: Энергоатомиздат, 1983, с | |||

| Прибор для исправления снимков рельефа местности | 1921 |

|

SU301A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1987-12-15—Публикация

1986-04-14—Подача