со sj

00

о 4 со

Изобретение относится к импульсной технике, а точнее к комбинационньв 1 логическим схемам на биполярных транзисторах.

Целью изобретения является повышение быстродействия и снижение потребляемой мощности.

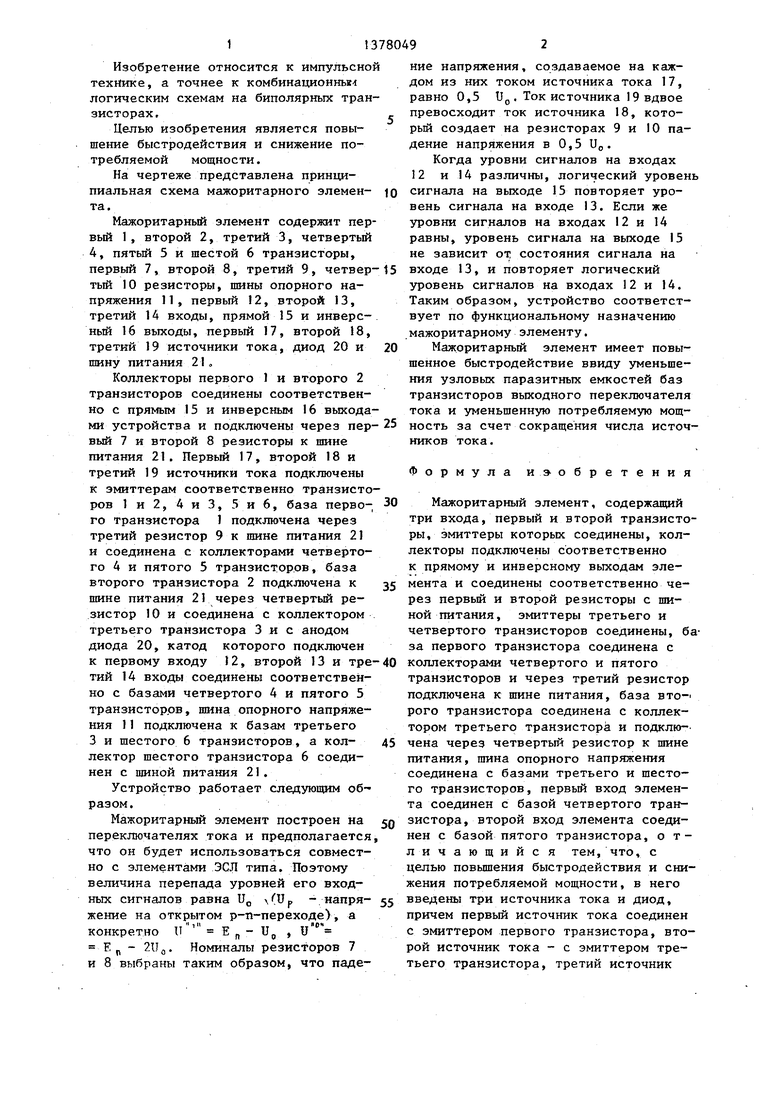

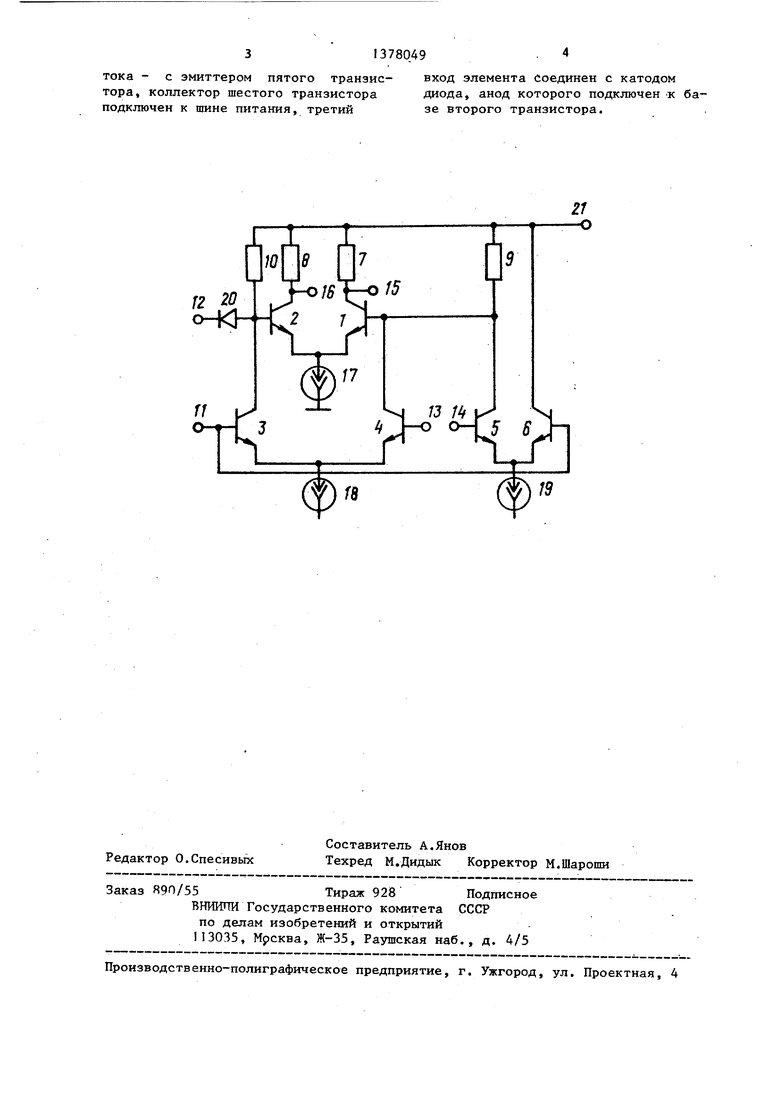

На чертеже представлена принципиальная схема мажоритарного элемента.

Мажоритарный злемент содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5 и шестой 6 транзисторы.

ние напряжения, создаваемое на каждом из них током источника тока 17, равно 0,5 Up. Ток источника 19 вдвое превосходит ток источника 18, который создает на резисторах 9 и 10 падение напряжения в 0,5 U.

Когда уровни сигналов на входах 12 и 14 различны, логический уровень сигнала на выходе 15 повторяет уровень сигнала на входе 13. Если же уровни сигналов на входах 12 и 14 равны, уровень сигнала на выходе 15 не зависит от состояния сигнала на

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1377917A1 |

| Стабилизированный логический элемент | 1977 |

|

SU683024A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Логический элемент | 1985 |

|

SU1275758A1 |

| Устройство реверсирования тока | 1979 |

|

SU788380A1 |

| Преобразователь уровня сигналов | 1981 |

|

SU1011025A1 |

Изобретение относится к комбинационным логическим схемам на биполярных транзисторах. Цель изобретения - повьппение быстродействия и снижение потребляемой мощности. Электрическая схема мажоритарного элемента построена на биполярных транзисторах. Переключатель тока второго информационного входа используется для инвертирования входного сигнала, благодаря , чему на базы транзисторов выходного переключателя тока один из сигналов поступает в инверсной форме. Использование мажоритарного элемента, построенного на переключателях тока и работающего с однофазными входными сигналами, отсутствие переключателя тока для одного из информационных входов позволяет достичь указанной выше цели. 1 йл. i (Л

первый 7, второй 8, третий 9, четвер-15 входе 13, и повторяет логический

тый 10 резисторы, шины опорного напряжения 11, первый I2, второй 13, третий 14 входы, прямой 15 и инверс- нь1й 16 выходы, первый 17, второй 18, третий 19 источники тока, диод 20 и шину питания 21

Коллекторы первого 1 и второго 2 транзисторов соединены соответственно с прямым 15 и инверсным 16 выходами устройства и подключены через пер- вый 7 и второй 8 резисторы к шине питания 21. Первый 17, второй 18 и третий 19 источники тока подключены к эмиттерам соответственно транзисторов 1 и 2, 4 и 3, 5 и 6, база перво-, го транзистора 1 подключена через третий резистор 9 к шине питания 21 и соединена с коллекторами четвертого 4 и пятого 5 транзисторов, база второго транзистора 2 подключена к шине питания 21 через четвертый резистор 10 и соединена с коллектором третьего транзистора 3 и с анодом диода 20, катод которого подключен

к первому входу 12, второй 13 и тре-40 коллекторами четвертого и пятого

тий 14 входы соединены соответственно с базами четвертого 4 и пятого 5 транзисторов, шина опорного напряжения 11 подключена к базам третьего 3 и шестого 6 транзисторов, а кол- лектор шестого транзистора 6 соединен с шиной питания 21.

Устройство работает следующим образом.

Мажоритарный элемент построен на переключателях тока и предполагается что он будет использоваться совместно с элементами ЭСЛ типа. Поэтому величина перепада уровней его входных сигналов равна U (Up - напря- жение на открытом р-п-переходе), а конкретно и Е „ - Up , Е р - 211 о. Номиналы резисторов 7 и 8 выбраны таким образом, что паде0

5 0

5

уровень сигналов на входах 12 и 14. Таким образом, устройство соответствует по функциональному назначению мажоритарному элементу.

Мажоритарный элемент имеет повышенное быстродействие ввиду уменьшения узловых паразитных емкостей баз транзисторов выходного переключателя тока и уменьшенную потребляемую мощность за счет сокращения числа источников тока.

Формула изобретения

Мажоритарный элемент, содержащий три входа, первый и второй транзисторы, эмиттеры которых соединены, коллекторы подключены соответственно к прямому и инверсному выходам элемента и соединены соответственно через первьй и второй резисторы с шиной питания, эмиттеры третьего и четвертого транзисторов соединены, база первого транзистора соединена с

транзисторов и через третий резистор подключена к шине питания, база вто- рого транзистора соединена с коллектором третьего транзистора и подклю- чена через четвертьпЧ резистор к шине питания, шина опорного напряжения соединена с базами третьего и шестого транзисторов, первый вход элемента соединен с базой четвертого транзистора, второй вход элемента соединен с базой пятого транзистора, отличающийся тем, что, с целью повышения быстродействия и снижения потребляемой мощности, в него введены три источника тока и диод, причем первый источник тока соединен с эмиттером первого транзистора, второй источник тока - с эмиттером третьего транзистора, третий источник

тока - с эмиттером пятого транзистора, коллектор шестого транзистора подключен к шине питания, третий

вход элемента соединен с катодом диода, анод которого подключен к базе второго транзистора.

73 7 1 XI

гЧл

75

| Мкртчян С.О | |||

| Проектирование логических устройств ЭВМ на нейтронных элементах | |||

| М.: Энергия, 1977, с.132, рис,5-1 | |||

| Будинский Я | |||

| Логические цепи в цифровой технике | |||

| М.: Связь, 1977, с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

Авторы

Даты

1988-02-28—Публикация

1986-10-15—Подача