1Изобретение относится к автоматике и вычислительной технике и может быть использовано для тестового контроля работоспособности релейных систем, например систем управления температурно-влажностным режимом в производственных помещениях.

Целью изобретения является повышение быстродействия устройства путем обеспечения адаптации к длительности отработки релейной системой тестовых команд.

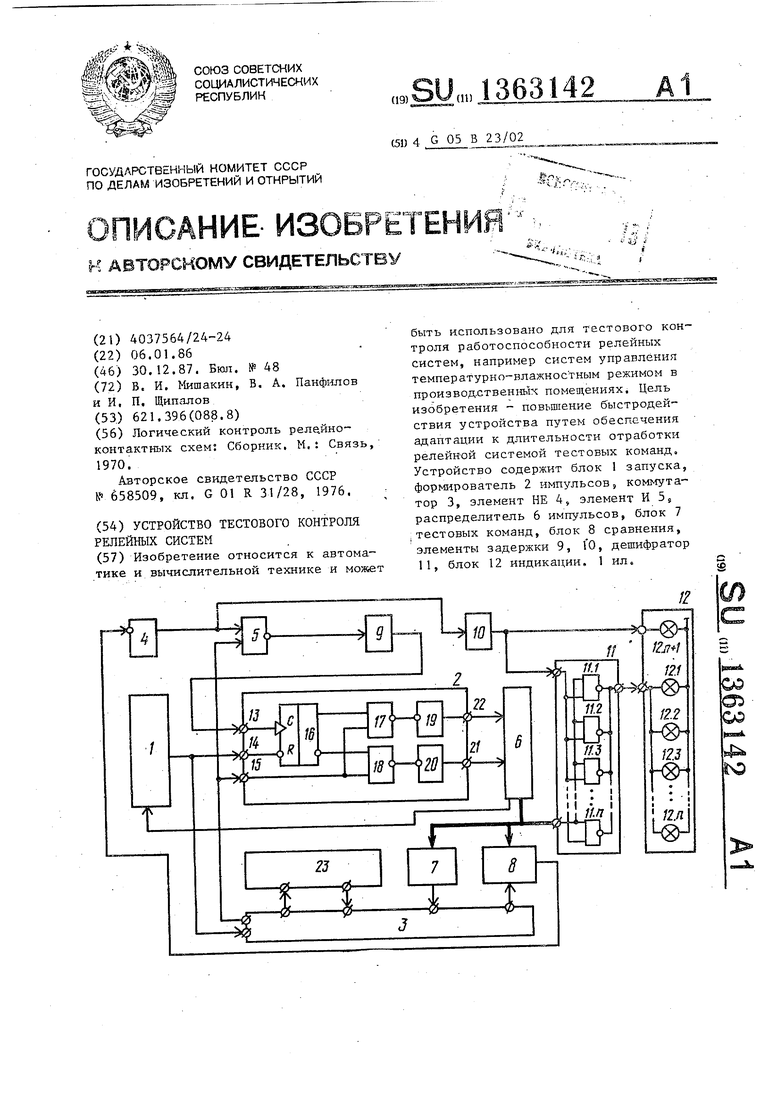

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит блок I запуска, формирователь 2 импульсов, коммутатор 3, элемент НЕ 4, элемент И 5, распределитель 6 импульсов, блок 7 тестовых команд, блок 8 сравнения, второй элемент 9 задержки, первый элемент 10 задержки, дешифратор 11, выполненный на элементах И 11.1-I1.п по числу тактов контроля блок 12 индикации, включающий элементы индикации 12,1-12.П+1, формирователь 2 импульсов, имеющий счетный установочный и стробирующий входы 1 14 и 15 соответственно и содержащий счетный триггер 16, элементы И 17 и 18, элементы НЕ 19 и 20 и первый и

второй выходы 21 и 22.

Контролируемая линейная система 23 подключена входом и выходюм к третьим выходам и вторым инфор аци- онным входам коммутатора 3.

Распределитель 6 импульсов выполнен с двумя тактовыми шинами, подключенными соответственно к выходам 21 и 22 формироват еля 2 импульсов.

Выходы распределителя 6 образуются нормально открытыми контактами тактвых реле (не показаны).

Устройство работает следующим образом.

Режим тестового контроля работоспособности релейной системы 23 управления вводится блоком 1 запуска выходной сигнал которого поступает на установочный вход 14 формирователя 2 импульсов и устанавливает по R-входу счетный триггер 16 в исходное положение, в результате чего на первый вход элемента И 18.подается единичный сигнал. Одновременно выходной сигнал блока 1 запуска посту пает на управляющий вход коммутатор 3, который по этой команде отключа

5

0

5

0

5

0

5

0

5

ет систему 23 от объекта управления (не показан) и подкггючает ее входы к выходу блока 7 тестовых команд, а ее выход - к входу блока 8 сравнения. Такое переключение осуществляется через первый и второй информационные входы и первый и третий выходы коммутатора 3. Сигнал обратной связи с донесением о переьслючении системы 23 в режим тестового контроля поступает с второго выхода коммутатора 3 через стробирующий вход 15 формирователя 2 импульсов на вторые входы .элементов И 17 и 18 и на первый вход элемента И 5. В результате на выходе элемента И 18 образуется нулевой сигнал, который через элемент НЕ 20 поступает в виде единичного сигнала на выход 21 и далее на первую тактовую шину распределителя 6. Распределитель 6 формирует выходной сигнал первого такта контроля для блока 7, который в соответствии с заданной программой тестового контроля вводит в систему 23 первую тестовую команду. На выходе блока 8 сравнения в это время присутствует единичный сигнал Неравнозначность, который через элемент НЕ 4 запускает в работу первый элемент 10 задержки. Величина максимальной выдержки времени элемента 10 выбирается заведомо большей наибольшего по длительности такта тестового контроля .

Система 23, реагируя в соответствии с заданным алгоритмом управления на поступающую из блока 7

тестовую команду, формирует на своем выходе сигналы управляющих воздействий, которые через втррой инФор мационный вход и первый выход коммутатора 3 поступают в блок 8 сравнения. При совпадении этих сигналов с сигналами, запрограммированными для этого такта контроля, блок 8 формирует нулевой сигнал Равнозначность, который через элемент НЕ 4 поступает- в виде единичного сигнала на вход элемента И 5. Поскольку на обоих входах элемента И 5 присутствуют единичные сигналы, то на его выходе формируется нулевой сигнал, который запускает второй элемент-9 задержки. После срабатывания элемента 9 задержки его выходной сигнал поступает на счетный вход 13 формирователя 2, что приводит к переходу триггера 16

в противоположное состояние и иэме- неиню на противоположные значения его выходных сигналов. В результате изменяются на противоположные значения выходные сигналы элементов И 17 и 18, элементов НЕ 19 и 20 и формирователя 2, на выходе 22 которого появляется единичный сигнал, а на выходе 21 - нулевой. Это вызывает формирование сигнала второго такта контроля распределителем 6 для блока 7 тестовых команд, который вводит новую команду в систему 23. Величина минимальной выдержки времени второго элемента 9 должна перекрывать временной интервал, в течение которого переключаются все логические элементы контролируемой системы 23 после снятия с ее выходов блоком & сигналов, формирующих итоговый сигнал Равнозначность, т.е. минимальная выдержки времени должна быть больше времени переходного процесса переключения логических элементов, который имеет место по окончании отработки предыдущей тестовой команды перед вводом последующей. В противном случае ввод новой тестовой, команды может наложиться во времени с переходным состоянием логических элементов и результат контрол будет ложным.

После отработки второй тестовой команды вводится третья и так далее По окончании тестового контроля, т.е после отработки последней тестовой команды п, распределитель 6 формирует служебный (п+1)-й такт, воздействующий на блок 1 запуска, который через коммутатор 3 выводит систему 23 из режима тестового контроля, подключая ее входы и выходы к объекту управления.

Если время отработки какой-либо тестовой команды превысит максимальную вьвдержку времени, то в этом случае сработает первый элемент 10 задержки, выходной сигнал которого по первому входу блока 12 зажигает общий транспарант Неисправность. Одновременно выходной сигнал элемента 10 через первый вход дешифратора 11 воздействует на первые входы элементов 11,1 и 11,п, на вторые входы которых воздействует сигнал теВНИИПИ

Заказ 6361/37 Тираж 863

. Произв-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

кущего такта тестового контроля. Это приводит к срабат1)Шанию соответству- юп1его этому такту элемента И, выходной сигнал которого с вторых выходов дешифратора 11 поступает на соответствующий второй вход блока 1.2 индикации и зажигает один из элементов индикации 12,,...12.п индикации этого блока, соответствующий номеру тестовой команды; по которой получена неисправность.

Формула изобретения

0

5

0

5

0

0

5

Устройство тестового контроля релейных систем, содержащее распределитель импульсов, подключенный первыми выходами к входам блока тестовых команд, блок сравнения, блок запуска, первый элемент задержки, блок индикации, от личающе- е с я тем, что, .с целью повьшения быстродействия, в него введены дешифратор, коммутатор, формирователь импульсов, элемент И, второй элемент задержки и элемент НЕ, подключенный входом к выходу блока сравнения, а выходом - к первому входу элемента И и через первый элемент задержки к первым входам блока индикации дешифратора, связанного выходами с соответствующими вторыми входами блока индикации, а вторыми входами - с первыми выходами распределителя импульсов и первыми входами блока сравнения, подключенного вторыми входами к первым выходам коммутатора, соединенного первыми информационными входами с выходами блока тестовых команд, управляющим входом - с выходом .блока запуска .и установочным входом формирователя импульсов, а вторым ВЫХОДОМ - со стробирукяцим g входом формирователя импульсов и

вторым входом элемента И, подключенного выходом через второй элемент задержки к счетному входу формирователя импульсов, связанного первыми и вторым выходами с первым и вторым тактовыми входами распределителя импульсов, связанного вторым выходом с входом блока запуска, третьи выходы и вторые информационные входы коммутатора являются контрольными входами и выходами устройства.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для ввода информации | 1988 |

|

SU1539763A1 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для тестовой проверки узлов контроля каналов ввода-вывода | 1979 |

|

SU922752A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

Изобретение относится к автоматике и вычислительной технике и мозкет быть нспользовано для тестового контроля работоспособности релейных систем, например систем управления температурно-влажнос тным режимом в производственных помещениях. Цель изобретения - повьшгение быстродействия устройства путем обеспечения адаптации к длительности отработки релейной системой тестовых команд. Устройство содержит блок 1 запуска, формирователь 2 импульсов, коммутатор 3, элемент НЕ 4, элемент И 5 распределитель 6 импульсов, блок 7 .тестовых команд, блок 8 сравнения, элементы задержки 9, , дешифратор 11, блок 12 индикации, 1 ил. sg

| Логический контроль контактных схем; Сборник, М.: Связь, 1970 | |||

| Устройство для контроля логических блоков | 1976 |

|

SU658509A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ; | |||

Авторы

Даты

1987-12-30—Публикация

1986-01-06—Подача